PDF issue: 2025-12-05

# Influence of elastic and inelastic phonon scattering on the drive current of quasi-ballistic MOSFETs

Tsuchiya, Hideaki Takagi, Shin-ichi

#### (Citation)

IEEE Transactions on Electron Devices, 55(9):2397-2402

(Issue Date)

2008-09

(Resource Type)

journal article

(Version)

Version of Record

(URL)

https://hdl.handle.net/20.500.14094/90000911

## Influence of Elastic and Inelastic Phonon Scattering on the Drive Current of Quasi-Ballistic MOSFETs

Hideaki Tsuchiya, Senior Member, IEEE, and Shin-ichi Takagi, Member, IEEE

Abstract—In this paper, we study the influence of elastic and inelastic phonon scattering on the drive current of Si MOSFETs under quasi-ballistic transport. Inelastic phonon emission involving energy relaxation helps achieve ballistic current, even in the presence of scattering, if the channel length is scaled down to the 10-nm scale. This result agrees with Natori's previous predictions. However, for longer channel devices, inelastic phonon emission degrades the drain current due to space charge effects caused by charge accumulation. We also demonstrate that source-end potential engineering to electrically reduce the bottleneck barrier length can result in a ballistic current even in longer channel devices.

Index Terms—Backscattering, elastic and inelastic scattering, nanoscale MOSFETs, quantum-corrected Monte Carlo simulation, quasi-ballistic transport, source-end velocity.

#### I. INTRODUCTION

WING TO significant advances in lithography technology, the channel length of Si MOSFETs has been scaled down to the sub-10-nm regime [1]. Because the frequency of carrier scattering is diminished in such ultrashort devices, carrier transport becomes ballistic [2]–[5], and a drive current enhancement is expected [6], [7]. In this paper, we study the influence of phonon scattering on the drive current of MOSFETs under quasi-ballistic transport. The electrical characteristics are computed using a quantum-corrected Monte Carlo simulation [7]–[9].

First, we study the roles of elastic and inelastic phonon scattering on the drive current. In quasi-ballistic transport, the channel current is degraded from the ideal ballistic limit due to backscattering processes toward the source electrode. According to Natori [2], [10]–[12], only carriers backscattered by the elastic process can return to the source electrode because carriers suffering inelastic emission processes, which mostly lose a few multiples of the thermal energy kT, never get over the potential barrier back to the source electrode. Because the inelastic emission probability is far larger than the elastic and

elastic ħω source (bottleneck) inelastic emission Inelas. phonons (energy relaxation)  $\hbar\omega_{f-TA}=19$  $D_{\rm f-TA} = 3 \times 10^7$  $D_{\rm f-LA} = 2 \times 10^8$  $\hbar\omega_{\rm f-LA} = 47$  $D_{\text{f-TO}} = 2 \times 10^8$  $\hbar\omega_{\text{f-TO}} = 59$  $\hbar \omega_{g-TA} = 12$  $D_{g-TA} = 5 \times 10^7$  $D_{g-LA} = 8 \times 10^7$  $\hbar\omega_{g-LA}=19$  $D_{\rm g-LO} = 1.1 \times 10^{-9}$  $\hbar\omega_{\rm g-LO}$  = 61 (meV) (eV/cm)

Fig. 1. Characteristics of elastic and inelastic phonon scattering on carrier transport. The inelastic phonon energies  $\hbar\omega$ 's and deformation potentials D's are also indicated.

inelastic absorption probabilities, inelastic emission processes may improve the ballisticity [11], [12]. This interesting phenomenon is important for the practical design of ballistic MOSFETs, so we quantitatively examine this prediction using a quantum-corrected Monte Carlo device simulator. We find that inelastic emission processes do indeed help to achieve a ballistic current, even in the presence of scattering, if the channel length is reduced to the 10-nm scale. On the other hand, for longer channel devices, the inelastic emission process degrades the drain current because the source-end bottleneck barrier is enlarged by the associated charge accumulation. In the last part of this paper, we discuss a possibility for enhancing the ballisticity by electrically narrowing the bottleneck barrier in long-channel devices.

### II. ROLES OF ELASTIC AND INELASTIC PHONON SCATTERING

#### A. Qualitative Description

Fig. 1 shows the characteristics of elastic and inelastic phonon scattering related to carrier transport. Carriers are injected into the channel with kinetic energy on the order of kT, and they suffer elastic and inelastic scattering events in the channel. The total kinetic energy of a carrier is conserved before and after elastic scattering, whereas it is significantly altered by inelastic scattering via phonon absorption and emission processes. In Fig. 1, the inelastic phonon energies  $\hbar\omega$ 's

Manuscript received August 8, 2007; revised May 2, 2008. This work was supported by a NEDO/MIRAI project. The review of this paper was arranged by Editor S. Datta.

Digital Object Identifier 10.1109/TED.2008.927384

H. Tsuchiya is with the Graduate School of Engineering, Kobe University, Kobe 657-8501, Japan (e-mail: tsuchiya@eedept.kobe-u.ac.jp).

S. Takagi is with the School of Engineering, The University of Tokyo, 113-8656. Japan.

and the deformation potentials D's are indicated [13]. As is well known, the g-longitudinal optical (LO) phonon with  $\hbar\omega=61$  meV is dominant. As a consequence, the inelastic phonon emission is suppressed at the beginning of the channel because the carrier energy is initially too small. In addition, phonon absorption is rare at ordinary temperatures, so that elastic scattering (such as of acoustic phonons) dominates at the beginning of the channel, and occasionally returns carriers back to the source. If a carrier survives this region, it is subsequently exposed to frequent optical phonon emission and immediately loses energy in multiples of kT (mostly  $\hbar\omega_{q-LO}=61$  meV). Because the carrier then has little chance of returning to the source and is eventually absorbed into the drain, the current is reduced from its ballistic value only because of backscattering at the beginning of the channel. Based on these ideas, Natori has suggested that inelastic emission suppresses backscattering and improves the ballisticity [11], [12]. In this paper, we examine Natori's prediction using a quantum-corrected Monte Carlo simulation described in the next section.

#### B. Monte Carlo Approach

In this paper, we consider only phonon scattering in order to test Natori's prediction. Surface roughness scattering is not included. We performed Monte Carlo simulations under the following different scattering conditions in the channel region:

- 1) no scattering processes;

- only elastic processes;

- 3) elastic + inelastic emission processes;

- 4) elastic + inelastic emission and absorption processes.

Elastic processes represent intravalley acoustic phonon scattering, whereas inelastic processes are intervalley phonon scattering due to the inelastic phonons shown in Fig. 1. Cases 1) and 4) correspond to a ballistic channel and to an actual MOS-FET channel, respectively. In the source and drain electrodes, all scattering processes (including plasmon scattering [9]) are included to activate the rapid decay of hot electrons in the electrodes. In particular, plasmon scattering ensures that the carrier distribution relaxes to an equilibrium distribution in a very short distance [6]. The redistribution of electric charges and of the electrostatic potential due to each scattering mechanism was examined by solving the 2-D Poisson equation selfconsistently. Degeneracy effects are incorporated in a manner such that a distribution function  $f_{\nu}(\mathbf{k}, \mathbf{r})$  is tabulated at each location throughout the device, and any scattering processes are rejected if the final electron state and band index  $\nu$  are such that  $1 - f_{\nu}(\mathbf{k}, \mathbf{r}) \leq \eta$ , where  $\eta$  is a random number between zero and one [7].

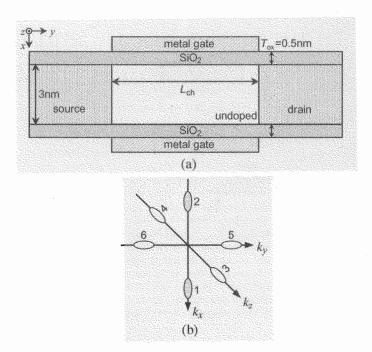

The simulated device is shown in Fig. 2(a), using a double-gate and ultrathin body structure ( $T_{\rm Si}=3$  nm) to suppress short-channel effects. For simplicity, the gate tunneling effect is neglected. A metal gate is employed, and its work function is taken to be 4.42 eV. The donor concentration in the source and drain regions is set at  $N_D=1.0\times 10^{20}~{\rm cm}^{-3}$ , and the channel region is assumed to be undoped. The channel length is variable, and the temperature is 300 K.

The electrical characteristics were computed using the Monte Carlo device simulator with quantum mechanical

Fig. 2. (a) Device structure used in the simulation and (b) equi-energy surfaces of the silicon conduction band, where the channel region is assumed to be undoped. A metal gate is employed, and its work function is 4.42 eV.

correction (MONAQO) developed at Kobe University. In this method, the equations of motion for particles in free flight are given as

$$\frac{d\mathbf{r}}{dt} = \mathbf{v} \tag{1}$$

$$\frac{d\mathbf{k}}{dt} = -\frac{1}{\hbar} \nabla_{\mathbf{r}} \left( U + U_{\nu}^{QC} \right). \tag{2}$$

The particles evolve not only due to the classical potential U but also due to the quantum correction  $U_{\nu}^{\rm QC}$  represented as [7]–[9]

$$U_{\nu}^{\rm QC} = -\frac{\hbar^2}{12m_x^{\nu}} \frac{\partial^2 \ln(n_{\nu})}{\partial x^2} - \frac{\hbar^2}{12m_y^{\nu}} \frac{\partial \ln(n_{\nu})}{\partial y^2} - \frac{\hbar^2}{12m_z^{\nu}} \frac{\partial^2 \ln(n_{\nu})}{\partial z^2}$$

(3)

where the index  $\nu=(1,2,\ldots,6)$  denotes the six equivalent valleys in the silicon conduction band shown in Fig. 2(b). Here,  $n_{\nu}$  represents the carrier density, and  $m_{x}^{\nu}$ ,  $m_{y}^{\nu}$ , and  $m_{z}^{\nu}$  are the effective masses of the ellipsoidal band structure. It has been previously demonstrated that the MONAQO can simulate quantized subbands in the inversion layer and source—drain tunneling, and so, it is applicable to quantum transport simulations in nanoscale MOSFETs [7]–[9].

#### C. Simulation Results

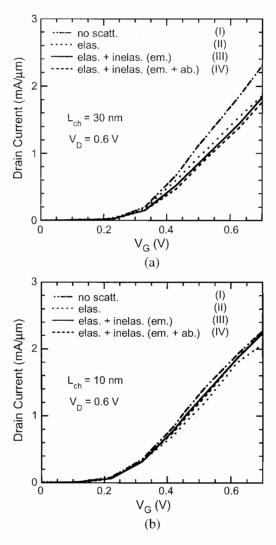

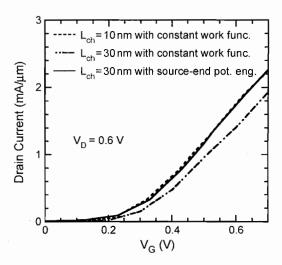

Fig. 3 shows  $I_D$ – $V_G$  characteristics computed for (a)  $L_{\rm ch}=30$  nm and (b)  $L_{\rm ch}=10$  nm, where the threshold voltage is fixed at 0.3 V for the no-scattering cases. The drain voltage  $V_D$  is 0.6 V. The drain current for  $L_{\rm ch}=30$  nm monotonically decreases as each scattering mechanism is added, as shown in Fig. 3(a). On the other hand, as seen in Fig. 3(b), the drain current for  $L_{\rm ch}=10$  nm slightly increases when inelastic

Fig. 3.  $I_D$ – $V_G$  characteristics computed for (a)  $L_{\rm ch}=30$  nm and (b)  $L_{\rm ch}=10$  nm, where the threshold voltage is 0.3 V for no-scattering processes. The drain voltage  $V_D$  is 0.6 V.

emission processes are included. A similar increase in drain current when the inelastic emission process is included has been recently reported for carbon nanotube MOSFETs under low- $V_G$  conditions [14]. However, in the latter case, the inelastic process significantly decreases the drain current when the gate voltage exceeds a well-defined threshold. Such a drain current decrease for large  $V_G$  is not observed in Fig. 3(b), but instead, the drain current approaches the ballistic current. This may be because the 3-D carrier transport is simulated here with a quantum correction.

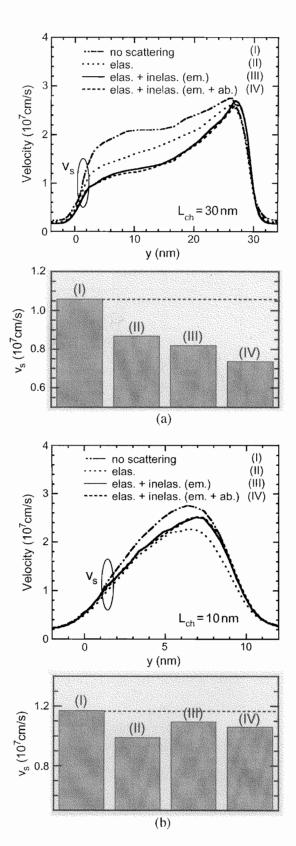

We computed the average electron velocity profiles, as shown in Fig. 4, where (a)  $L_{\rm ch}=30$  nm and (b)  $L_{\rm ch}=10$  nm, and the gate voltage is 0.5 V. The lower portion of each figure summarizes the source-end velocities  $v_s$ , defined as the electron velocity at the bottleneck point. It is found that elastic and inelastic absorption processes decrease  $v_s$  for both channel lengths. On the other hand, inelastic emission processes have the opposite effect on  $v_s$  for the longer channel length. That is, the inelastic emission process increases  $v_s$  for  $L_{\rm ch}=10$  nm, which is in agreement with Natori's prediction [11], [12], whereas it decreases  $v_s$  for  $L_{\rm ch}=30$  nm.

Fig. 4. Average electron velocity profiles computed for (a)  $L_{\rm ch}=30$  nm and (b)  $L_{\rm ch}=10$  nm, when the gate voltage is 0.5 V. The lower figures summarize the source-end velocities  $v_s$ .

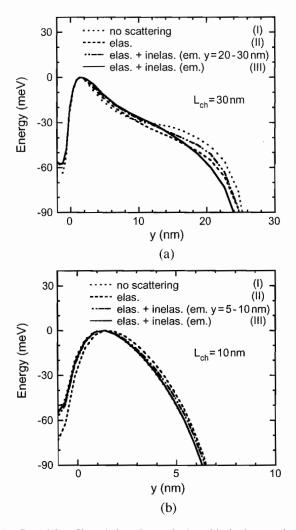

To further probe the dependence on inelastic emission processes, we examined variations in the potential profiles, as shown in Fig. 5 for (a)  $L_{\rm ch}=30$  nm and (b)  $L_{\rm ch}=10$  nm. The plotted profiles are averaged over the carrier density in

Fig. 5. Potential profile variations due to elastic and inelastic scattering processes, where (a)  $L_{\rm ch}=30$  nm and (b)  $L_{\rm ch}=10$  nm. The effects of localized phonon emission in the drain side of the channel are also plotted to clarify the influence of charge accumulation during the inelastic emission process.

the vertical direction. The effects on localized phonon emission in the drain side of the channel are also plotted to clarify the influence of charge accumulation during the inelastic emission process. For  $L_{\rm ch}=30$  nm, the bottleneck barrier is found to broaden due to the accumulated charges, even due to localized phonon emission in the drain side of the channel (y=20-30 nm). Therefore, inelastic phonon emission influences the carrier transport via the modulation of the source-end potential in a long-channel device, and consequently, the drain current decreases.

On the other hand, the source-end potential shape hardly changes due to scattering for the shorter channel device, as shown in Fig. 5(b), implying that the charge accumulation has a negligible influence on the potential profile in ultrashort-channel MOSFETs. Consequently, the suppression of backscattering due to inelastic phonon emission can give rise to a ballistic current in the short channel device. It is likely that the different dependence of inelastic phonon emission on  $L_{\rm ch}$  results from the different lengths of the bottleneck barrier. Therefore, it may be possible to enhance the ballisticity by reducing the bottleneck barrier length, as discussed in the next section.

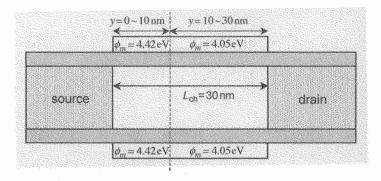

Fig. 6. Device structure with two different gate work functions (4.42 and 4.05 eV) in both the top and bottom gate electrodes, where  $L_{\rm ch}=30$  nm and the smaller work-function region extends from y=10 to 30 nm in the channel.

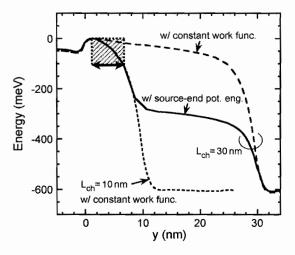

Fig. 7. Potential profiles computed at  $V_G=0.5~\rm V$  for  $L_{\rm ch}=10~\rm mm$  with a constant work function, for  $L_{\rm ch}=30~\rm mm$  with a constant work function, and for  $L_{\rm ch}=30~\rm mm$  with source-end potential engineering. For the constant work-function simulations, we used a work function of 4.42 eV throughout the gate.

#### III. SOURCE-END POTENTIAL ENGINEERING

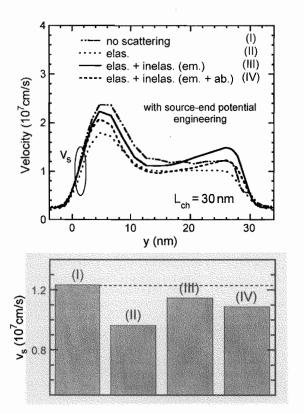

Several ideas have previously been proposed to realize lateral channel engineering, such as asymmetric channel doping [15] and hetero-material gate with dual work functions [16], [17]. In this paper, we employed a hetero-material gate structure with dual work functions because the channel region is undoped. Fig. 6 shows the device structure with two different gate work functions, 4.42 and 4.05 eV, in both the top and bottom gate electrodes. Here,  $L_{\rm ch}=30$  nm, and the smaller work-function region extends from y = 10 to 30 nm in the channel. The potential profile computed at  $V_G = 0.5$  V is shown in Fig. 7, which is similar to that in [18, Fig. 3]. The same length of bottleneck barrier as for  $L_{\rm ch}=10$  nm with a constant work function is obtained for  $L_{\rm ch}=30$  nm with source-end potential engineering. As a result, the source-end velocity is significantly enhanced, as shown in Fig. 8. It is noteworthy that, even in this long-channel device, the source-end velocity increases due to inelastic phonon emission, just as shown in Fig. 4(b). These results indicate that the reduction of the bottleneck barrier length to the nanometer scale is required to enhance the ballisticity due to inelastic emission processes.

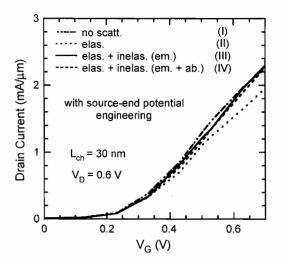

We confirmed that the drain current increase due to inelastic phonon emission is obtained in the long-channel device, as

Fig. 8. Average electron velocity profiles and source-end velocities computed for  $L_{\rm ch}=30$  nm with source-end potential engineering at  $V_G=0.5$  V.

Fig. 9.  $I_D$ – $V_G$  characteristics computed for  $L_{\rm ch}=30$  nm with source-end potential engineering, where the drain voltage  $V_D$  is fixed at 0.6 V.

shown in Fig. 9 for  $V_D=0.6$  V. The current reduction due to elastic processes is more striking in Fig. 9 than in Fig. 3(b) because the longer the channel, the greater the number of elastic events. Finally, Fig. 10 compares  $I_D$ – $V_G$  characteristics for  $L_{\rm ch}=10$  nm with a constant work function,  $L_{\rm ch}=30$  nm with a constant work function, and  $L_{\rm ch}=30$  nm with source-end potential engineering. We see that the same current drive as in the  $L_{\rm ch}=10$ -nm device can be obtained by employing source-end potential engineering in a longer channel device.

These results suggest that source-end potential engineering is effective in achieving ballistic current in Si MOSFETs. Although the same lithography technique as used for 10-nm

Fig. 10. Comparison of the  $I_D$ - $V_G$  characteristics for  $L_{\rm ch}=10$  nm with a constant work function, for  $L_{\rm ch}=30$  nm with a constant work function, and for  $L_{\rm ch}=30$  nm with source-end potential engineering. The threshold voltage is fixed at 0.3 V.

channel devices is probably required to pattern the two different gate work functions, source-end potential engineering might be useful in designing ballistic MOSFETs with superior immunity to short-channel effects. To examine how effective the source-end potential engineering is in practice, we need to investigate surface roughness scattering with a fluctuation in the subband energy profiles in an ultrathin body structure [19].

#### IV. CONCLUSION

Understanding scattering effects is increasingly important for practical design of Si MOSFETs with 10-nm-scale channel lengths. In this paper, we found that, as the channel length is reduced to the 10-nm scale, inelastic phonon emission processes help achieve ballistic current, even in the presence of scattering, which is in agreement with Natori's predictions. However, for longer channel devices, inelastic phonon emission processes degrade the drain current due to space charge effects caused by the associated charge accumulation. We further demonstrated that reducing the bottleneck barrier length to the nanometer scale is required to enhance the ballisticity due to inelastic phonon emission. Based on these findings, we propose that source-end potential engineering can improve the ballisticity.

#### REFERENCES

- H. Wakabayashi, S. Yamagami, N. Ikezawa, A. Ogura, M. Narihiro, K. Arai, Y. Ochiai, K. Takeuchi, T. Yamamoto, and T. Mogami, "Sub-10-nm planar-bulk-CMOS devices using lateral junction control," in *IEDM Tech. Dig.*, 2003, pp.989-991.

- [2] K. Natori, "Ballistic metal-oxide-semiconductor field effect transistor," J. Appl. Phys., vol. 76, no. 8, pp. 4879–4890, 1994.

- [3] K. Natori, "Scaling limit of the MOS transistor—A ballistic MOSFET," IEICE Trans. Electron., vol. E84-C, no. 8, pp. 1029–1036, 2001.

- [4] M. Lundstrom, "Elementary scattering theory of the Si MOSFET," *IEEE Electron Device Lett.*, vol. 18, no. 7, pp. 361–363, Jul. 1997.

- [5] M. Lundstrom and Z. Ren, "Essential physics of carrier transport in nanoscale MOSFETs," *IEEE Trans. Electron Devices*, vol. 49, no. 1, pp. 133-141, Jan. 2002.

- [6] P. Palestri, D. Esseni, S. Eminente, C. Fiegna, E. Sangiorgi, and L. Selmi, "Understanding quasi-ballistic transport in nano-MOSFETs: Part I—Scattering in the channel and in the drain," *IEEE Trans. Electron Devices*, vol. 52, no. 12, pp. 2727–2735, Dec. 2005.

- [7] H. Tsuchiya, K. Fujii, T. Mori, and T. Miyoshi, "A quantum-corrected Monte Carlo study on quasi-ballistic transport in nanoscale MOSFETs," *IEEE Trans. Electron Devices*, vol. 53, no. 12, pp. 2965–2971, Dec. 2006.

- [8] H. Tsuchiya, M. Horino, M. Ogawa, and T. Miyoshi, "Quantum transport simulation of ultrathin and ultrashort silicon-on-insulator metal-oxide-semiconductor field-effect transistors," *Jpn. J. Appl. Phys.*, vol. 42, no. 12, pp. 7238–7243, 2003.

- [9] H. Tsuchiya, A. Oda, M. Ogawa, and T. Miyoshi, "A quantum-corrected Monte Carlo and molecular dynamics simulation on electron-densitydependent velocity saturation in silicon metal-oxide-semiconductor field-effect transistors," *Jpn. J. Appl. Phys.*, vol. 44, no. 11, pp. 7820– 7826, 2005.

- [10] K. Natori, "Ballistic MOSFET reproduces current-voltage characteristics of an experimental device," *IEEE Electron Device Lett.*, vol. 23, no. 11, pp. 655–657, Nov. 2002.

- [11] K. Natori and T. Kurusu, "Nanoscale quasi-ballistic MOSFETs in reflection-transmission model," in *Proc. Int. Conf. SSDM*, Tokyo, Japan, Sep. 2004, pp. 728–729.

- [12] K. Natori, "Prospective characteristics of nanoscale MOSFETs," in Proc. ICSICT, Shanghai, China, Oct. 2006, pp. 47–50.

- [13] C. Jacoboni and L. Reggiani, "The Monte Carlo method for the solution of charge transport in semiconductors with applications to covalent materials," Rev. Mod. Phys., vol. 55, no. 3, pp. 645–705, 1983.

- [14] S. Koswatta, S. Hasan, M. Lundstrom, M. Anantram, and D. Nikonov, "Ballisticity of nanotube field-effect transistors: Role of phonon energy and gate bias," *Appl. Phys. Lett.*, vol. 89, no. 2, p. 023 125, 2006.

- [15] S. Odanaka and A. Hiroki, "Potential design and transport property of 0.1-μm MOSFET with asymmetric channel profile," *IEEE Trans. Electron Devices*, vol. 44, no. 4, pp. 595–600, Apr. 1997.

- [16] X. Zhou and W. Long, "A novel hetero-material gate (HMG) MOSFET for deep-submicron ULSI technology," *IEEE Trans. Electron Devices*, vol. 45, no. 12, pp. 2546–2548, Dec. 1998.

- [17] X. Zhou, "Exploring the novel characteristics of hetero-material gate field-effect transistors (HMGFETs) with gate-material engineering," *IEEE Trans. Electron Devices*, vol. 47, no. 1, pp. 113–120, Jan. 2000.

- [18] J. Guo, Z. Ren, and M. Lundstrom, "A computational exploration of lateral channel engineering to enhance MOSFET performance," *J. Comput. Electron.*, vol. 1, no. 1, pp. 185–189, 2002.

- [19] K. Uchida, J. Koga, and S. Takagi, "Experimental study on carrier transport mechanisms in double- and single-gate ultrathin-body MOSFETs—Coulomb scattering, volume inversion, and  $\delta T_{\rm SOI}$ -induced scattering," in *IEDM Tech. Dig.*, 2003, pp. 805–808.

**Hideaki Tsuchiya** (M'93–SM'01) was born in Ehime, Japan, on August 12, 1964. He received the B.S., M.S., and Ph.D. degrees in electronic engineering from Kobe University, Kobe, Japan, in 1987, 1989, and 1993, respectively.

In 1993, he was with the Department of Electrical and Electronics Engineering, Kobe University, as a Research Associate. He has been engaged in research of quantum transport simulation of mesoscopic devices. From 1999 to 2000, he was a Visiting Scientist with the University of Illinois, Urbana. Since 2003,

he has been an Associate Professor with the Graduate School of Engineering, Kobe University. His current research includes the quantum transport modeling in nanoscale MOSFETs and the first-principles simulation in atomic-scale devices.

Dr. Tsuchiya is a member of the Institute of Electronics, Information, and Communication Engineers of Japan and the Japan Society of Applied Physics. He received the Young Scientist Award in 1998 from the Japan Society of Applied Physics and the Outstanding Achievement Award for a pioneering research on nanoscale device simulator in 2006 from the Institute of Electronics, Information, and Communication Engineers of Japan.

Shin-ichi Takagi (M'93) was born in Tokyo, Japan, on August 25, 1959. He received the B.S., M.S., and Ph.D. degrees in electronic engineering from The University of Tokyo, Tokyo, Japan, in 1982, 1984, and 1987, respectively. His Ph.D. thesis involved the study on the surface carrier transport in MISFETs based on III–V semiconductors.

He was with the Toshiba Research and Development Center, Kawasaki, Japan, in 1987, where he was engaged in the research on the device physics of Si MOSFETs, including the carrier transport in the

inversion layer, the impact ionization phenomena, the hot-carrier degradation, and the electric properties of Si/SiO<sub>2</sub> interface. From 1993 to 1995, he was a Visiting Scholar with Stanford University, Stanford, CA, where he studied the Si/SiGe heterostructure devices. When he was with the ULSI Research Laboratories, he was also engaged in the physics and technology of the reliability of SiO<sub>2</sub>, ferroelectric devices, and strained-Si MOS devices. Since 2001, he has been working for the Millennium Research for Advanced Information Technology Project in the Advanced Semiconductor Research Center, National Institute of Advanced Industrial Science and Technology, Tsukuba, Japan, as the Leader of the Ultra-High Performance New Transistor Structures Theme. Since October 2003, he has been with The University of Tokyo, where he is currently a Professor in the Department of Electrical Engineering and Information Systems, the School of Engineering. His recent interests include the science and the technologies of advanced CMOS devices using new channel materials such as strained Si, Ge, and III–Vs.

Dr. Takagi is a member of the IEEE Electron Devices Society and the Japan Society of Applied Physics. He served on the Technical Program Committee on several international conferences including the International Electron Devices Meeting, the International Reliability Physics Symposium, the International Conference on Solid State Devices and Materials, and the International Solid State Circuits Conference.