PDF issue: 2025-12-05

## A 40-nm 0.5-V 12.9-pJ/Access 8T SRAM Using Low-Energy Disturb Mitigation Scheme

Yoshimoto, Shusuke ; Terada, Masaharu ; Okumura, Shunsuke ; Suzuki, Toshikazu ; Miyano, Shinji ; Kawaguchi, Hiroshi ; Yoshimoto, Masahiko

### (Citation)

IEICE Transactions on Electronics, 95(4):572-578

(Issue Date) 2012-04-01

(Resource Type) journal article

(Version)

Version of Record

(Rights)

copyright©2012 IEICE

(URL)

https://hdl.handle.net/20.500.14094/90002972

PAPER Special Section on Solid-State Circuit Design — Architecture, Circuit, Device and Design Methodology

# A 40-nm 0.5-V 12.9-pJ/Access 8T SRAM Using Low-Energy Disturb Mitigation Scheme\*

Shusuke YOSHIMOTO<sup>†a)</sup>, Student Member, Masaharu TERADA<sup>†</sup>, Nonmember, Shunsuke OKUMURA<sup>†</sup>, Student Member, Toshikazu SUZUKI<sup>††</sup>, Member, Shinji MIYANO<sup>††</sup>, Senior Member, Hiroshi KAWAGUCHI<sup>†</sup>, and Masahiko YOSHIMOTO<sup>†††</sup>, Members

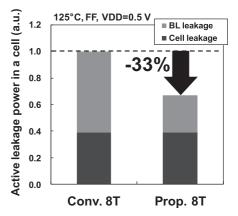

This paper presents a novel disturb mitigation scheme which achieves low-energy operation for a deep sub-micron 8T SRAM macro. The classic write-back scheme with a dedicated read port overcame both half-select and read-disturb problems. Moreover, it improved the yield, particularly in the low-voltage range. The conventional scheme, however, consumed more power because of charging and discharging all write bitlines in a sub-block. Our proposed scheme reduces the power overhead of the write-back scheme using a floating write bitline technique and a low-swing bitline driver (LSBD). The floating bitline and the LSBD respectively consist of a precharge-less CMOS equalizer (transmission gate) and an nMOS write-back driver. The voltage on the floating write bitline is at an intermediate voltage between the ground and the supply voltage before a write cycle. The write target cells are written by normal CMOS drivers, whereas the write bitlines in half-selected columns are driven by the LSBDs in the write cycle, which suppresses the write bitline voltage to VDD -  $V_{\rm tn}$  and therefore saves the active power in the half-selected columns (where  $V_{\rm tn}$  is a threshold voltage of an nMOS). In addition, the proposed scheme reduces a leakage current from the write bitline because of the floating write bitline. The active leakage is reduced by 33% at the FF corner, 125°C. The active energy in the write operation is reduced by 37% at the FF corner. In other process corners, more writing power reduction can be expected because it depends on the  $V_{\rm tn}$  in the LSBD. We fabricated a 512-Kb 8T SRAM test chip that operates at a single 0.5-V supply voltage. The test chip with the proposed scheme respectively achieves 1.52-µW/MHz writing energy and 72.8-µW leakage power, which are 59.4% and 26.0% better than those of the conventional write-back scheme. The total energy is  $12.9 \,\mu\text{W/MHz}$  (12.9 pJ/access) at a supply voltage of 0.5 V and operating frequency of 6.25 MHz in a 50%-read/50%-write operation.

key words: SRAM, 8T, low energy, disturb, half select, write back

#### 1. Introduction

As process technology has been scaled down, it has become increasingly difficult to realize a stable bitcell design in a 6T SRAM because of the tradeoff between read and write margins [2]. An 8T bitcell with a dedicated read port is proposed to obviate the 6T's read margin, which achieves low-voltage operation in nature.

The separation of read and write ports frees the bitcell design of the read/write tradeoff. The area of the 8T cell is expected to be smaller than that of the 6T cell in a future pro-

Manuscript received August 17, 2011.

Manuscript revised November 4, 2011.

<sup>†</sup>The authors are with Kobe University, Kobe-shi, 657-8501 Japan.

††The authors are with Semiconductor Technology Academic Research Center (STARC), Yokohama-shi, 222-0033 Japan.

†††The author is with JST, CREST, Kobe-shi, 657-8501 Japan.

\*This paper is the extended version of the original paper presented at the 2011 Symposium on VLSI Circuits [1].

a) E-mail: yoshipy@cs28.cs.kobe-u.ac.jp DOI: 10.1587/transele.E95.C.572

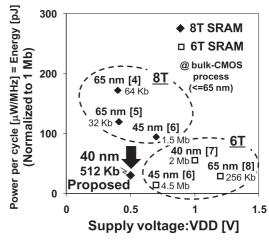

Fig. 1 Supply voltage versus energy among low-power bulk-CMOS SRAMs [4]–[8].

cess [3]. Although low-voltage and high-yield 8T SRAMs under 1.0-V operation are proposed [4]–[6], the power per operation cycle (= energy) is larger than that in 6T SRAMs [6]–[8] because the 8T cell needs an extra 2T read port. Furthermore, an assist circuit must be implemented to avoid the disturb (half-select) problem [9]. Figure 1 portrays the tendency of power per cycle among recent SRAMs. Our research object is to achieve a low-voltage and low-energy SRAM: 0.5-V and sub- $100\,\mu\text{W/MHz/Mb}$  operation is the target.

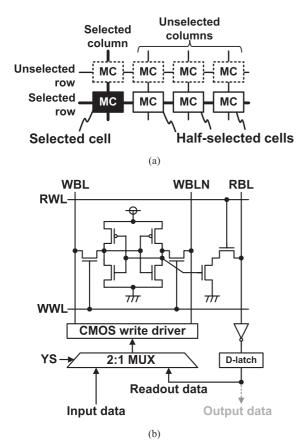

Figure 2(a) depicts selected and half-selected cells in an SRAM array. On an activated wordline, the selected cells are written by write drivers. However, half-selected cells are disturbed by the precharged write bitlines. When the writability of the SRAM cell is enhanced, the static noise margin of the half-selected cell is decreased, and vice versa. The half-select problem degrades the SRAM operation margin. To mitigate the half-select problem and lower the operating voltage, the divided wordline structure [10] and the write-back scheme [11] (Fig. 2(b)) are useful in the 8T SRAM at a single supply voltage.

The divided wordline structure produces no halfselected cells by incorporating separate wordlines, but aligning a word with physically adjacent bits (wordinterleaving) weakens a soft error immunity against singleevent multiple-cell upsets (MCU) caused by ionized-particle strikes. A recent work [12] reports that a ratio of MCU to

**Fig. 2** (a) Selected cell and half-selected cells in the SRAM array. (b) Conventional write-back scheme [3] with a single-ended 8T cell.

the total single-event upsets is as high as about 50% and that the failed bits spread out in more than  $1,000 \times 1,000 \, (= 1 \, \mathrm{M})$  bits at a 22-nm node. In a bit-leaving structure, multiple-bit upsets (MBU = MCU in a same word) can be, however, suppressed to a reasonable FIT (failure in time) value by single-bit error correction coding (ECC) [13], because more than 99% of the MCU in a wordline direction are adjacent two bits [12]. In contrast, the MBU in the divided wordline structure cannot be suppressed by single-bit ECC because the failed two bits are physically adjacent in the same word.

Although different design requirements [14] in the latest SRAMs necessitate various functionalities, and although one functionality is the partial-write operation [15], the partial-write operation cannot be implemented in the divided wordline structure because a separated wordline is incorporated.

The write-back scheme for the 8T SRAM design can be implemented in the bit-interleaving structure, which provides soft-error immunity and partial-write functionality. The write-back scheme eliminates the half-select problem; however, a read operation is required even in a write cycle. In the write-back scheme in the write operation, input data to be written go to target cells at target columns, but at half-selected columns, readout data are written back to half-selected cells. Because the readout data at the half-selected columns do not need to be transferred to output buffers, the

speed penalty in the write-back scheme can be minimized.

The write-back scheme has power overhead because the CMOS write drivers fully pull the write bitlines (WBL/WBLN) up or down at all half-selected columns. The WBLs are usually longer than read bitlines (RBL) to preserve array efficiency [5]. Consequently, the active energy in the half-selected columns degrades the energy efficiency.

To achieve low-energy operation without the divided wordline structure, we propose a novel disturb mitigation scheme in this paper. The proposed scheme reduces the active power and a leakage power using a low-swing bitline driver (LSBD) and a precharge-less CMOS equalizer (transmission gate) for a floating write bitline.

The remaining part of this paper is organized as follows. The circuit implementation of the proposed LSBD and the precharge-less CMOS equalizer for the floating write bitline in the disturb mitigation scheme are discussed in Sect. 2 with simulation results. The proposed scheme improves the energy efficiency of the 8T SRAM. In Sect. 3, we present the experimentally-obtained results of a 40-nm 512-Kb SRAM test chip. Section 4 concludes the paper.

#### 2. Proposed Disturb Mitigation Scheme

To reduce extra energy for the half-select problem, we propose a disturb mitigation scheme that features the following: floating WBLs with a precharge-less equalizer (CMOS transmission gate) and the low-swing bitline driver (LSBD) with nMOS pull-up transistors for the WBLs, which limit the swing of the WBLs in the half-selected columns.

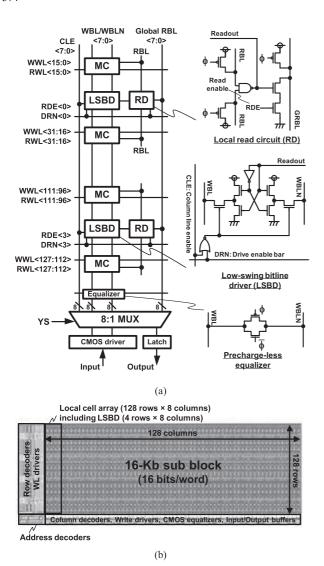

Figures 3(a) and 3(b) portray a local cell array (128 rows × 8 columns) and a 16-Kb sub-block (16 local cell arrays) configuration of the proposed SRAM. Figure 3(a) also shows circuitry of the local read circuit, the LSBD, and the precharge-less equalizer. The single-ended 8T cell is adopted in the SRAM as presented in Fig. 2(b). The proposed 8T SRAM employs a hierarchical read bitline (RBL) structure. The number of cells per RBL is 16 for stable read operation. In contrast, a WBL is shared by 128 cells to preserve the array efficiency. The WBLs are not precharged to a supply voltage, but floated because of the precharge-less equalizer. A local read circuit and an LSBD are shared by 32 cells. A CMOS write driver is shared by a local cell array.

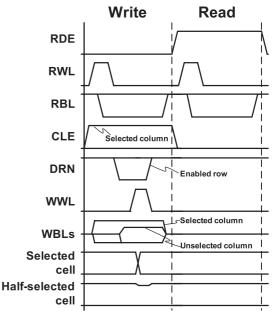

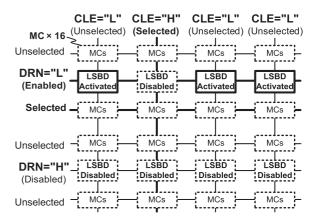

Figure 4 portrays operating waveforms of the proposed scheme. In a read cycle, a read enabling (RDE) signal is activated; then a global read bitline (GRBL) is discharged when an RBL is pulled down. In the write cycle, the dedicated read ports transport the data to the local read circuits. Column line enable (CLE) signals are high in the selected columns and the LSBDs are disabled as presented in Fig. 5. In the half-selected columns (CLE = "L"), the proposed LS-BDs drive the WBLs according to the readout data when the driver enable (DRN) signal is grounded. The LSBD consists only of nMOSes. Thereby, the swing of WBLs is limited by the threshold voltage of the nMOSes. After the WBLs are pulled up or down by nMOS-based LSBDs, the write word-line (WWL) is activated. The selected cell is written by the

**Fig. 3** (a) Local cell array and (b) 16-Kb sub-block with the proposed circuitry including a low-swing bitline driver (LSBD) and precharge-less equalizer. "MC" signifies "single-ended 8T memory cell", as presented in Fig. 2(b).

CMOS write driver and the write margin is not degraded.

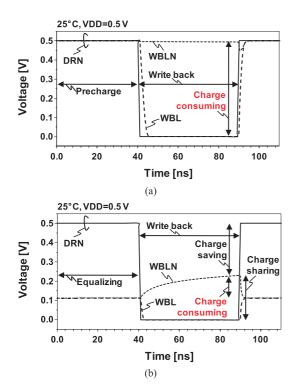

Figures 6(a) and 6(b) respectively show waveforms of the write bitline pair (WBLs: WBL and WBLN) in the halfselected columns with the conventional write-back scheme and the proposed scheme. In the conventional write-back scheme, the WBLs are precharged to supply voltage until the DRN signal is pulled down. The WBL is grounded and the WBLN is pulled up by the CMOS drivers. When the write operation is finished, the WBLs are precharged again. In contrast, the WBLs in the proposed scheme are floated until the DRN activation. When the WBL and WBLN are pulled down and up by the proposed LSBD, then the charging energy is saved because the rising write bitline voltage is saturated at an intermediate voltage by the threshold voltage of an nMOS in the LSBD. At the end of the write cycle, the write bitlines' voltages are again equalized with charge sharing. The floating WBLs reduce bitline leakage current

Fig. 4 Operating waveforms.

**Fig. 5** Activated LSBDs exist on low-state CLE (column line enable) and low-state DRN (driver enable bar) signals.

because no precharge transistors are incorporated.

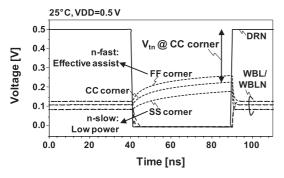

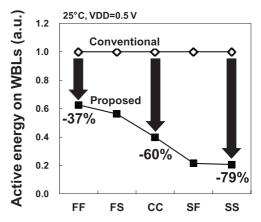

Figure 7 shows that a pulled-up WBL level depends on  $V_{\rm tn}$ : if an nMOS is fast, then the  $V_{\rm tn}$  drop is small, the disturb mitigating assist becomes effective. However, a slow nMOS can save power because its swing is small. The enlarged margin and saving power are a tradeoff. Figure 8 portrays the active power reduction compared to the conventional write-back scheme at the write cycle. The active energy on the WBLs is reduced by 37%, 60%, and 79%, respectively at the FF, CC, and SS corners at 25°C.

We investigated the disturbance margins of the half-select cells with the proposed disturb mitigation scheme. Monte-Carlo analyses are executed at the five process corners and at three temperatures when VDD is 0.5 V. The simulation considers threshold voltage variation in the LSBD shared by 32 bitcells. The yield in Table 1 shows that the SS corner at  $-40^{\circ}$ C is the worst case and its yield is  $3.27\sigma$ , in

**Fig. 6** Waveforms of the half-selected cells assisted by (a) the conventional write-back scheme and (b) the proposed scheme.

Fig. 7 Pulled-up WBL level dependence on the global corner.

Table 1 Yields of half-selected cells in the proposed scheme.

| Yield @ 0.5 V          |    | Temperature [°C] |         |       |

|------------------------|----|------------------|---------|-------|

| (based on Monte Carlo) |    | -40              | 25 (RT) | 125   |

| Global corner          | FF | 5.39σ            | > 7σ    | > 7σ  |

|                        | FS | 4.79σ            | 5.59σ   | > 7σ  |

|                        | CC | 4.31σ            | 5.49σ   | > 7σ  |

|                        | SF | 4.04σ            | 5.45σ   | > 7σ  |

|                        | SS | 3.27σ            | 4.47σ   | 6.85σ |

which the pull-up transistors in the LSBD is weakened. In the worst case, the voltage of the suppressed WBL, "VDD –  $V_{\rm th}$ " is decreased. The weak pull-up transistor and the more suppressed WBL causes more disturbing current flowing through the pass gate transistor of the SRAM cell. The tradeoff between the yield at the global corner and the saved

Fig. 8 Active energy reductions on WBLs at the five process corners (RT, room temperature; VDD = 0.5 V).

**Fig. 9** Comparison of the active leakage powers of the conventional and proposed schemes (FF corner, 125°C, VDD = 0.5 V).

energy must be considered in the SRAM design.

Figure 9 portrays simulation results of the leakage power on the WBLs at the activated cycle in 8T bitcells. The leakage power in the worst corner is improved by 33% because of the low-swing feature of the LSBD.

#### 3. Measurement Results

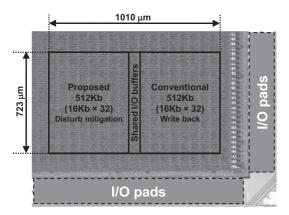

As presented in Fig. 10, we fabricated the proposed and conventional 512-Kb 8T SRAM macros using a 40-nm CMOS bulk process for comparison. The conventional macro incorporates a write bitline precharger connected to a supply voltage. Therefore, its write bitlines are fully charged and discharged in the write-back operation. The proposed 512-Kb macro consists of  $32 \times 16$ -Kb sub-blocks, as shown in Fig. 3(b). Table 2 shows specifications of the proposed SRAM test chip. The 8T bitcell area is  $0.706 \, \mu \text{m}^2$ , which is 28% larger than a 6T cell with a  $\beta$  ratio of two. The transistor width of access gates is doubled to enhance a write margin while the other transistors are minimum sizing. The numbers of cells in a RBL and WBL are 16 and 128, respectively. The cell density is 701 Kb/mm².

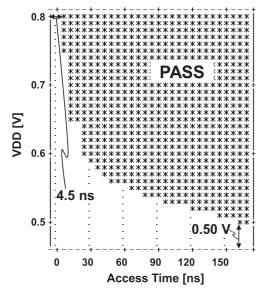

Figure 11 presents a measured Shmoo plot of the pro-

**Fig. 10** Micrographs of the test chip: 1 Mb SRAMs include the proposed disturb mitigating scheme and the conventional write back scheme.

Table 2

Features of the test chip.

| Technology               | 40-nm bulk CMOS                      |  |  |

|--------------------------|--------------------------------------|--|--|

| Macro size               | 0.723 mm × 1.010 mm                  |  |  |

| Macro configuration      | 512 Kb (16 Kb × 4 × 8), 16 bits/word |  |  |

| Cell size                | 0.706 mm (logic rule)                |  |  |

| # of cells / BL          | 16 (RBL), 128 (WBL)                  |  |  |

| Cell density             | 701 Kb/mm <sup>2</sup>               |  |  |

| Power supply             | 0.5–0.8 V                            |  |  |

| Write active energy      | 1.52 μW/MHz @ 0.5 V, 6.25MHz, RT     |  |  |

| Total energy (R/W=50/50) | 12.9 μW/MHz @ 0.5 V, 6.25MHz, RT     |  |  |

| Access time              | 160 ns @ 0.5 V, 4.5 ns @ 0.8 V       |  |  |

Fig. 11 Shmoo plot of the proposed 512-Kb SRAM macro.

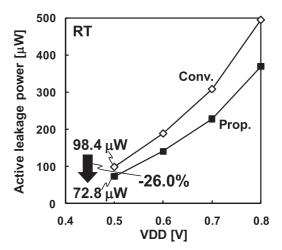

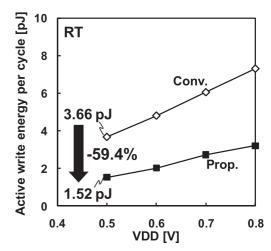

posed 8T SRAM macro. The access time is restricted by the read operation. The minimum operating voltage is 0.5 V at an access time of 160 ns at room temperature (RT). Figures 12 and 13 respectively show that the measured leakage power and active energy, which are improved by 26.0% and 59.4% at the supply voltage of 0.5 V. The active energy in

Fig. 12 Measured active leakage power at RT.

Fig. 13 Measured active energy per write cycle without leakage at RT.

the write cycle is 1.52 pJ (=  $\mu\text{W/MHz}$ ). The total energy is 12.9 pJ when the read and write cycles are 50-50 at 0.5 V.

#### 4. Conclusion

As described in this paper, a novel disturb mitigation scheme is proposed. It achieves low-power and low-voltage operation for an 8T SRAM. The proposed scheme has a  $3.27\sigma$  yield at  $0.5 \, \text{V}$  at the SS corner and low temperature. The active energy is improved by 37%, 60%, and 79% at FF, CC, and SS corners, respectively at 25°C. The 512-Kb 8T SRAM test chips were implemented in a 40-nm bulk-CMOS process. The SRAM operates at a single 0.5-V supply voltage at room temperature and achieves  $1.52\text{-}\mu\text{W}/\text{MHz}$  active energy in a write cycle and  $72.8\text{-}\mu\text{W}$  leakage power, which are 59.4% and 26.0% better than the conventional write-back scheme. The total energy is  $12.9 \, \mu\text{W}/\text{MHz}$  at  $0.5 \, \text{V}$  in a 50%-read / 50%-write operation.

#### Acknowledgments

This work was carried out as a part of the Extremely

Low Power (ELP) project supported by the Ministry of Economy, Trade and Industry (METI) and the New Energy and Industrial Technology Development Organization (NEDO). The authors would like to thank Mr. S. Moriwaki, Mr. A. Kawasumi with STARC, Prof. T. Sakurai, Prof. T. Hiramoto, Prof. K. Takeuchi and Dr. K. Miyaji with The University of Tokyo.

#### References

- [1] S. Yoshimoto, M. Terada, S. Okumura, T. Suzuki, S. Miyano, H. Kawaguchi, and M. Yoshimoto, "A 40-nm 0.5-V 20.1-μW/MHz 8T SRAM with low-energy disturb mitigation scheme," Digest of Technical Papers 2011 Symposium on VLSI Circuits, pp.72–73, June 2011

- [2] R. Heald and P. Wang, "Variability in Sub-100 nm SRAM Designs," Proc. International Conference on Computer Aided Design, pp.347–352, 2004.

- [3] Y. Morita, H. Fujiwara, H. Noguchi, Y. Iguchi, K. Nii, H. Kawaguchi, and M. Yoshimoto, "An area-conscious low-voltage-oriented 8T-SRAM design under DVS environment," IEEE Symposium on VLSI Circuits Digest of Technical Papers, pp.256–257, June 2007.

- [4] M.E. Sinangil, N. Verma, and A.P. Chandrakasan, "A reconfigurable 65 nm SRAM achieving voltage scalability from 0.25–1.2 V and performance scalability from 20 kHz–200 MHz," Proc. European Solid-State Circuits Conference, pp.282–285, 2008.

- [5] L. Chang, Y. Nakamura, R.K. Montoye, J. Sawada, A.K. Martin, K. Kinoshita, F.H. Gebara, K.B. Agarwal, D.J. Acharyya, W. Haensch, K. Hosokawa, and D. Jamsek, "A 5.3 GHz 8T-SRAM with operation down to 0.41 V in 65 nm CMOS," IEEE Symp. VLSI Circuit, Dig. Tech. Papers, pp.252–253, 2007.

- [6] K. Nii, M. Yabuuchi, Y. Tsukamoto, S. Ohbayashi, Y. Oda, and K. Usui, "A 45-nm single-port and dual-port SRAM family with robust read/write stabilizing circuitry under DVFS environment," IEEE Symposium on VLSI Circuits Digest of Technical Papers, pp.212–213, 2008.

- [7] K. Takeda, T. Saito, S. Asayama, Y. Aimoto, H. Kobatake, S. Ito, T. Takahashi, K. Takeuchi, M. Nomura, and Y. Hayashi, "Multistep word-line control technology in hierarchical cell architecture for scaled-down high-density SRAMs," IEEE Symposium on VLSI Circuits Digest of Technical Papers, pp.101–102, June 2010.

- [8] M. Khellah, N.S. Kim, J. Howard, G. Ruhl, M. Sunna, Y. Ye, J. Tschanz, D. Somasekhar, N. Borkar, F. Hamzaoglu, G. Pandya, A. Farhang, K. Zhang, and V. De, "A 4.2 GHz 0.3 mm<sup>2</sup> 256 kb Dual-V<sub>cc</sub> SRAM building block in 65 nm CMOS," ISSCC 2006 Digest of Technical Papers, pp.2572–2581, 2006.

- [9] D. Kim, V. Chandra, R. Aitken, D. Blaauw, and D. Sylvester, "Variation-aware static and dynamic writability analysis for voltagescaled bit-interleaved 8-T SRAMs," Proc. International Symposium on Low Power Electronics and Design, pp.145–150, 2011.

- [10] M. Yoshimoto, K. Anami, H. Shinohara, T. Yoshihara, H. Takagi, S. Agao, S. Kayano, and T. Nakano, "Divided Word-Line Structure in the Static RAM and Its Application to a 64K Full CMOS RAM," IEEE J. Solid State Circuits, vol.SC-18, no.5, pp.479–485, Oct. 1983.

- [11] J.J. Wu, Y.H. Chen, M.F. Chang, P.W. Chou, C.Y. Chen, H.J. Liao, M.B. Chen, Y.H. Chu, W.C. Wu, and H. Yamauchi, "A large  $\sigma$ VTH/VDD tolerant zigzag 8T SRAM with area-efficient decoupled differential sensing and fast write-back scheme," IEEE Symp. VLSI Circuit, Dig. Tech. Papers, pp.103–104, 2010.

- [12] E. Ibe, K. Shimbo, H. Taniguchi, and T. Toba, "Quantification and mitigation strategies of neutron induced soft-errors in CMOS devices and components," Proc. IEEE International Reliability Physics Symposium, pp.239–246, 2011.

- [13] N. Mahatme and B. Bhuva, "Analysis of multiple cell upsets due to neutrons in SRAMs for A deep-N-well process," Proc. IEEE International Reliability Physics Symposium, pp.891–896, 2011.

- [14] S. Adham and B. Nadeau-Dosite, "A BIST algorithm for bit/group write enable faults in SRAMs," Proc. IEEE International Workshop on Memory Technology, Design and Testing, pp.98–103, 2004.

- [15] "Write combining memory implementation guidelines," Order Number: 244422-001, http://download.intel.com/design/PentiumII/ applnots/24442201.pdf. Intel Corporation, Nov. 1998.

Shusuke Yoshimoto received B.E. and M.E. degrees in Computer and Systems Engineering from Kobe University, Hyogo, Japan, in 2009 and 2011, respectively. He is currently working in the doctoral course at that university. His current research is low-power and soft-error tolerant SRAM designs. He is a student member of IPSJ and IEEE.

Masaharu Terada received his B.E. degree in Computer and Systems Engineering in 2010 from Kobe University, Hyogo, Japan, where he is currently working in the M.E. course. His current research is low-power SRAM designs.

Shunsuke Okumura received his B.E. and M.E. degrees in Computer and Systems Engineering in 2008 and 2010, respectively from Kobe University, Hyogo, Japan, where he is currently working in the doctoral course. His current research is high-performance, low-power SRAM designs, dependable SRAM designs, and error correcting codes implementation. He is a student member of IPSJ and IEEE.

Toshikazu Suzuki received Ph.D., M.E. and B.E. degrees in electronic engineering from Kobe University, Kobe, Japan, in 2008, 1986, and 1984, respectively. In 1988, he joined Panasonic Corporation, Osaka, Japan. He has been engaged in the research and development of the microprocessors, analog circuits, high-density DRAMs, and embedded SRAMs. Since 2009, he has moved temporarily to the Semiconductor Technology Academic Research Center (STARC), Yokohama, Japan, and has continued

research on low-power memory circuits. He served on the Program Committee of IEEE Asian Solid-State Circuits Conference during 2008–2009.

Shinji Miyano received his B.E. and M.E. degrees in Applied Physics from The University of Tokyo, Tokyo, Japan, in 1984 and 1986, respectively. He joined Toshiba Corporation, Kawasaki, Japan, in 1986, where he has been developing GaAs IC, embedded DRAM, SRAM, and MEMS. Since 2009, he has served concurrently as a manager of memory design at Semiconductor Technology Academic Research Center. His current research interests include ultra-low-power SRAM, DRAM, and system

LSIs. He has served as a Program Committee Member for IEEE Custom Integrated Circuits Conference (CICC), and as a Guest Associate Editor of IEICE Transactions on Electronics.

Hiroshi Kawaguchi received his B.E. and M.E. degrees in Electronic Engineering from Chiba University, Chiba, Japan, in 1991 and 1993, respectively, and earned a Ph.D. degree in Engineering from The University of Tokyo, Tokyo, Japan, in 2006. He joined Konami Corporation, Kobe, Japan, in 1993, where he developed arcade entertainment systems. He moved to the Institute of Industrial Science, The University of Tokyo, as a Technical Associate in 1996, and was appointed as a Research Asso-

ciate in 2003. In 2005, he moved to Kobe University, Kobe, Japan. Since 2007, he has been an Associate Professor with the Department of Information Science at that university. He is also a Collaborative Researcher with the Institute of Industrial Science, The University of Tokyo. His current research interests include low-voltage SRAM, RF circuits, and ubiquitous sensor networks. Dr. Kawaguchi was a recipient of the IEEE ISSCC 2004 Takuo Sugano Outstanding Paper Award and the IEEE Kansai Section 2006 Gold Award. He has served as a Design and Implementation of Signal Processing Systems (DISPS) Technical Committee Member for IEEE Signal Processing Society, as a Program Committee Member for IEEE Custom Integrated Circuits Conference (CICC) and IEEE Symposium on Low-Power and High-Speed Chips (COOL Chips), and as a Guest Associate Editor of IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences and IPSJ Transactions on System LSI Design Methodology (TSLDM). He is a member of IEEE, ACM, and IPSJ.

Masahiko Yoshimoto earned his B.S. degree in Electronic Engineering from Nagoya Institute of Technology, Nagoya, Japan, in 1975, and an M.S. degree in Electronic Engineering from Nagoya University, Nagoya, Japan, in 1977. He earned a Ph.D. degree in Electrical Engineering from Nagoya University, Nagoya, Japan in 1998. He joined the LSI Laboratory, Mitsubishi Electric Corporation, Itami, Japan, in April 1977. During 1978–1983 he was engaged in the design of NMOS and CMOS static RAM

including a 64K full CMOS RAM with the world's first divided-wordline structure. From 1984, he was involved in research and development of multimedia ULSI systems for digital broadcasting and digital communication systems based on MPEG2 and MPEG4 Codec LSI core technology. Since 2000, he has been a Professor of the Department of Electrical and Electronic Systems Engineering at Kanazawa University, Japan. Since 2004, he has been a Professor of the Department of Computer and Systems Engineering at Kobe University, Japan. His current activities are research and development of multimedia and ubiquitous media VLSI systems including an ultra-low-power image compression processor and a low-power wireless interface circuit. He holds 70 registered patents. He served on the Program Committee of the IEEE International Solid State Circuit Conference during 1991-1993. Additionally, he served as a Guest Editor for special issues on Low-Power System LSI, IP, and Related Technologies of IEICE Transactions in 2004. He received R&D100 awards in 1990 and 1996 from R&D Magazine for development of the DISP and development of a real-time MPEG2 video encoder chipset, respectively.