PDF issue: 2025-12-05

# A 40-nm 256-Kb Half-Select Resilient 8T SRAM with Sequential Writing Technique

```

Yoshimoto, S.; Terada, M.; Okumura, S.; Suzuki, T.; Miyano, S.; Kawaguchi, H.; Yoshimoto, M.

```

### (Citation)

IEICE Electronics Express, 9(12):1023-1029

(Issue Date) 2012-06-20 (Resource Type)

journal article

(Version)

Version of Record

(Rights)

copyright©2012 IEICE

(URL)

https://hdl.handle.net/20.500.14094/90002977

## A 40-nm 256-Kb Half-Select Resilient 8T SRAM with Sequential Writing Technique

- S. Yoshimoto<sup>1a)</sup>, M. Terada<sup>1</sup>, S. Okumura<sup>1</sup>, T. Suzuki<sup>2</sup>, S. Miyano<sup>3</sup>, H. Kawaguchi<sup>1</sup>, and M. Yoshimoto<sup>1</sup>

- <sup>1</sup> Depratment of Information science Kobe University

- 1-1 Rokkodai, Nada-ku, Kobe, Hyogo, 657-8501, Japan

- <sup>2</sup> Panasonic Corporation, Japan

- <sup>3</sup> Semiconductor Technology Academic Research Center (STARC), Japan

- a) yoshipy@cs28.cs.kobe-u.ac.jp

**Abstract:** This paper introduces a novel half-select resilient dual write wordline 8T (DW8T) SRAM with a sequential writing technique. The dual write wordlines are sequentially activated in a write cycle, and its combination with the half-VDD precharge suppresses the half-select problem. We implemented a 256-Kb DW8T SRAM and a half-VDD generator with a 40-nm CMOS process. The measurement results of the seven samples show that the proposed DW8T SRAM achieves a VDDmin of 600 mV and improves the average VDDmin by 367 mV compared to the conventional 8T SRAM. The measured leakage power can be reduced by 25%.

**Keywords:** SRAM, 8T, disturb, half-select

**Classification:** Integrated circuits

#### References

- [1] R. Heald and P. Wang, "Variability in Sub-100 nm SRAM Designs," *Proc. International Conference on Computer Aided Design*, pp. 347–352, 2004.

- [2] M. Yamaoka, K. Osada, and T. Kawahara, "A Cell-activation-time Controlled SRAM for Low-voltage Operation in DVFS SoCs Using Dynamic Stability Analysis," *European Solid-State Circuits Conference (ES-SCIRC)*, pp. 286–289, Sept. 2008.

- [3] H. Pilo, J. Barwin, G. Braceras, C. Browning, S. Burns, J. Gabric, and M. Miller, "An SRAM Design in 65 nm and 45 nm Technology Nodes Featuring Read and Write-Assist Circuits to Expand Operating Voltage," *IEEE Symp. on VLSI Circuits*, pp. 15–16, June 2006.

- [4] Y. Morita, H. Fujiwara, H. Noguchi, Y. Iguchi, K. Nii, H. Kawaguchi, and M. Yoshimoto, "An Area-Conscious Low-Voltage-Oriented 8T-SRAM Design under DVS Environment," *IEEE Symp. on VLSI Circuits*, pp. 256–257, June 2007.

- [5] T. Suzuki, S. Moriwaki, A. Kawasumi, S. Miyano, and H. Shinohara, "0.5-V, 150-MHz, Bulk-CMOS SRAM with Suspended Bit-Line Read Scheme," European Solid-State Circuits Conference (ESSCIRC), pp. 354–357, Sept. 2010.

- [6] Y. Fujimura, O. Hirabayashi, T. Sasaki, A. Suzuki, A. Kawasumi, Y. Takeyama, K. Kushida, G. Fukano, A. Katayama, Y. Niki, and T. Yabe, "A Configurable SRAM with Constant-Negative-Level Write Buffer for Low-Voltage Operation with 0.149 μm² Cell in 32 nm High-k Metal-Gate CMOS," ISSCC, pp. 348–349, Feb. 2010.

- [7] H. Fujiwara, T. Takeuchi, Y. Otake, M. Yoshimoto, and H. Kawaguchi, "An Inter-Die Variability Compensation Scheme for 0.42-V 486-kb FD-SOI SRAM using Substrate Control," *IEEE International SOI Confer*ence, Oct. 2008.

#### 1 Introduction

CMOS technology scaling increases random and systematic variation [1]. To date, the SRAM is the most sensitive device to the variation because of its large capacity and minimum sizing [2]. The high-yield requirement for the classic 6T SRAM makes the cell size larger because the 6T cell has a tradeoff between the static noise margin (SNM) and the write noise margin (WNM) in nature [3]. Dual port 8T cells have been proposed to free the SNM/WNM tradeoff with its dedicated read port, which enables lower-voltage operation than 6T SRAMs [4]. The 8T cells, however, have a half-select problem, which is a disturbance to unselected cells in a write cycle [5]. The half-selected cell in the unselected column is disturbed because the 8T cell is usually comprised of minimum sizing transistors and the  $\beta$  ratio is one; the cell content might be flipped when the write wordline (WWL) is activated for turning on all the access gates in the horizontal direction. In this paper, a novel sequential writing technique is proposed: dual write wordlines mitigate the half-select disturbance in an 8T SRAM.

# 2 Sequential writing technique for dual write wordline 8T SRAM

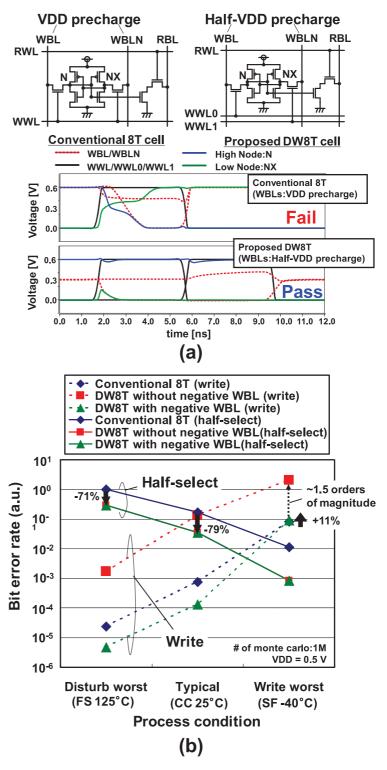

Fig. 1 (a) presents schematics of the conventional and the proposed DW8T cell and the concept of the sequential writing technique. In the proposed DW8T cell, the write bitlines (WBLs) are precharged to a half of the supply voltage (a half VDD), which decreases the disturbing currents through the WBLs. The proposed 8T cell has two WWLs: they are called "dual write wordlines" in this paper and are sequentially activated in a write cycle. The sequential writing technique eliminates one of the two disturbing currents flowing from a high-state node to WBL and from WBLN to a low-state node. Utilizing the half-VDD precharging WBLs and the dual write wordlines, the proposed scheme mitigates the half-select problem.

Fig. 1 (a) also shows waveforms of the conventional and proposed 8T cells in the half-selected situation. In a write operation, the conventional 8T cell is disturbed by the noise current from a write bitline to a low-state node. On the other hand, the proposed DW8T cell is disturbed by either of the two disturbing currents mentioned above: one is from a high-state node and the

other is to a low-state node. The proposed sequential writing technique can separate the two disturbing currents because the dual write wordlines are sequentially activated in the proposed DW8T cell. The disturbing current

Fig. 1. (a) schematics of conventional and proposed dual write wordline 8T (DW8T) cell and their waveforms and (b) simulated bit error rate of the conventional 8T SRAM, DW8T SRAM, and DW8T SRAM with negative WBLs.

in the DW8T is suppressed lower than the conventional 8T and its SNM is improved because the WBLs are precharged to a half VDD.

We investigated the SNMs in the conventional and proposed 8T cells. The proposed scheme improves the SNM to 86 mV from  $68\,\text{mV}$  ( $18\,\text{mV}=26.5\%$  improvement).

Fig. 1(b) shows the simulated bit error rates (BERs) of the conventional 8T, DW8T and DW8T with a negative WBL scheme. The both DW8Ts use the proposed sequential writing technique. The DW8T (without the negative WBL) has disadvantages in the write margin due to the proposed sequential write technique; in the write worst corner (SF,  $-40^{\circ}$ C), the write BER of the DW8T is degraded by 1.5 orders of magnitude, compare with the conventional 8T. Therefore, we adopt negative WBL scheme [6] to improve the write margin. The negative bitline level is -0.1 V (20% of VDD). The BERs of the DW8T with the negative WBLs are limited by the half-select margin at the disturb worst corner (FS, 125°C) and a typical corner (CC, 25°C), whereas at the write worst corner, its BER is indeed limited by the write margin. The DW8T improves the half-select BER by 71% at the disturb worst corner and by 79% at the typical corner over the conventional 8T, respectively. Its write BER is degraded by 11% at the write worst corner; however it is not the global worst point. The performance in terms of BER is restricted by the disturb worst corner in our design.

#### 3 Experimental results

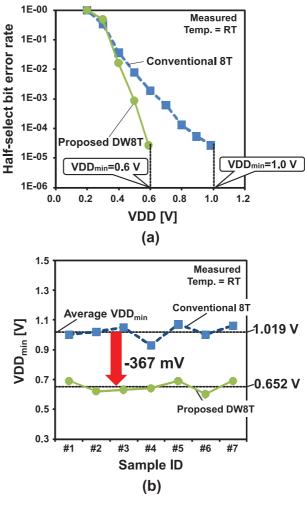

We designed a 256-Kb DW8T SRAM test chip in a 40-nm CMOS process. We also implemented half-VDD generators on the chip [7]. Each 8-Kb SRAM block has a half-VDD generator. the size of the generator is  $35 \times 5 \,\mu\text{m}^2$ . The area overhead is less than 0.5% in the 256-Kb SRAM macro. Fig. 2(a) portrays the measured half-select BERs of the conventional 8T SRAM and the proposed DW8T SRAM with the sequential writing technique on the best chip. The measurement result of the conventional 8T SRAM was obtained by reusing the proposed DW8T SRAM; the dual write wordlines are simultaneously controlled in a similar manner and the WBLs are precharged to VDD in this case. The precharge level can be changed to an arbitrary value on the test chip. The measurement results show that the proposed DW8T SRAM with the sequential writing technique can operate at a VDD<sub>min</sub> of  $0.6\,\mathrm{V}$  and can improve the  $\mathrm{VDD}_{\mathrm{min}}$  by  $0.4\,\mathrm{V}$  on the chip. By using seven test chips, we also measured the VDD<sub>min</sub>'s of the conventional 8T SRAM and the proposed DW8T SRAM. Fig. 2(b) shows the data from the seven samples. The number six is the best chip mentioned above. The  $VDD_{min}$  is improved by 367 mV (from 1.019 V to 0.652 V) on average in the proposed DW8T SRAM.

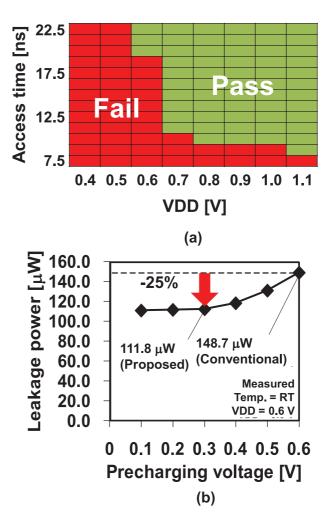

Fig. 3 (a) portrays a Shmoo plot of the access time and VDD. The operation is restricted by a read operation rather than the write operation. So, we confirmed that the proposed scheme does not affect its access time although the proposed DW8T has the dual write wordlines to be sequentially

activated. The best chip can operate at an access time of  $20.0\,\mathrm{ns}$  even when the VDD is  $0.6\,\mathrm{V}$ . The access time at the nominal VDD of  $1.1\,\mathrm{V}$  is  $8.5\,\mathrm{ns}$ .

The leakage power was measured in the standby mode as shown in Fig. 3 (b). The VDD and the operating frequency were set to  $0.6\,\mathrm{V}$  and  $10\,\mathrm{MHz}$ , respectively. In the figure, the precharging voltage on the WBLs are changed to a half VDD (=  $0.3\,\mathrm{V}$ ) in the proposed scheme. The leakage power is decreased by 25%, compared with the conventional 8T SRAM. The leakage power is decreased with a precharging voltage because bitline leakage is accordingly reduced.

We also investigated area overheads; the proposed 8T SRAM requires an additional WWL and an extra driver for it to implement the sequential writing technique. The additional WWL can be laid out without any area overhead in the given process, whereas the extra WWL driver occupied some area. The area overhead for the extra WWL driver is, however, small because it merely drives either of the access gates in the proposed DW8T cell and the capacitance is small (usually, the conventional SRAM drives the two access

**Fig. 2.** (a) Die photograph of the test chip, (b) measured half-select BERs (best chip), and (c) measured VDD<sub>min</sub>'s of the conventional 8T SRAM and the proposed DW8T SRAM using 7 chips.

**Fig. 3.** (a) Shmoo plot and (b) measured leakage power in the proposed DW8T SRAM when a precharging voltage is changed.

gates, which has to be designed twice larger). Consequently, the area overhead for the dual write wordline drivers is only 2.3% in the SRAM macro. The area overhead derived from the negative WBL scheme is 2%. The proposed DW8T cell area is  $0.6679\,\mu\mathrm{m}^2$  on a logic rule basis, which is 21% larger than the classic 6T cell (the same size as that of the conventional 8T cell).

#### 4 Summary

In this paper, we proposed a novel DW8T SRAM with the sequential writing technique that can mitigate the half-select problem. The proposed sequential writing technique further eliminates one of the two disturb currents, which improves the half-select margin better. DW8T with sequential writing technique improves the half-select BERs by 71% at the disturb worst corner and 79% at the typical corner compared with the conventional 8T, respectively. We implemented the 256-Kb DW8T SRAM macro and the half-VDD generator on a single chip in a 40-nm CMOS process. The measured output voltage of the half-VDD generator shows good dependence on the VDD from  $0.2\,\mathrm{V}$  to  $1.1\,\mathrm{V}$  within an error of  $-45\,\mathrm{mV}$  to  $+35\,\mathrm{mV}$ . The VDD<sub>min</sub> of the

proposed 256-Kb DW8T SRAM is improved by  $367\,\mathrm{mV}$  on average among seven sample chips. The best chip operates at a VDD<sub>min</sub> of  $600\,\mathrm{mV}$ . The proposed half-VDD precharging WBLs improves the leakage power by 25%, compared with the conventional 8T SRAM.

### **Acknowledgments**

This work was carried out as a part of the Extremely Low Power (ELP) project supported by the Ministry of Economy, Trade and Industry (METI) and the New Energy and Industrial Technology Development Organization (NEDO).

© IEICE 2012 DOI: 10.1587/elex.9.1023 Received March 29, 2012 Accepted May 16, 2012 Published June 20, 2012