PDF issue: 2025-12-05

# Application of pentacene thin-film transistors with controlled threshold voltages to enhancement/depletion inverters

Takahashi, Hajime Hanafusa, Yuki Kimura, Yoshinari Kitamura, Masatoshi

### (Citation)

Japanese Journal of Applied Physics, 57(3):03EH03-03EH03

# (Issue Date)

2018-03

# (Resource Type)

journal article

### (Version)

Accepted Manuscript

### (Rights)

© 2018 The Japan Society of Applied Physics.

本著作物の利用は,私的利用(著作権法第30条)および引用(著作権法第32条)の範囲内に限られる

### (URL)

https://hdl.handle.net/20.500.14094/90004872

Application of pentacene thin-film transistors with controlled threshold voltages

to enhancement/depletion inverters

Hajime Takahashi, Yuki Hanafusa, Yoshinari Kimura, and Masatoshi Kitamura\*

Department of Electrical and Electronic Engineering, Graduate School of Engineering,

Kobe University, Kobe 657-8501, Japan

Oxygen plasma treatment has been carried out to control the threshold voltage in organic

thin-film transistors (TFTs) having a SiO<sub>2</sub> gate dielectric prepared by rf sputtering. The

threshold voltage linearly changed in the range of -3.7 to 3.1 V with the increase in plasma

treatment time. Although the amount of change is smaller than that for organic TFTs having

thermally grown SiO<sub>2</sub>, the tendency of the change was similar to that for thermally grown SiO<sub>2</sub>.

To realize different plasma treatment times on the same substrate, a certain region on the SiO<sub>2</sub>

surface was selected using a shadow mask, and was treated with oxygen plasma. Using the

process, organic TFTs with negative threshold voltages and those with positive threshold

voltages were fabricated on the same substrate. As a result, enhancement/depletion inverters

consisting of the organic TFTs operated at supply voltages of 5 to 15 V.

\*E-mail: kitamura@eedept.kobe-u.ac.jp

1

### 1. Introduction

Organic thin-film transistors (TFTs) have been intensively studied toward their application to flexible, large-area, light-weight, and low-cost electronic devices.<sup>1-4)</sup> The performance of organic TFTs including field-effect mobilities has been progressing for over ten years.<sup>5-7)</sup> From the progress of the performance in organic TFTs, it is expected that organic TFTs are practically applied to logic circuits<sup>8-12)</sup> and active matrix displays.<sup>13-20)</sup> Threshold voltage control is an important issue for such applications of organic TFTs.

The threshold voltage in metal-oxide-semiconductor field-effect transistors (MOSFETs) including organic TFTs is affected by the work functions of the gate electrodes and the semiconductor, charges in the gate dielectric, and dipole on the interface between the gate dielectric and the semiconductor. Also, the voltage applied to an additional gate 24,25 and the parasitic resistance 26,27 change the threshold voltage. Some groups have demonstrated threshold voltage control in organic TFTs on the basis of these phenomena. Oxygen plasma and UV ozone treatments 29-31 have been conducted to obtain a hydrophilic surface as pretreatment for gate dielectrics in organic TFTs. Such a treatment causes excess charges on or close to the surface of the gate dielectric. Thus, it is possible that such a treatment is used for threshold voltage control. In fact, oxygen plasma treatment leads to the change in threshold voltage in organic TFTs.

We have demonstrated the control of the threshold voltage in pentacene<sup>36)</sup> and dinaphthothienothiophene (DNTT)<sup>37)</sup> TFTs fabricated on Si substrates with thermally grown SiO<sub>2</sub> using oxygen plasma treatment to the surface of the gate dielectric. The threshold voltage linearly changed in the range from -6.4 to 9.4 V with the increase in the plasma treatment time.<sup>37)</sup> The relationship between the threshold voltage and the plasma treatment time is important for the design of actual circuits. In addition, p-channel organic TFTs having a negative or a positive threshold voltage serve as an enhancement- or a depletion-type PMOS, respectively. When p-channel organic TFTs having a negative threshold voltage are used for

logic circuit, four TFTs are required for constructing a stably operating inverter.<sup>38,39)</sup> On the other hand, the use of enhancement- and depletion-type PMOS enables the construction of an inverter consisting of two PMOSs known as an enhancement/depletion (E/D) inverter.

In actual work, we have used DNTT TFTs having different threshold voltages fabricated on Si substrates for E/D inverters.<sup>37)</sup> The E/D inverter operated at supply voltages of 5 to 20 V. However, the E/D inverter was constructed by externally connecting DNTT TFTs fabricated on different substrates. In addition, use of a silicon substrate having thermally grown SiO<sub>2</sub> is not suitable for practical application. Thus, it is necessary to clarify whether this method of threshold voltage control is applicable to organic TFTs having other gate dielectrics instead of thermally grown SiO<sub>2</sub>.

In this paper, we report the characteristics of pentacene TFTs having a SiO<sub>2</sub> gate dielectric fabricated on glass substrates. The SiO<sub>2</sub> gate dielectric for the TFT was deposited by rf sputtering, and the surface was treated with oxygen plasma for control of the threshold voltage. We investigated the dependence of the threshold voltage in the TFT on treatment time. The treatment time for a TFT applied to a logic inverter was determined on the basis of the investigation. The characteristics of logic inverters consisting of TFTs having a threshold voltage adjusted are shown to evaluate the effectiveness of the threshold voltage control.

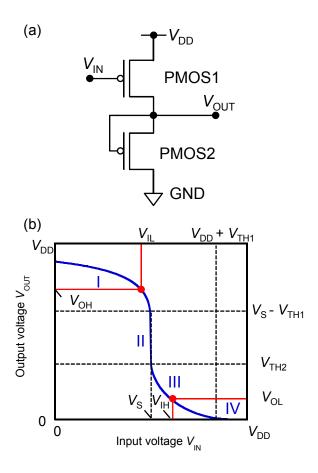

### 2. Enhancement/depletion inverters

Figure 1(a) shows the circuit for an E/D inverter consisting of an enhancement-type PMOS1 and a depletion-type PMOS2. In general, PMOS1 and PMOS2 have negative and positive threshold voltages, respectively. Figure 1(b) shows the ideal output characteristic for an E/D inverter, which is classified into four regions: I, II, III, and IV. The output voltage  $V_{\rm OUT}$  can be given by

$$V_{\text{OUT}} = \begin{cases} V_{\text{IN}} - V_{\text{TH1}} + \left[ (V_{\text{IN}} - V_{\text{DD}} - V_{\text{TH1}})^2 - \frac{\beta_2}{\beta_1} V_{\text{TH2}}^2 \right]^{\frac{1}{2}}, & \text{for } 0 \le V_{\text{IN}} \le V_{\text{S}}, \\ \text{an indefinite value between } V_{\text{TH2}} \text{ and } V_{\text{S}} - V_{\text{TH1}}, & \text{for } V_{\text{IN}} = V_{\text{S}}, \\ V_{\text{TH2}} - \left[ V_{\text{TH2}}^2 - \frac{\beta_1}{\beta_2} (V_{\text{IN}} - V_{\text{DD}} - V_{\text{TH1}})^2 \right]^{\frac{1}{2}}, & \text{for } V_{\text{S}} \le V_{\text{IN}} \le V_{\text{DD}} + V_{\text{TH1}}, \\ 0, & \text{for } V_{\text{DD}} + V_{\text{TH1}} \le V_{\text{IN}} \le V_{\text{DD}}, \end{cases}$$

$$(1)$$

as a function of the input voltage  $V_{\rm IN}$  under a supply voltage  $V_{\rm DD}$ . Here,  $\beta_i = \mu_i \ C_{\rm OX} \ W_i/L_i$  (i=1 or 2),  $\mu_i$  is the field-effect mobility,  $C_{\rm OX}$  is the gate capacitance per unit area,  $W_i$  is the channel width,  $L_i$  is the channel length, and  $V_{\rm TH}_i$  is the threshold voltage for PMOS1 or PMOS2. Equation (1) can be derived from the standard equation of drain current in the quadratic model for MOSFETs.  $V_{\rm S}$  is defined as

$$V_{\rm S} = V_{\rm DD} + V_{\rm TH1} - \sqrt{\frac{\beta_2}{\beta_1}} V_{\rm TH2} \,,$$

(2)

and represents the switching voltage for the inverter. Since  $V_{\text{OUT}}$  has an indefinite value at  $V_{\text{IN}} = V_{\text{S}}$ , the input-output gain,  $dV_{\text{OUT}}/dV_{\text{IN}}$ , is minus infinity at the input voltage. In contrast to a CMOS inverter,  $V_{\text{OUT}}$  for the E/D inverter is not equal to  $V_{\text{DD}}$  when  $V_{\text{IN}} = 0$  as seen in Fig. 1(b).

The low  $(NM_L)$  and high  $(NM_H)$  noise margins are defined as  $NM_L = V_{IL} - V_{OL}$  and  $NM_H = V_{OH} - V_{IH}$ , respectively. Here,  $V_{IL}$  or  $V_{IH}$  is an input voltage when  $dV_{OUT}/dV_{IN} = -1$ , and  $V_{OH}$  or  $V_{OL}$  is an output voltage at  $V_{IN} = V_{IL}$  or  $V_{IH}$ , as shown in Fig. 1(b). From Eq. (1),  $NM_L$  and  $NM_H$  are expressed as

$$NM_{\rm L} = V_{\rm DD} + V_{\rm TH1} + \left(\frac{1}{\sqrt{1+\gamma}} - 1 - 2\sqrt{\frac{\gamma}{3}}\right) V_{\rm TH2},$$

(3)

$$NM_{\rm H} = -V_{\rm TH1} + \left(\frac{\gamma}{\sqrt{1+\gamma}} - \sqrt{\frac{\gamma}{3}}\right)V_{\rm TH2},\tag{4}$$

where  $\gamma = \beta_2/\beta_1$ . Equations (2)-(4) were used for the evaluation of fabricated E/D inverters.

### 3. Experimental methods

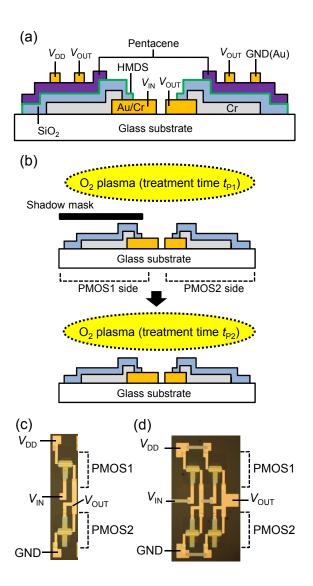

Figures 2(a) and 2(b) show the cross section of the pentacene TFTs examined and the illustration of the oxygen plasma treatment adopted in this study, respectively. The pentacene TFTs were prepared on glass substrates. The fabrication process of the pentacene TFTs is as follows. First, a Au layer with a Cr adhesive layer was deposited on a glass substrate for lines connecting between terminals of TFTs. After that, a Cr gate layer was deposited on the glass substrate by thermal evaporation. Then, a SiO<sub>2</sub> gate dielectric was deposited by rf sputtering using a SiO<sub>2</sub> target. The SiO<sub>2</sub> gate dielectric had a unit area capacitance of about 25 nF/cm<sup>2</sup>, which corresponds to a thickness of about 150 nm. The SiO<sub>2</sub> surface was treated with oxygen plasma. The AC power for plasma generation was set at 5.4 W. The condition for the plasma treatment is similar to that reported in Ref. 36. For the fabrication of E/D inverters, the area for PMOS2 was exposed to the plasma through a shadow mask for a time  $t_{P1}$ , and the entire area was exposed for a time  $t_{P2}$  as shown in Fig. 2(b). Thus, the treatment time  $t_P$  is equal to  $t_{P2}$  for PMOS1, and  $(t_{P1}+t_{P2})$  for PMOS2. For a reference transistor, UV/ozone treatment was performed instead of oxygen plasma treatment. UV/ozone treatment can be expected to have no large influence on threshold voltage. After the second plasma or UV/ozone treatment, the substrate was immediately exposed to hexamethyldisilazane (HMDS) vapor to obtain a hydrophobic surface. A 45-nm-thick pentacene was deposited on the SiO<sub>2</sub> surface, and a Au layer was deposited for drain/source electrodes. The channel width was 600 µm, and the channel length was 40 µm. The deposition processes were performed at room temperature, and all layers deposited were patterned by the use of shadow masks. The maximum temperature in the fabrication process is 120 °C for the HMDS treatment. Figures 2(c) and 2(d) show photographs of an E/D inverter and a circuit consisting of two E/D inverters, respectively. The characteristics of pentacene TFTs and circuits were examined in a dry-nitrogen glovebox at room temperature using a semiconductor parameter analyzer.

### 4. Transistor characteristics

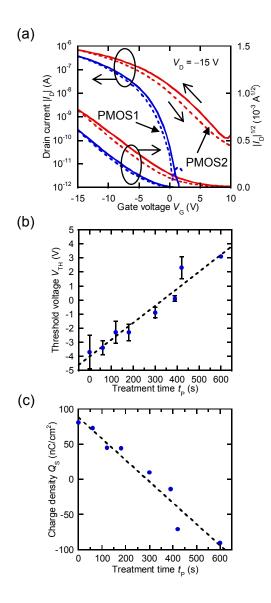

Figure 3(a) shows the transfer characteristics of typical pentacene TFTs serving as PMOS1 and PMOS2 in an E/D inverter in the saturation regime at a drain voltage ( $V_D$ ) of -15 V. Plasma treatment time was 60 s for the PMOS1 and 420 s for the PMOS2. The PMOS1 had a threshold voltage of -3.7 V, and worked as an enhancement-type transistor. On the other hand, the PMOS2 has a threshold voltage of 1.2 V, and worked as a depletion-type transistor. The field-effect mobilities for both transistors were about 0.01 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The value is relatively low in pentacene TFTs. The fabrication process including pretreatment for the glass substrate has not been optimized. The surface roughness of SiO<sub>2</sub> deposited on such a glass substrate may cause the low mobility. In fact, the pentacene layer had a small grain structure with a diameter of about 200 nm. Although the field-effect mobility is low, the result shown in Fig. 3(a) suggests that the plasma treatment is effective for threshold voltage control to SiO<sub>2</sub> gate dielectrics prepared by rf sputtering.

Threshold voltages of pentacene TFTs for  $t_P$  in the range of 60 to 600 s are summarized in Fig. 3(b). The pentacene TFTs for  $t_P$  of 60 to 180 s were used for PMOS1, and the pentacene TFTs for  $t_P$  of 300 to 600 s were used for PMOS2. The data at  $t_P = 0$  represents the threshold voltage of pentacene TFTs having SiO<sub>2</sub> gate dielectrics treated by UV/ozone. The result indicates that UV/ozone treatment does not affect the threshold voltage. The threshold voltage linearly shifts to positive voltages with respect to plasma treatment time. The line fitting to experimental data is expressed as  $V_{TH} = (0.012 \text{ V/s}) t_P - 4.0 \text{ V}$ . As a result, the threshold voltage changed in the range of -3.7 to 3.1 V under the condition that SiO<sub>2</sub> gate dielectrics are treated by UV/ozone and by oxygen plasma for  $t_P$  in the range of 60 to 600 s.

The threshold voltage change can be explained by the generation of negative charges on or close to the surface of the SiO<sub>2</sub> gate dielectric. Under some assumptions, the negative charges are calculated from the following equation for the threshold voltage of organic TFTs:

$$V_{\rm TH} = \frac{\Phi_{\rm M} - \Phi_{\rm S}}{e} - \frac{1}{C_{\rm OX}} Q_{\rm S},\tag{5}$$

where e is the electron elementary charge,  $\Phi_{\rm M}$  and  $\Phi_{\rm S}$  are the work functions of the gate electrode and the organic semiconductor, respectively, and  $Q_{\rm S}$  is the surface charge density at the interface between the gate dielectric and the semiconductor. Here, it is assumed that the surface charge is dominant as compared with the charge inside the gate dielectric. By using  $\Phi_{\rm M}=4.5~{\rm eV}$  for Cr gate<sup>40)</sup> and  $\Phi_{\rm S}=5.0~{\rm eV}$  for pentacene<sup>6)</sup>, an experimental  $Q_{\rm S}$  value is calculated by substituting an experimental  $V_{\rm TH}$  value into

$$Q_{\rm S} = C_{\rm OX} \left( \frac{\Phi_{\rm M} - \Phi_{\rm S}}{e} - V_{\rm TH} \right). \tag{6}$$

Figure 3(c) shows experimental  $Q_S$  values calculated for  $V_{TH}$  values in Fig. 3(b). In this study, it is assumed that the dependence of  $Q_S$  on  $t_P$  is expressed as

$$Q_{\mathcal{S}} = Q_0 + q_{\mathcal{P}} t_{\mathcal{P}},\tag{7}$$

where  $Q_0$  is the intrinsic surface charge density and  $q_P$  is the surface charge density per unit time induced by plasma treatment. By fitting a line to  $Q_S$  in Fig. 3(c),  $Q_0$  and  $q_P$  are estimated to be 81.2 nC cm<sup>-2</sup> and -0.30 nC cm<sup>-2</sup> s<sup>-1</sup>, respectively. We have reported  $q_P$  values of -0.76 nC cm<sup>-2</sup> s<sup>-1</sup> for DNTT TFTs and -3.1 nC cm<sup>-2</sup> s<sup>-1</sup> for pentacene TFTs. The pentacene and DNTT TFTs were fabricated on Si substrates with thermally grown SiO<sub>2</sub> treated at an AC power of 5.8 W. The AC power is close to that for SiO<sub>2</sub> prepared by rf sputtering in this study. However, the absolute value of  $q_P$  estimated in this study, 0.30 nC cm<sup>-2</sup> s<sup>-1</sup>, is quite small as compared with those of previous reports. The difference suggests that a SiO<sub>2</sub> surface prepared by rf sputtering is not easily affected by oxygen plasma treatment as compared with a surface of thermally grown SiO<sub>2</sub>. The reason has been under investigation.

### 5. Inverter characteristics

Enhancement/depletion inverters were fabricated as an application of pentacene TFTs having

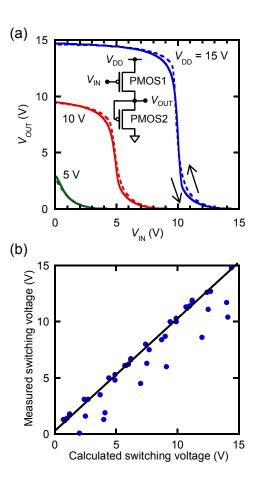

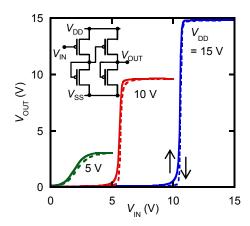

controlled threshold voltages. To fabricate inverters on a glass substrate, the two-step oxygen plasma treatment explained in Sect. 3 was adopted. Figure 4(a) shows the input-output characteristics of an E/D inverter consisting of two pentacene TFTs whose transfer characteristics are shown in Fig. 3(a). The characteristics, which were measured at  $V_{\rm DD} = 5$ , 10, and 15 V, have no large hysteresis in forward and reverse sweeps. The input-output characteristics for  $V_{\rm DD} = 10$  and 15 V exhibited typical transfer characteristics of an inverter circuit having noise margins. The characteristics for the E/D inverter are summarized in Table I. The value of  $NM_{\rm L}$  increases with  $V_{\rm DD}$ , and the value of  $NM_{\rm H}$  has no dependence on  $V_{\rm DD}$ . The increases in  $NM_{\rm L}$  and the unchanged in  $NM_{\rm H}$  can be explained by Eqs. (3) and (4), respectively. From the transfer characteristics in Fig. 4(a), the measured switching voltages for  $V_{\rm DD} = 5$ , 10, and 15 V were 0.3, 4.8, and 10.0 V, respectively. On the other hand, the switching voltages for  $V_{\rm DD} = 5$ , 10, and 15 V were calculated to be -0.1, 4.9, and 9.9 V, respectively. The values were calculated using the mobilities and threshold voltages for the individual TFTs. The measured switching voltages are close to calculated values.

To confirm the reproducibility, the measured and calculated switching voltages of sixteen E/D inverters are shown in Fig. 4(b). For an E/D inverter, three plots for  $V_{\rm DD}$  = 5, 10, and 15 V are shown. Pentacene TFTs with various  $t_{\rm P}$  values were used for the inverters. The  $t_{\rm P}$  values were 0–180 s for PMOS1 and 300–600 s for PMOS2. By substituting measured mobilities and threshold voltages into Eq. (2), the calculated switching voltage was calculated. Since the gate electrode of PMOS2 for E/D inverters was connected to the source electrode of the PMOS2, the transfer characteristics of the PMOS2 cannot be directly measured. Thus, a pentacene TFT fabricated in the area for PMOS2 on the same substrate was measured for the evaluation of mobility and threshold voltage used for calculated switching voltage. The plots of three or four inverters are slightly far from a line representing a correspondence between the measured and calculated values. This is probably due to the non-uniformity in mobilities and threshold voltage on the same substrate. On the other hand, the plots for many inverters are

close to the line. The correspondence between the measured and calculated values is useful for deciding the plasma treatment time for individual TFTs used in a circuit.

The characteristics of a two-stage inverter were measured as the next step for application to a large-scale circuit. Figure 5 shows the input-output characteristics of a two-stage inverter. The  $t_P$  values were 60 s for PMOS1 and 420 s for PMOS2. The circuits operated at  $V_{\rm DD} = 5$ , 10, and 15 V and exhibited typical input-output characteristics for a two-stage inverter. Switching voltages, maximum gain, and noise margin of the first-stage inverter, second stage inverter, and two-stage inverter are summarized in Table II. The maximum gain of the two-stage inverter is larger than those of the individual inverters. This is a feature of a multi-stage inverter. The increase in the gain leads to the increase in the noise margin. As a result, the two-stage inverter has noise margin larger than those of the individual inverters.

### 6. Summary

We investigated the effect of oxygen plasma treatment on the characteristics of pentacene TFTs having a SiO<sub>2</sub> gate dielectric prepared by rf sputtering. The threshold voltage linearly changed in the range of -3.7 to 3.1 V with the increase in plasma treatment time. We fabricated enhancement- and depletion-type pentacene TFTs on the same substrate by two-step oxygen plasma treatment. The fabrication process was applied for the construction of logic inverter circuits. The E/D inverters operated at supply voltages of 5 to 15 V, and exhibited switching voltage close to an expected value. The threshold voltage control in organic TFTs by oxygen plasma treatment will be applicable to circuits consisting of more TFTs.

### Acknowledgement

This work was supported by a Grant-in-Aid for Scientific Research, Challenging Research (Pioneering), Grant Number 17H06229.

- 1) T. Sekitani and T. Someya, Jpn. J. Appl. Phys. **51**, 100001 (2012).

- 2) H. T. Yi, M. M. Payne, J. E. Anthony, and V. Podzorov, Nat. Commun. 5, 4147 (2014).

- 3) K. Fukuda, Y. Takeda, Y. Yoshimura, R. Shiwaku, L. T. Tran, T. Sekine, M. Mizukami, D. Kumaki, and S. Tokito, Nat. Commun. **3**, 1259 (2012).

- 4) D. M. Taylor, Jpn. J. Appl. Phys. 55, 02BA01 (2016).

- 5) M. Kitamura and Y. Arakawa, J. Phys.: Condens. Matter 20, 184011 (2008).

- 6) K. Takimiya, S. Shinamura, I. Osaka, and E. Miyazaki, Adv. Mater. 23, 4347 (2011).

- 7) H. Sirringhaus, Adv. Mater. 26, 1319 (2014).

- 8) P. F. Baude, D. A. Ender, M. A. Haase, T. W. Kelley, D. V. Muyres, and S. D. Theiss, Appl. Phys. Lett. **82**, 3964 (2003).

- 9) D. Bode, K. Myny, B. Verreet, B. van der Putten, P. Bakalov, S. Steudel, S. Smout, P. Vicca, J. Genoe, and P. Heremans, Appl. Phys. Lett. **96**, 133307 (2010).

- 10) M. Kitamura, Y. Kuzumoto, S. Aomori, and Y. Arakawa, Appl. Phys. Express 4, 051601 (2011).

- K.-J. Baeg, S.-W. Jung, D. Khim, J. Kim, D.-Y. Kim, J. B. Koo, J. R. Quinn, A. Facchetti,

I.-K. You, and Y.-Y. Noh, Org. Electron. 14, 1407 (2013).

- 12) M. Kondo, T. Uemura, T. Matsumoto, T. Araki, S. Yoshimoto, and T. Sekitani, Appl. Phys. Express **9**, 061602 (2016).

- 13) P. Mach, S. J. Rodriguez, R. Nortrup, P. Wiltzius, and J. A. Rogers, Appl. Phys. Lett. 78, 3592 (2001).

- 14) C. D. Sheraw, L. Zhou, J. R. Huang, D. J. Gundlach, T. N. Jackson, M. G. Kane, I. G. Hill, M. S. Hammond, J. Campi, B. K. Greening, J. Francl, and J. West, Appl. Phys. Lett. **80**, 1088 (2002).

- 15) Y. Fujisaki, H. Sato, T. Takei, T. Yamamoto, H. Fujikake, S. Tokito, and T. Kurita, J. Soc. Inf. Disp. 16, 1251 (2008).

- 16) M. Kitamura, T. Imada, and Y. Arakawa, Appl. Phys. Lett. 83, 3410 (2003).

- 17) M. Kitamura, T. Imada, and Y. Arakawa, Jpn. J. Appl. Phys. 42, 2483 (2003).

- 18) L. Zhou, S. Park, B. Bai, J. Sun, S.-C. Wu, T. N. Jackson, S. Nelson, D. Freeman, and Y. Hong, IEEE Electron Device Lett. **26**, 640 (2005).

- 19) L. Zhou, A. Wanga, S.-C. Wu, J. Sun, S. Park, and T. N. Jackson, Appl. Phys. Lett. 88, 083502 (2006).

- 20) M. Mizukami, S. Oku, S.-I. Cho, M. Tatetsu, M. Abiko, M. Mamada, T. Sakanoue, Y. Suzuri, J. Kido, and S. Tokito, IEEE Electron Device Lett. **36**, 841 (2015).

- 21) S. Kobayashi, T. Nishikawa, T. Takenobu, S. Mori, T. Shimoda, T. Mitani, H. Shimotani, N. Yoshimoto, S. Ogawa, and Y. Iwasa, Nat. Mater. **3**, 317 (2004).

- 22) K. P. Pernstich, S. Haas, D. Oberhoff, C. Goldmann, D. J. Gundlach, B. Batlogg, A. N. Rashid, and G. Schitter, J. Appl. Phys. **96**, 6431 (2004).

- 23) J. E. McDermott, M. McDowell, I. G. Hill, J. Hwang, A. Kahn, S. L. Bernasek, and J. Schwartz, J. Phys. Chem. A 111, 12333 (2007).

- 24) S. Iba, T. Sekitani, Y. Kato, T. Someya, H. Kawaguchi, M. Takamiya, T. Sakurai, and S. Takagi, Appl. Phys. Lett. **87**, 023509 (2005).

- 25) K. Hizu, T. Sekitani, T. Someya, and J. Otsuki, Appl. Phys. Lett. 90, 093504 (2007).

- 26) R. Schroeder, L. A. Majewski, and M. Grell, Appl. Phys. Lett. 83, 3201 (2003).

- 27) M. Kitamura, Y. Kuzumoto, S. Aomori, M. Kamura, J. H. Na, and Y. Arakawa, Appl. Phys. Lett. **94**, 083310 (2009).

- 28) S. C. Lim, S. H. Kim, J. H. Lee, M. K. Kim, D. J. Kim, and T. Zyung, Synth. Met. **148**, 75 (2005).

- 29) D. Guo, S. Entani, S. Ikeda, and K. Saiki, Chem. Phys. Lett. 429,124 (2006).

- 30) M. Kitamura, Y. Kuzumoto, M. Kamura, S. Aomori, J. H. Na, and Y. Arakawa, Phys. Status Solidi C 5, 3181 (2008).

- 31) Y. Ito, A. A. Virkar, S. Mannsfeld, J. H. Oh, M. Toney, J. Locklin, and Z. Bao, J. Am. Chem. Soc. **131**, 9396 (2009).

- 32) M. W. Lee and C. K. Song, Jpn. J. Appl. Phys. 42, 4218 (2003).

- 33) A. Wang, I. Kymissis, V. Bulović, and A. I. Akinwande, IEEE Electron Device Lett. **53**, 9 (2006).

- 34) A. Wang, I. Kymissis, V. Bulović, and A. I. Akinwande, Appl. Phys. Lett. 89, 112109 (2006).

- 35) K. Fukuda, T. Sekitani, U. Zschieschang, H. Klauk, K. Kuribara, T. Yokota, T. Sugino, K. Asaka, M. Ikeda, H. Kuwabara, T. Yamamoto, K. Takimiya, T. Fukushima, T. Aida, M. Takamiya, T. Sakurai, and T. Someya, Adv. Funct. Mater. **21**, 4019 (2011).

- 36) Y. Kimura, M. Kitamura, A. Kitani, and Y. Arakawa, Jpn. J. Appl. Phys. **55**, 02BB14 (2016).

- 37) A. Kitani, Y. Kimura, M. Kitamura, and Y. Arakawa, Jpn. J. Appl. Phys. 55, 03DC03 (2016).

- 38) K. Fukuda, T. Sekitani, T. Yokota, K. Kuribara, T.-C. Huang, T. Sakurai, U. Zschieschang, H. Klauk, M. Ikeda, H. Kuwabara, T. Yamamoto, K. Takimiya, K.-T. Cheng, and T. Someya, IEEE Electron Device Lett. **32**, 10 (2011).

- 39) T. Yokota, T. Sekitani, T. Tokuhara, N. Take, U. Zschieschang, H. Klauk, K. Takimiya, T.-C. Huang, M. Takamiya, T. Sakurai, and T. Someya, IEEE Trans. Electron Devices **59**, 12 (2012). 40) H. B. Michaelson, J. Appl. Phys. **48**, 4729 (1977).

## **Figure Captions**

Fig. 1. (Color online) (a) Circuit of an E/D inverter constructed using two PMOSs.

(b) Typical input-output characteristics of an E/D inverter for explaining switching voltage and noise margin.

**Fig. 2.** (Color online) (a) Cross section of a fabricated E/D inverter consisting of pentacene TFTs. (b) Schematic illustration of two-step oxygen plasma treatment. (c) Photograph of a fabricated E/D inverter. (d) Photograph of a fabricated two-stage E/D inverter.

**Fig. 3.** (Color online) (a) Transfer characteristics of enhancement- and depletion-type pentacene TFTs used for an E/D inverter. (b) Dependence of threshold voltages in pentacene TFTs on plasma treatment time for the SiO<sub>2</sub> surface. (c) Charge densities depending on plasma treatment time estimated from measured threshold voltages.

**Fig. 4.** (Color online) (a) Input/output characteristics of an E/D inverter measured at  $V_{\rm DD} = 5$ , 10, and 15 V. (b) Relationship between measured switching voltages and calculated switching voltages.

Fig. 5. (Color online) Input/output characteristics of a two-stage inverter circuit measured at  $V_{\rm DD} = 5$ , 10, and 15 V.

**Table I.** Switching voltages, maximum gain, and noise margin of the inverter consisting of PMOS1 with  $V_{\rm TH1} = -3.7$  V and PMOS2 with  $V_{\rm TH2} = 1.2$  V.

| V <sub>DD</sub> (V) | Measured $V_{\rm S}$ (V) | Calculated $V_{\rm S}$ (V) | Maximum<br>gain | NM <sub>H</sub> (V) | NM <sub>L</sub> (V) |

|---------------------|--------------------------|----------------------------|-----------------|---------------------|---------------------|

| 5                   | 0.3                      | -0.1                       | -2.2            | -                   | -                   |

| 10                  | 4.8                      | 4.9                        | -9.5            | 2.3                 | 2.8                 |

| 15                  | 10.0                     | 9.9                        | -19.0           | 2.3                 | 7.7                 |

**Table II.** Switching voltages, maximum gain, and noise margin of first-stage inverter, second-stage inverter, and two-stage inverter.

|                       | Measured $V_{\rm S}$ (V) | Maximum<br>gain | NM <sub>H</sub> (V) | NM <sub>L</sub> (V) |

|-----------------------|--------------------------|-----------------|---------------------|---------------------|

| First-stage inverter  | 11.0                     | -19.3           | 0.6                 | 8.7                 |

| Second-stage inverter | 10.0                     | -18.2           | 2.4                 | 7.9                 |

| Two-stage inverter    | 10.6                     | 47.4            | 4.9                 | 10.5                |

Figure 1 H. Takahashi et Al.

Figure 2 H. Takahashi et Al.

Figure 3 H. Takahashi et Al.

Figure 4 H. Takahashi et Al.

Figure 5 H. Takahashi et Al.