PDF issue: 2025-12-05

An 11.8 nA ultra-low power active diode using a hysteresis common gate comparator for low-power energy harvesting systems

Matsumoto, Kaori ; Asano, Hiroki ; Nakazawa, Yuichiro ; Kuroki, Nobutaka ; Numa, Masahiro ; Maida, Osamu ; Kanemoto, Daisuke ; Hirose,...

(Citation)

IEICE Electronics Express, 17(11):20200103-20200103

(Issue Date) 2020-06-10

(Resource Type)

journal article

(Version)

Version of Record

(Rights)

© 2020 The Institute of Electronics, Information and Communication Engineers

(URL)

https://hdl.handle.net/20.500.14094/90007324

# An 11.8 nA ultra-low power active diode using a hysteresis common gate comparator for low-power energy harvesting systems

Kaori Matsumoto<sup>1, a)</sup>, Hiroki Asano<sup>1</sup>, Yuichiro Nakazawa<sup>1</sup>, Nobutaka Kuroki<sup>1</sup>, Masahiro Numa<sup>1</sup>, Osamu Maida<sup>2</sup>, Daisuke Kanemoto<sup>2</sup>, and Tetsuya Hirose<sup>2, b)</sup>

Abstract This paper proposes an ultra-low power active diode (ADIO) using a hysteresis common gate comparator for low-voltage and low-power energy harvesting systems. The proposed ADIO consists of a MOS switch and hysteresis common gate comparator, which eliminates unwanted ripple and noise voltages. The hysteresis comparator controls the MOS switch to turn ON or OFF, depending on the input and output voltages. The hysteresis voltages of the comparator can be controlled by the current flowing in the comparator. The measurement results demonstrated that the hysteresis comparator had  $-26~{\rm and}~25~{\rm mV}$  hysteresis voltages and the ADIO using the hysteresis comparator eliminated unwanted ripple voltage. The maximum current consumption of our ADIO was 11.8 nA.

**Keywords:** IoT, energy harvesting, active diode, hysteresis comparator, low-power, low voltage

Classification: Integrated circuits (memory, logic, analog, RF, sensor)

#### 1. Introduction

In this paper, we propose an ultra-low power active diode (ADIO) circuit that is used for the reverse current protection in energy harvesting systems.

Energy harvesting has gained increasing attention to realize battery-less and maintenance-free IoT devices [1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18]. To realize such devices, highly efficient power management systems are strongly required because the output voltages of the small harvesters are basically weak and are easily lost depending on their power generation environment. When the energy from the harvester is cut off during the charging phase, the charged and stored energy on the energy buffer is dissipated as a reverse current.

An ADIO can prevent the reverse current problem. However, the conventional ADIO consisting of a MOS switch and common-gate (CG) comparator suffers from ripple and noise voltages. The hysteresis comparator can cope with the ripple and noise voltages [19]. There are several hysteresis comparators that are based on the differential pair circuit. However, there are few reports on the CG comparator with hysteresis.

In light of the background, we propose an ultra-low power

hysteresis CG comparator and develop an ADIO using the hysteresis CG comparator. In our proposed power management system, the hysteresis CG comparator monitors the output voltage of the energy harvester and stored voltage of the energy buffer and prevents the reverse current when the energy from the harvester is lost. This paper is organized as follows: Section II briefly summarizes our proposed power management system. Section III explains our proposed hysteresis CG comparator. Section IV discusses the simulation results. Section V concludes the paper.

## 2. Proposed power management system

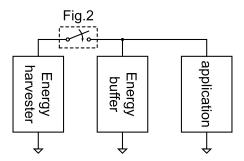

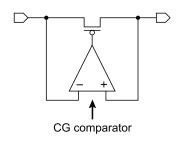

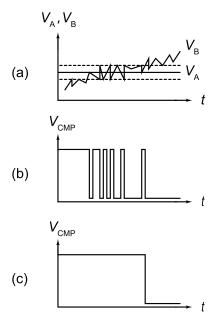

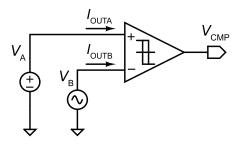

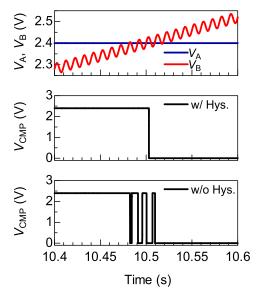

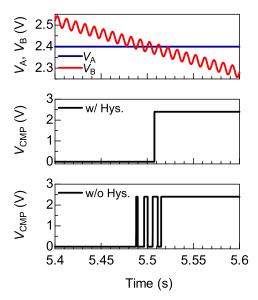

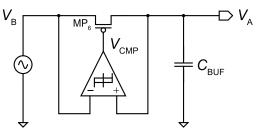

Figure 1 shows a power management system. The system employs an ADIO as a switch between the harvester and energy buffer. Figure 2 shows the ADIO. The ADIO consists of a CG comparator and pMOS transistor. The ADIO transfers the charge to the energy buffer with a quite low voltage difference [20, 21, 22, 23, 24]. When the output voltage of the energy harvester is lost, the ADIO will detect the input voltage reduction and cut off the current path to prevent the reverse current. Figure 3 shows waveforms of input and output voltages with and without hysteresis. The ripple and noise voltages will oscillate the comparator's output when we use a comparator without hysteresis (Fig. 3(b)). To

Fig. 1 Proposed power management system.

Fig. 2 ADIO using CG comparator.

1

DOI: 10.1587/elex.17.20200103 Received March 17, 2020 Accepted March 31, 2020 Publicized April 10, 2020 Copyedited June 10, 2020

Dept. of Electrical and Electronic Engineering, Kobe University, 1–1 Rokkodai, Nada, Kobe 657–8501, Japan

Dept. of Electrical and Electronic Engineering, Osaka University, 2–1 Yamadaoka, Suita, Osaka 565–0871, Japan

a) matsumoto@eedept.kobe-u.ac.jp

b) hirose@eei.eng.osaka-u.ac.jp

Fig. 3 Waveforms of (a) input voltages, (b) output voltage of the comparator without hysteresis, and (c) output voltage of the comparator with hysteresis.

eliminate the oscillation (Fig. 3(c)), we use hysteresis comparators. There are several hysteresis comparators that are based on the differential pair circuit. However, there are few reports on the CG comparator with hysteresis. Therefore, we develop a hysteresis CG comparator for the ADIO.

## 3. Hysteresis CG comparator

#### 3.1 Conventional CG comparator

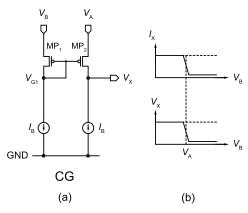

Figure 4(a) shows a simplified core circuit of the conventional CG comparator. The circuit consists of two current sources and two pMOS transistors. Input voltages  $V_A$  and  $V_B$  are connected to the source terminals of the pMOS transistors. Figure 4(b) illustrates waveforms of the output current  $I_X$  and output voltage  $V_X$  when  $V_A$  is set to a certain voltage and  $V_B$  is changed from Low to High. When  $V_B$  is lower than  $V_A$ ,  $V_X$  is high because current flowing in MP<sub>2</sub> is larger than  $I_B$ . On the other hand, when  $V_B$  is higher than  $V_A$ ,  $V_X$  is low because current flowing in MP<sub>2</sub> is lower than  $I_B$ . Therefore, current flowing in MP<sub>2</sub> will determine the voltage of  $V_X$ . This can be analyzed as follows.

When the source-drain voltage  $V_{\rm SD}$  of a PMOS transistor is 0.1 V or more, the subthreshold drain current I can be expressed as

$$I = KI_0 \exp\left(\frac{V_{\text{SG}} - |V_{\text{THP}}|}{\eta V_{\text{T}}}\right),\tag{1}$$

where K(=W/L) is the aspect ratio of the transistor,  $I_0(=\mu C_{\rm ox}V_{\rm T}^2(\eta-1))$  is the process dependent parameter,  $\mu$  is the carrier mobility,  $C_{\rm ox}$  is the gate-oxide capacitance,  $V_{\rm T}(=k_{\rm B}T/q)$  is the thermal voltage,  $k_{\rm B}$  is the Boltzmann constant, T is the absolute temperature, q is the elementary charge,  $\eta$  is the subthreshold slope factor,  $V_{\rm SG}$  is the source-source voltage, and  $|V_{\rm TH}|$  is the threshold voltage of a pMOS transistor. From Eq. (1), the source-gate voltage  $V_{\rm SG1}$  of

**Fig. 4** (a) Schematic of the simplified CG comparator and (b) illustrations of the output current and voltage  $(I_X \text{ and } V_X)$ .

Fig. 5 Simplified schematic of our hysteresis CG comparator.

MP1 is expressed as

$$V_{\text{SG1}} = |V_{\text{THP}}| + \eta V_{\text{T}} \ln \left( \frac{I_{\text{B}}}{K_1 I_0} \right), \tag{2}$$

where  $I_{\rm B}$  is the bias current and  $K_1$  is the aspect ratio of MP1. From Eq. (2),  $V_{\rm G1}$  can be expressed as

$$V_{G1} = V_{B} - V_{SG1}$$

$$= V_{B} - |V_{THP}| - \eta V_{T} \ln \left( \frac{I_{B}}{K_{1}I_{0}} \right).$$

(3)

The source-gate voltage  $V_{SG2}$  of MP2 can be expressed as

$$V_{SG2} = V_{A} - V_{G1}. (4)$$

Therefore, from Eqs. (1) and (3), the current  $I_2$  can be expressed as

$$I_2 = \frac{K_2}{K_1} I_{\rm B} \exp\left(\frac{V_{\rm A} - V_{\rm B}}{\eta V_{\rm T}}\right),\tag{5}$$

where  $K_2$  is the aspect ratio of M2. When  $K_1 = K_2$ , Eq. (5) can be expressed as

$$I_2 = I_{\rm B} \exp\left(\frac{V_{\rm A} - V_{\rm B}}{\eta V_{\rm T}}\right). \tag{6}$$

Therefore, the current  $I_X$  flowing into  $V_X$  can be expressed as

$$I_{\rm X} = I_2 - I_{\rm B}$$

$$= I_{\rm B} \left\{ \exp\left(\frac{V_{\rm A} - V_{\rm B}}{\eta V_{\rm T}}\right) - 1 \right\}. \tag{7}$$

From Eq. (7), when  $V_{\rm B} < V_{\rm A}$ ,  $I_{\rm X}$  becomes positive and  $V_{\rm X}$  increases. On the other hand, when  $V_{\rm B} > V_{\rm A}$ ,  $I_{\rm X}$  becomes negative and  $V_{\rm X}$  decreases. Figure 4(b) illustrates  $I_{\rm X}$  and  $V_{\rm X}$  as a function of  $V_{\rm B}$ . When  $V_{\rm B} = V_{\rm A}$ , the output voltage  $V_{\rm X}$  changes from High to Low.

## 3.2 Proposed hysteresis CG comparator

As discussed in the previous section, we can control the switching voltage of the CG comparator by changing the bias current  $I_B$  connected to  $V_X$ . Figure 5 shows a simplified schematic of our proposed hysteresis CG comparator. A switch (SW) is used to control the bias current.

When SW is OFF,  $I_3$  in Fig. 5 becomes  $I_B/2$ . From Eq. (7),  $I_X$  can be expressed as

$$I_{\rm X} = I_2 - I_3 = I_2 - \frac{1}{2}I_{\rm B}$$

=  $I_{\rm B} \left\{ \exp\left(\frac{V_{\rm A} - V_{\rm B}}{\eta V_{\rm T}}\right) - \frac{1}{2} \right\}$ . (8)

Therefore, from Eq. (8),  $I_X$  becomes positive, when

$$V_{\rm B} > V_{\rm A} + \eta V_{\rm T} \ln 2. \tag{9}$$

The switching voltage becomes higher than  $V_A$  by  $\eta V_T \ln 2$ . It is 27 mV, when we set  $\eta$  and  $V_T$  at room temperature to 1.5 and 26 mV, respectively.

On the other hand, when SW is ON, current  $I_3$  in Fig. 5 becomes  $2I_B$ . Therefore, from Eq. (7),  $I_X$  can be expressed as

$$I_{\rm X} = I_2 - I_3 = I_2 - 2I_{\rm B}$$

=  $I_{\rm B} \left\{ \exp\left(\frac{V_{\rm A} - V_{\rm B}}{\eta V_{\rm T}}\right) - 2 \right\}$ . (10)

Therefore, from Eq. (10),  $I_X$  becomes positive, when

$$V_{\rm B} < V_{\rm A} - \eta V_{\rm T} \ln 2. \tag{11}$$

The switching voltage becomes lower than  $V_A$  by  $\eta V_T \ln 2$ . It is -27 mV, when we set  $\eta$  and  $V_T$  at room temperature to 1.5 and 26 mV, respectively.

Therefore, when the input voltage  $V_{\rm B}$  changes from Low to High, a positive hysteresis voltage can be obtained by turning SW OFF. On the other hand, when the input voltage  $V_{\rm B}$  changes from High to Low, a negative hysteresis voltage can be obtained by turning SW ON. Figure 6 shows a complete schematic of our proposed hysteresis CG comparator.

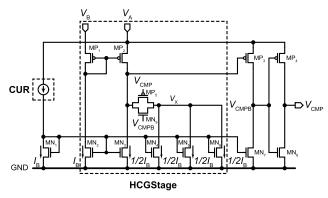

Fig. 6 Schematic of our proposed hysteresis CG comparator.

A common source amplifier (MN<sub>7</sub>-MP<sub>3</sub>) and inverter (MN<sub>8</sub>-MP<sub>4</sub>) are added to enhance the total voltage gain. A nano-ampere current source is used to achieve ultra-low power dissipation [25, 26, 27, 28, 29, 30]. The transistor sizes of MN<sub>1</sub>:MN<sub>2</sub>:MN<sub>3-6</sub> are set to 4:2:1. A transmission gate (MP<sub>5</sub> and MN<sub>9</sub>) is used as the switch to control the bias current. The outputs of the comparator  $V_{\rm CMP}$  and common source amplifier  $V_{\rm CMPB}$  are used to control the transmission gate.

#### 4. Results

#### 4.1 Simulation results

We evaluated the performance of our hysteresis CG comparator using SPICE with a set of 65-nm standard CMOS process parameters. Table I lists the transistor sizes  $(M \times (W/L), M$ : multiplier, W: channel width, and L: channel length) of the comparator. Figure 7 shows the simulated hysteresis CG comparator circuit.

Figures 8 and 9 show the simulated transient waveforms of the comparator. The  $V_A$  and  $I_B$  were set to 2.4 V and 2 nA, respectively. The  $V_B$  increased from 2.3 to 2.5 V (Fig. 8), and then decreased from 2.5 to 2.3 V (Fig. 9), with a ripple voltage. The frequency and amplitude of the ripple voltage were set to 100 Hz and 50 mV, respectively. The output voltage of the comparator without hysteresis oscillated as shown on the bottom in Figs. 8 and 9. We confirmed that our proposed comparator operated correctly.

## 4.2 Experimental results

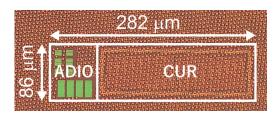

A prototype chip was fabricated with a 65-nm, CMOS process with deep n-well option. The circuit was designed with the same parameters as those in the simulation. Figure 10 shows a chip micrograph of our comparator. The area occupied  $0.024~\rm{mm}^2$ .

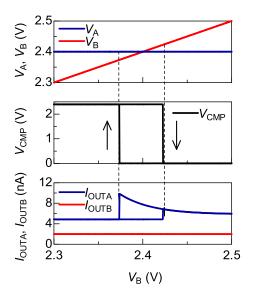

Figure 11 shows the measurement  $V_A$ ,  $V_B$ ,  $V_{CMP}$ ,  $I_{OUTA}$ ,

Table I Transistor sizes Transistor  $MP_1, MP_2$  $4\times(4 \mu \text{m}/10 \mu \text{m})$  $\overline{MP}_3$  $4\times(2 \mu \text{m}/10 \mu \text{m})$  $\overline{\text{MP}_4}$  $5\times(1 \ \mu\text{m/5} \ \mu\text{m})$ MP<sub>5</sub>  $5\times(1 \mu m/1 \mu m)$  $40 \times (1 \ \mu \text{m}/1 \ \mu \text{m})$  $MP_6$  $\overline{MN_1}$  $8\times(2 \mu \text{m}/10 \mu \text{m})$  $\overline{MN_2, MN_7}$  $4\times(2 \mu \text{m}/10 \mu \text{m})$  $MN_3$ ,  $MN_4$ ,  $MN_5$ ,  $MN_6$  $2\times(2 \mu \text{m}/10 \mu \text{m})$  $1\times(1 \mu \text{m}/25 \mu \text{m})$  $MN_8$ MN<sub>9</sub>  $5\times(1 \mu m/1 \mu m)$

Fig. 7 Block diagram of hysteresis CG comparator.

Fig. 8 Simulated transient waveforms.

Fig. 9 Simulated transient waveforms.

Fig. 10 Chip micrograph.

and  $I_{\rm OUTB}$ , as a function of  $V_{\rm B}$ . As shown in Fig. 11, we confirmed that  $V_{\rm CMP}$  changed with hysteresis voltages. The positive and negative hysteresis voltages were 25 and -26 mV, respectively, which were almost the same as the calculated results. The maximum current consumption  $I_{\rm OUTA}$ , and  $I_{\rm OUTB}$  were 9.82 and 1.97 nA, respectively.

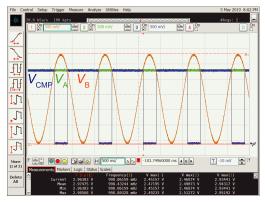

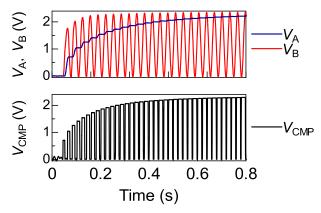

Figure 12 shows the measured transient waveforms  $V_{\rm A}$ ,  $V_{\rm B}$  and  $V_{\rm CMP}$ . The  $V_{\rm A}$  and  $I_{\rm B}$  were set to 2.4 V and 2 nA, respectively. The frequency and peak-to-peak voltage of  $V_{\rm B}$  were set to 1 Hz and 3 V, respectively. The  $V_{\rm CMP}$  was high

Fig. 11 Measured transfer function.

Fig. 12 Measured transient waveforms.

Fig. 13 Block diagram of ADIO.

when  $V_{\rm B}$  was lower than  $V_{\rm A}$ , while the  $V_{\rm CMP}$  was low when  $V_{\rm B}$  was higher than  $V_{\rm A}$ . We confirmed that our proposed comparator operated correctly.

Figure 13 shows a test bench circuit of our proposed ADIO using our proposed hysteresis CG comparator. The  $C_{\rm BUF}$  and  $I_{\rm B}$  were set to 100 uF and 2 nA, respectively. The frequency and peak-to-peak voltage of  $V_{\rm B}$  were set to 50 Hz and 2.4 V, respectively. Figure 14 shows the measured waveforms of the ADIO. The output voltage of the CG comparator  $V_{\rm CMP}$  changed correctly according to the voltage difference between  $V_{\rm A}$  and  $V_{\rm B}$ . The measured  $V_{\rm A}$  increased gradually as expected because the ADIO cut off the reverse current successfully.

Fig. 14 Measured transient waveforms with ADIO.

### 5. Conclusion

This paper presented a hysteresis CG comparator and active diode (ADIO) using the CG comparator for low-voltage and low-power energy harvesting systems. The proposed ADIO consists of a MOS switch and CG comparator, which eliminates unwanted ripple and noise voltages. The hysteresis CG comparator controls the MOS switch to turn ON or OFF, depending on the input and output voltages. The hysteresis voltage of the comparator can be controlled by the current flowing in the CG comparator. The measurement results demonstrated that the hysteresis CG comparator had -26 and 25 mV hysteresis voltages and the active diode using the hysteresis CG comparator eliminated unwanted ripple voltage. The maximum current consumption of our ADIO was 11.8 nA.

# Acknowledgments

This work was based on results obtained from a project commissioned by the New Energy and Industrial Technology Development Organization (NEDO) of Japan, and was conducted through a dedicated licensing program provided by the VLSI Design and Education Center (VDEC) at the University of Tokyo with the cooperation of Cadence Design Systems, Inc. and Mentor, a Siemens business.

This work was also partially supported by JSPS KAKENHI Grant Number JP19K11875 and Canon Foundation.

#### References

- [1] L.D. Xu, et al.: "Internet of things in industries: a survey," IEEE Trans. Ind. Inform. 10 (2014) 2233. (DOI: 10.1109/tii.2014.2300753)

- [2] D. Blaauw, et al.: "IoT design space challenges: circuits and systems," Symp. VLSI Technol. Dig. Tech. Papers (2014) 1. (DOI: 10.1109/ vlsit.2014.6894411)

- [3] S. Chen, et al.: "A vision of IoT: applications, challenges, and opportunities with china perspective," IEEE Internet Things J. 1 (2014). (DOI: 10.1109/jiot.2014.2337336)

- [4] R.J.M. Vullers, et al.: "Energy harvesting for autonomous wireless sensor networks," IEEE Solid-State Circuits Mag. 2 (2010) 29. (DOI: 10.1109/mssc.2010.936667)

- [5] V. Raghunathan and P.H. Chou: "Design and power management of energy harvesting embedded systems," Proc. Int. Symp. Low Power Electron. Design (ISLPED) (2006) 369. (DOI:

#### 10.1145/1165573.1165663)

- [6] A.P. Chandrakasan, et al.: "Next generation micro-power systems," IEEE Symp. VLSI Circuits (2008) 2. (DOI: 10.1109/vlsic.2008. 4585930)

- [7] T. Hirose, et al.: "Watch-dog circuit for quality guarantee with subthreshold MOSFET current," IEICE Trans. Electron. E87-C (2004) 1910.

- [8] K. Ueno, et al.: "CMOS smart sensor for monitoring the quality of perishables," IEEE J. Solid-State Circuits 42 (2007) 798. (DOI: 10.1109/jssc.2007.891676)

- [9] H. Asano, et al.: "A 1.66-nW/kHz, 32.7-kHz, 99.5ppm/°C, fully integrated current-mode RC oscillator for real-time clock applications with PVT stability," Proc. Eur. Solid-State Circuits Conf. (ESSCIRC) (2016) 149. (DOI: 10.1109/esscirc.2016.7598264)

- [10] T. Ozaki, et al.: "Fully-integrated high-conversion-ratio dual-output voltage boost converter with MPPT for low-voltage energy harvesting," IEEE J. Solid-State Circuits 51 (2016) 2398. (DOI: 10.1109/JSSC.2016.2582857)

- [11] T. Ozaki, et al.: "A highly efficient switched-capacitor voltage boost converter with nano-watt MPPT controller for low-voltage energy harvesting," IEICE Trans. Fundam. Electron. Commun. Comput. Sci. E99-A (2016) 2491. (DOI: 10.1587/transfun.e99.a.2491)

- [12] Y. Tsuji, et al.: "A 0.1–0.6 V input range voltage boost converter with low-leakage driver for low-voltage energy harvesting," Proc. Int. Conf. Electron. Circuits Syst. (ICECS) (2017) 502. (DOI: 10.1109/icecs.2017.8292004)

- [13] R. Matsuzuka, et al.: "A 42-mV startup ring oscillator using gainenhanced self-bias inverters for extremely low voltage energy harvesting," Jpn. J. Appl. Phys. 59 (2020) SGGL01. (DOI: 10.7567/1347-4065/ab65d4)

- [14] H. Asano, et al.: "A fully integrated, wide load range, high power conversion efficiency switched capacitor DC-DC converter with adaptive bias comparator for ultra-low-power power management integrated circuit," Jpn. J. Appl. Phys. 57 (2018) 04FF03. (DOI: 10.7567/jjap.57.04ff03)

- [15] Y. Kojima, et al.: "A fully on-chip 3-terminal switched capacitor DC-DC converter for low-voltage CMOS LSIs," Jpn. J. Appl. Phys. 55 (2016) 04EF09. (DOI: 10.7567/jjap.55.04ef09)

- [16] M. Nishi, et al.: "Sub-0.1V input, low-voltage CMOS driver circuit for multi-stage switched capacitor voltage boost converter," Proc. Int. Conf. Electron. Circuits Syst. (ICECS) (2019) 530. (DOI: 10.1109/icecs46596.2019.8964719)

- [17] T. Ozaki, et al.: "Ultra-low quiescent current and wide load range low-dropout linear regulator with self-biasing technique for micropower battery management," Jpn. J. Appl. Phys. 56 (2017) 04CF11. (DOI: 10.7567/jjap.56.04cf11)

- [18] Y. Nakazawa, et al.: "Analytical study of multi-stage switched-capacitor voltage boost converter for ultra-low voltage energy harvesting," Proc. Int. Symp. Circuits Syst. (ISCAS) (2018) 1. (DOI: 10.1109/iscas.2018.8351466)

- [19] K. Matsumoto, et al.: "An ultra-low power active diode using a hysteresis common gate comparator for low-voltage and low-power energy harvesting systems," Proc. IFIP/IEEE Int. Conf. Very Large Scale Integration (2018) 196. (DOI: 10.1109/vlsi-soc.2018.8644968)

- [20] Y. Rao, et al.: "An input-powered vibrational energy harvesting interface circuit with zero standby power," IEEE Trans. Power Electron. 26 (2011) 3524. (DOI: 10.1109/tpel.2011.2162530)

- [21] P.F. Becker, et al.: "Efficient energy harvesting with electromagnetic energy transducers using active low-voltage rectification and maximum power point tracking," IEEE J. Solid-State Circuits 47 (2012) 1369. (DOI: 10.1109/jssc.2012.2188562)

- [22] Q. Li, et al.: "A wide input amplitude range, highly efficient rectifier for low power energy harvesting systems," NOLTA 5 (2014) 499. (DOI: 10.1587/nolta.5.499)

- [23] E.E. Aktakka, et al.: "A micro inertial energy harvesting platform with self-supplied power management circuit for autonomous wireless sensor nodes," IEEE J. Solid-State Circuits 49 (2014) 2017. (DOI: 10.1109/jssc.2014.2331953)

- [24] D.A. Sanchez, et al.: "A parallel-SSHI rectifier for piezoelectric energy harvesting of periodic and shock excitations," IEEE J. Solid-State Circuits 51 (2016) 2867. (DOI: 10.1109/jssc.2016.2615008)

- [25] T. Hirose, et al.: "Ultralow-power current reference circuit with low temperature dependence," IEICE Trans. Electron. E88-C (2005) 1142. (DOI: 10.1093/ietele/e88-c.6.1142)

- [26] T. Hirose, et al.: "Temperature-compensated CMOS current reference circuit for ultralow-power subthreshold LSIs," IEICE Electron. Express 5 (2008) 204. (DOI: 10.1587/elex.5.204)

- [27] K. Ueno, et al.: "A 1-uW, 600-ppm/°C current reference circuit consisting of sub-threshold CMOS circuits," IEEE Trans. Circuits Syst. II, Exp. Briefs 57 (2010) 681. (DOI: 10.1109/tcsii.2010.2056051)

- [28] T. Hirose, et al.: "A nano-ampere current reference circuit and its temperature dependence control by using temperature characteristics of carrier mobilities," Proc. Eur. Solid-State Circuits Conf. (ESSCIRC) (2010) 114. (DOI: 10.1109/esscirc.2010.5619819)

- [29] Y. Osaki, et al.: "Temperature-compensated nano-ampere current reference circuit with subthreshold metal-oxide-semiconductor field effect transistor resistor ladder," Jpn. J. Appl. Phys. 50 (2011) 04DE08. (DOI: 10.7567/jjap.50.04de08)

- [30] I. Homjakovs, et al.: "A 0.8-V 110-nA CMOS current reference circuit using subthreshold operation," IEICE Electron. Express 10 (2013) 20130022. (DOI: 10.1587/elex.10.20130022)