PDF issue: 2025-12-05

# Evaluation of organic metal-oxide-semiconductor capacitors based on a distributed constant circuit

Kimura, Yoshinari Hattori, Yoshiaki Kitamura, Masatoshi

#### (Citation)

Japanese Journal of Applied Physics, 59(3):036503-036503

(Issue Date) 2020-03-01

(Resource Type) journal article

(Version)

Accepted Manuscript

#### (Rights)

© 2020 The Japan Society of Applied Physics. This is the Accepted Manuscript version of an article accepted for publication in Japanese Journal of Applied Physics. IOP Publishing Ltd is not responsible for any errors or omissions in this version of the manuscript or any version derived from it. The Version of Record is available online...

(URL)

https://hdl.handle.net/20.500.14094/90007352

Evaluation of organic metal-oxide-semiconductor capacitors based on a distributed constant circuit

Yoshinari Kimura\*, Yoshiaki Hattori, and Masatoshi Kitamura\*\*

Department of Electrical and Electronic Engineering, Graduate School of Engineering, Kobe University, Kobe 657-8501, Japan

\*E-mail address: kimura@eedept.kobe-u.ac.jp

\*\*E-mail address: kitamura@eedept.kobe-u.ac.jp

The capacitance characteristics of pentacene metal-oxide-semiconductor (MOS) capacitors with a large uncovered pentacene area have been investigated. The capacitance measured was examined by assuming that the uncovered area is represented by a distributed constant circuit. The frequency dependence of the capacitance was reproduced by an equation derived based on the assumption. The sheet resistance for the uncovered area of a MOS capacitor was calculated as a function of the gate voltage from the capacitance measured. The mobility of a MOS capacitor with an uncovered area was estimated by fitting a curve to the gate-voltage dependence of the sheet resistance, and was in the range of 0.48 to 0.64 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. In addition, the mobilities were compared with those calculated from the current-voltage characteristics of pentacene transistors fabricated on the same substrate.

#### 1. Introduction

Organic semiconductor devices, including thin film transistors (TFTs),<sup>1,2)</sup> light-emitting diodes,<sup>3,4)</sup> photovoltaics,<sup>5,6)</sup> and chemical sensors,<sup>7,8)</sup> have attracted attention because of their potential application to flexible, large-area, light-weight, and low-cost electronic devices. In addition to these features, the field-effect mobilities in organic TFTs significantly improving with finding of novel materials <sup>9)</sup> have reached over 10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.<sup>10)</sup> With the improvement of organic device performance, the carrier transport in organic devices is required to be investigated in more detail.<sup>11,12)</sup>

For organic TFTs, the field-effect mobility and threshold voltage calculated from the current-voltage characteristics are used as standard evaluation for them.<sup>13)</sup> The contact resistance between the contact electrode and the organic semiconductor in organic TFTs is often calculated based on a transfer line method.<sup>14-16)</sup> In this method, the contact resistance is also calculated from the current-voltage characteristics obtained by DC measurement. On the other hand, impedance spectroscopy based on AC measurement is an evaluation methods for organic TFTs when focusing on the metal-oxide-semiconductor (MOS) or metal-insulator-semiconductor (MIS) structure.<sup>17,18)</sup> Actually, the capacitance-voltage characteristics measured at a certain frequency have been used for investigation of the interface states,<sup>19,20)</sup> the flat-band voltage,<sup>21-23)</sup> the injection barrier,<sup>24)</sup> and the stability.<sup>25)</sup> The investigation is based on theory for Si-based MOS capacitors.<sup>26)</sup> However, an organic MOS capacitor often has an area uncovered with the contact electrode to the organic semiconductor. In order to eliminate the influence, it is necessary to remove the organic layer uncovered with the contact electrode.<sup>18)</sup>

Some groups have examined organic TFTs<sup>27,28)</sup> and organic MOS capacitors<sup>29-33)</sup> considering organic semiconductor areas uncovered with the contact electrode. Hamadani *et al.* and Girolamo *et al.* investigated the characteristics of organic TFTs using equivalent circuits consisting of distributed elements for the uncovered area.<sup>27,28)</sup> On the other hand, Jung *et al.* and Hayashi *et al.* reproduced the characteristics of organic MOS capacitors with uncovered organic areas using a distributed constant circuit<sup>29</sup> and a diffusion equation,<sup>30</sup> respectively. In order to reproduce the measured results, it is necessary to consider both the effect of the uncovered area and that of the MOS capacitors covered by the electrode. The lengths of the uncovered areas were up to about 95 µm for Ref. 29) and 235 µm for Ref. 30).

On the other hand, Ucurum and Goebel investigated the capacitance-voltage characteristics of pentacene MOS capacitors having uncovered areas up to 4 mm in length.<sup>31)</sup> They analyzed the characteristics separating into three components for metal/insulator/metal, covered MIS, and uncovered MIS structures. Although the method of the analysis is effective, it is seems that the hysteresis in the capacitance-voltage characteristics caused difficulty in quantitative analysis. If a MOS capacitor having an uncovered area sufficiently larger than a covered area is examined, it is possible to eliminate the influence of the covered MOS area and intensively analyze the carrier transport in organic layers uncovered with an electrode. Actually, we have reported the voltage and frequency dependence of capacitance in pentacene MOS capacitors with a large uncovered area without detail analysis.<sup>34)</sup>

In this paper, we report the capacitance characteristics of pentacene MOS capacitors with a large uncovered area in detail. The measured capacitance is systematically examined by assuming that the uncovered area is represented by a distributed constant circuit. The sheet resistance derived from the measured capacitance is used for calculation of the carrier mobility in the pentacene layer. The carrier mobilities are compared with those calculated from the current-voltage characteristics of pentacene TFTs fabricated on the same substrates.

# 2. Analytical method

#### 2.1 Characteristics of MOS capacitors

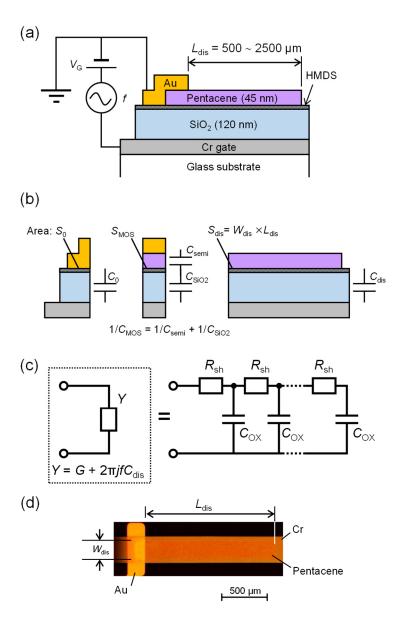

Figure 1(a) shows illustration of a pentacene MOS capacitor examined in this study. The pentacene layer has an area uncovered with the top Au electrode. For measurement of the capacitance, an AC voltage of frequency f superimposed on a gate voltage  $V_G$  was applied to the Cr gate electrode as seen in Fig. 1(a). The length and the width of the uncovered area are denoted by  $L_{\rm dis}$  and  $W_{\rm dis}$ , respectively. The total capacitance of the MOS capacitor C can be represented as

$$C = C_0 + C_{\text{MOS}} + C_{\text{dis}},\tag{1}$$

where  $C_0$ ,  $C_{MOS}$ , and  $C_{dis}$  are the capacitances of Au/SiO<sub>2</sub>/Cr, Au/pentacene/SiO<sub>2</sub>/Cr, and pentacene/SiO<sub>2</sub>/Cr structures shown in Fig. 1(b), respectively. When the capacitance per unit area of SiO<sub>2</sub> is denoted as  $C_{OX}$ ,  $C_0 = C_{OX}$   $S_0$  where  $S_0$  is the area of the Au/SiO<sub>2</sub>/Cr structure. The capacitance of the Au/pentacene/SiO<sub>2</sub>/Cr structure  $C_{MOS}$  is given by

$$C_{\text{MOS}} = \begin{cases} C_{\text{SiO2}} & \text{when carriers are accumulated in the pentacene} \\ 1/(1/C_{\text{SiO2}} + 1/C_{\text{semi}}) & \text{when no carrier presents in the pentacene} \end{cases}, (2)$$

where  $C_{SiO2} = C_{OX} S_{MOS}$ ,  $C_{semi} = \varepsilon_{pen} S_{MOS}/d_{pen}$ ,  $S_{MOS}$  is the area of the Au/pentacene/SiO<sub>2</sub>/Cr structure,  $\varepsilon_{pen}$  is the dielectric constant, and  $d_{pen}$  is the thickness of the pentacene. Assuming that the pentacene/SiO<sub>2</sub>/Cr structure is represented by a distributed constant circuit, the capacitance component  $C_{dis}$  in the admittance Y ( $Y = G + jB = G + j2\pi fC_{dis}$ ), which is composed of conductance G and susceptance B, is given by

$$C_{\text{dis}} = C_{\text{OX}} W_{\text{dis}} L_{\text{dis}} \frac{1}{\alpha} \frac{\sinh \alpha + \sin \alpha}{\cosh \alpha + \cos \alpha},$$

(3)

where

$$\alpha = \sqrt{4\pi f C_{\text{OX}} R_{\text{sh}} L_{\text{dis}}^2} \tag{4}$$

is a dimensionless quantity,  $R_{\rm sh}$  is the sheet resistance in the pentacene layer, and f is the frequency for capacitance measurement.<sup>32,33)</sup> Equation (3) can be derived by assuming that the line inductance and parallel resistance in a distributed constant circuit with open termination are equal to zero. When a function  $g(\alpha)$  is defined as

$$g(\alpha) = \frac{1}{\alpha} \frac{\sinh \alpha + \sin \alpha}{\cosh \alpha + \cos \alpha},\tag{5}$$

the function has the following properties:

$$\lim_{\alpha \to +0} g(\alpha) = 1, \tag{6a}$$

$$\lim_{\alpha \to +\infty} g(\alpha) = 0. \tag{6b}$$

Therefore, the dependence of  $C_{dis}$  on  $R_{sh}$  exhibits that

$$C_{\rm dis} \approx C_{\rm OX} W_{\rm dis} L_{\rm dis}$$

for  $R_{\rm sh} \ll (1/f C_{\rm OX} L_{\rm dis}^2)$ , (7a)

$$C_{\text{dis}} \approx 0$$

for  $R_{\text{sh}} \gg (1/fC_{\text{OX}}L_{\text{dis}}^2)$ . (7b)

Since pentacene is a *p*-channel material, the decreases in  $V_G$  leads to the accumulation of holes in a pentacene layer, the decrease in  $R_{\rm sh}$ , and the asymptotic to  $(C_0 + C_{\rm SiO2} + C_{\rm OX} W_{\rm dis} L_{\rm dis})$  of C. On the other hand, the increase in  $V_G$  leads to the depletion of holes, the increase in  $R_{\rm sh}$ , and the asymptotic to  $\{C_0 + 1/(1/C_{\rm SiO2} + 1/C_{\rm semi})\}$  of C. Since  $R_{\rm sh}$  is only an unknown

value in the equation for C, a value of  $R_{\rm sh}$  can be estimated from an experimental C value.

For the Au/pentacene/SiO<sub>2</sub>/Cr structure in Fig. 1(b), the bulk resistance for the pentacene and the contact resistance at the interface of Au and pentacene are not considered in this study. This is because we focus on the characteristics of  $C_{\rm dis}$  for the pentacene/SiO<sub>2</sub>/Cr structure. Although C defined in Eq. (1) does not contain effect of the resistances mentioned above, capacitances measured in this study are actually reproduced by the C defined in Eq. (1) as seen in Sect. 4.

#### 2.2 Mobility and threshold voltage in uncovered pentacene layers

When  $V_G$  is applied to the Cr gate electrode, the sheet resistance  $R_{sh}$  induced by hole carriers accumulated in the pentacene layer can be expressed as

$$R_{\rm sh} = \frac{1}{\mu C_{\rm ox} |V_{\rm G} - V_{\rm 0}|} \tag{8}$$

on the basis of the assumption that

$$R_{\rm sh} = \frac{1}{\sigma \delta},\tag{9a}$$

$$\sigma = en\mu = e\frac{n_{\rm S}}{\delta}\mu = \frac{Q_{\rm S}}{\delta}\mu, \tag{9b}$$

$$Q_{\rm S} = C_{\rm OX} |V_{\rm G} - V_0| \,. \tag{9c}$$

Here,  $\mu$  is the carrier mobility for the hole,  $\sigma$  is the conductivity, n is the density of the hole,  $\delta$  is the thickness of the accumulation layer,  $n_S$  is the area density of the charge,  $Q_S$  is the surface charge density, and  $V_0$  is the maximum value in voltages at which holes accumulate.  $V_0$  corresponds to threshold voltage of the MOS transistor. The notation for the voltage  $V_0$  is used to distinguish it from the threshold voltage estimated from experimental results of transistors. The  $R_{\rm sh}$  value estimated from an experimental C depends on  $V_{\rm G}$ . The  $\mu$  and  $V_0$  values can be calculated by fitting a curve to the relation between  $R_{\rm sh}$  and  $V_{\rm G}$ .

#### 2.3 Characteristics of TFTs

In the gradual channel approximation, the drain current  $I_D$  flowing from the drain to the source for p-channel organic TFT is given by

$$I_{\rm D} = -\frac{1}{2} \mu_{\rm FE} C_{\rm OX} \frac{W}{L} (V_{\rm G} - V_{\rm TH})^2, \quad \text{for } |V_{\rm D}| \ge |V_{\rm G} - V_{\rm TH}|,$$

(10a)

$$I_{\rm D} = -\mu_{\rm FE} C_{\rm OX} \frac{W}{L} \left[ (V_{\rm G} - V_{\rm TH}) V_{\rm D} - \frac{1}{2} V_{\rm D}^{2} \right], \qquad \text{for } |V_{\rm D}| \le |V_{\rm G} - V_{\rm TH}|$$

(10b)

where  $\mu_{\rm FE}$  is the field-effect mobility, W and L are the channel width and length,  $V_{\rm TH}$  is the threshold voltage,  $V_{\rm G}$  and  $V_{\rm D}$  are the source-gate and the source-drain voltages. In this study, the field-effect mobility ( $\mu_{\rm sat}$ ) and  $V_{\rm TH}$  values experimentally estimated in the saturation regime were calculated by fitting a line to a measured  $|I_{\rm D}|^{1/2}$ - $V_{\rm G}$  curve with Eq. (10a). The experimental field-effect mobility ( $\mu_{\rm lin}$ ) in the linear regime was calculated from a measured  $|I_{\rm D}|$ - $V_{\rm G}$  curve using Eq. (10b).

When  $|V_{\rm D}| \ll |V_{\rm G} - V_{\rm TH}|$ , the drain current is approximated as

$$I_{\rm D} \cong -\mu_{\rm FE} C_{\rm OX} \frac{W}{L} (V_{\rm G} - V_{\rm TH}) V_{\rm D}. \tag{11}$$

Equation (11) relates to Eq. (8). Actually, Eq. (8) is derived from Eq. (11) by dividing  $V_D$  by  $I_D$ . Since the structure in Fig. 1(a) corresponds to a transistor having no drain electrode, the measurement for the structure satisfies the condition that  $|V_D|$  is small.

#### 2.4 Contact resistance and sheet resistance for TFTs

The on-resistance  $R_{\rm on}$ , the channel resistance  $R_{\rm ch}$ , and the contact resistance  $R_{\rm C}$  for a TFT were calculated to compare  $R_{\rm sh}$  estimated from C with the sheet resistance  $R_{\rm TFT}$  calculated from the characteristics for the TFT. In the transfer line method, <sup>15,16)</sup> the on-resistance, which is defined as  $\left|\partial V_{\rm D}/\partial I_{\rm D}\right|$ , is assumed to be

$$R_{\rm on} = R_{\rm ch} + R_{\rm C} = \frac{L}{\mu_{\rm I} W C_{\rm OX} |V_{\rm G} - V_{\rm TH}|} + R_{\rm C}$$

(12)

where  $\mu_{\rm I}$  is the mobility in the intrinsic transistor without contact resistance.  $R_{\rm TFT}$  is given by

$$R_{\rm TFT} = R_{\rm ch} \frac{W}{L} = \frac{1}{\mu_{\rm l} C_{\rm OX} |V_{\rm G} - V_{\rm TH}|}.$$

(13)

As a result, Eq. (13) has the same form as Eq. (8).

## 3. Experimental method

Pentacene MOS capacitors and pentacene TFTs were fabricated on glass substrates, Corning (R) EAGLE XG. The cross sections are shown in Figs. 1(a) and 2(a), respectively. Each layer for the capacitor and the TFT was prepared by use of a metal mask common to the capacitor and the TFT. After cleaning the glass substrate, a 20-nm-thick Cr layer for the gate electrode was deposited on the glass substrate by thermal evaporation. Then, a 120-nm-thick SiO<sub>2</sub> gate dielectric was deposited by rf sputtering under a condition that a flat surface is obtained.  $^{35)}$  The SiO<sub>2</sub> dielectric had a capacitance per unit area (Cox) of 26.5 nF/cm<sup>2</sup>, which was determined by measurement of the capacitance at 1 kHz. The SiO<sub>2</sub> surface was treated with UV/ozone for 15 min, and was immediately exposed to hexamethyldisilazane (HMDS) vapor at 120 °C for about 30 min. A 45-nm-thick pentacene was deposited on the SiO<sub>2</sub> surface at room temperature. The deposition rate was 0.02 nm/s. Finally, a 45-nm-thick Au layer was deposited as the drain/source electrodes for TFTs and as the top electrode for MOS capacitors. For MOS capacitors, the width ( $W_{dis}$ ) and length ( $L_{dis}$ ) of an uncovered pentacene layer are 200 µm and in the range of 500 to 2500 µm, respectively. For TFTs, the channel width (W) and length (L) were 400 µm and in the range of 55 to 215 µm, respectively.

All the measurements were performed in a dry-nitrogen filled glovebox at room temperature. The capacitance characteristics of MOS capacitors were measured with a source/measurement unit, Keysight Technologies, B2912A. An AC voltage of 100 mVrms superimposed on a DC voltage was applied to the Cr gate electrode. The current characteristics of TFTs were measured with a semiconductor parameter analyzer, Agilent Technologies, B1500A.

#### 4. Results and discussion

#### 4.1 Transistor characteristics

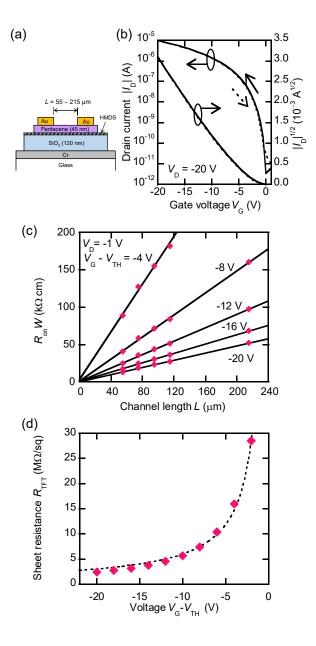

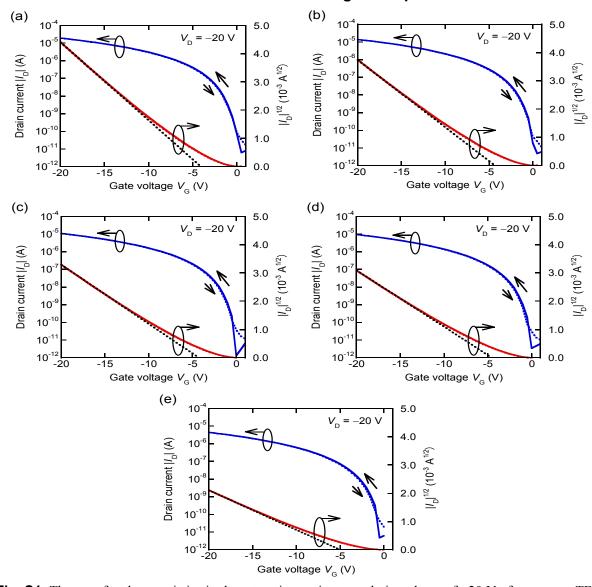

Pentacene TFTs were fabricated on the same substrate for MOS capacitors in order to compare the characteristics of TFTs with those of MOS capacitors. The schematic illustration of the TFT is shown in Fig. 2(a). Figure 2(b) shows the transfer characteristics of a pentacene TFT with  $L = 115 \mu m$  measured at  $V_D = -20 \text{ V}$ . The transfer curve showed characteristics of a typical p-channel organic TFT, and exhibited no large hysteresis in the forward and reverse sweep. For the TFT in Fig. 2(b), the  $\mu_{\text{sat}}$  and  $V_{\text{TH}}$  values in the

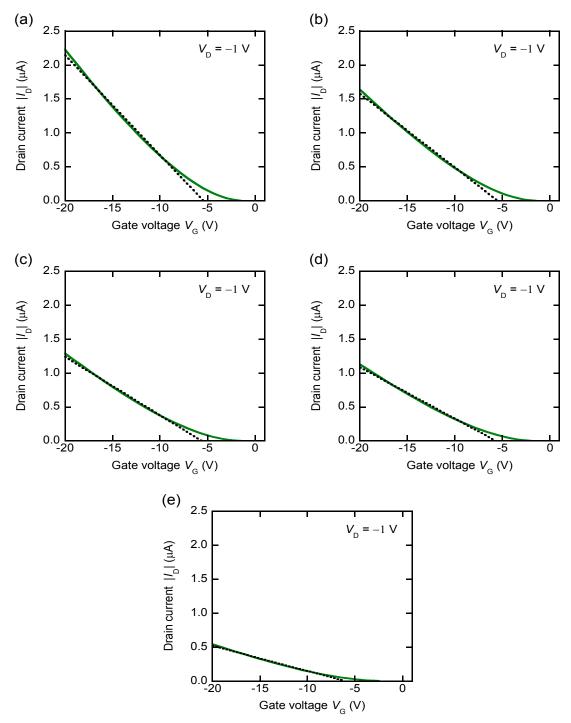

saturation regime were estimated to  $0.86~\rm cm^2~V^{-1}~s^{-1}$  and  $-4.51~\rm V$ , respectively. The transfer characteristics in the saturation and linear regime of pentacene TFTs with different channel lengths are respectively shown in Figs. S1 and S2 in the online supplementary data. The  $\mu_{\rm lin}$ ,  $\mu_{\rm sat}$  and  $V_{\rm TH}$  values calculated from transfer characteristics are summarized in Table I. The  $\mu_{\rm lin}$  and  $\mu_{\rm sat}$  values did not largely depend on L. Although  $\mu_{\rm lin}$  was slight lower than  $\mu_{\rm sat}$ , the difference between  $\mu_{\rm lin}$  and  $\mu_{\rm sat}$  was not large. The averages of  $\mu_{\rm lin}$ ,  $\mu_{\rm sat}$  and  $V_{\rm TH}$  for TFTs with L=55 to 215  $\mu$ m were 0.79 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, 0.84 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and -4.3 V, respectively. The mobilities are in the range of typical values for pentacene TFTs with top contact structure. <sup>13,36</sup>)

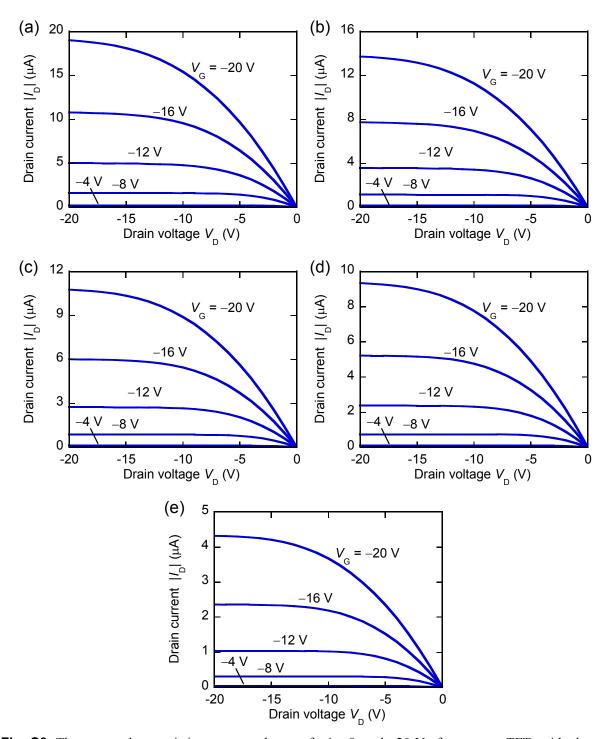

Figure 2(c) shows width-normalized  $R_{\rm on}$  versus L calculated for the TFT of Fig. 2(b). The plots for each  $V_{\rm G}$  is almost on a line. From Eqs. (12) and (13), the slope and the intercept of the line fitting to data of  $R_{\rm on}W$  versus L are equal to  $R_{\rm TFT}$  and ( $R_{\rm C}W$ ), respectively. The  $R_{\rm C}W$  values decreased with an increase of  $|V_{\rm G}-V_{\rm TH}|$ , and 3.24 k $\Omega$  cm for  $V_{\rm G}-V_{\rm TH}=-4$  V and 214  $\Omega$  cm for  $V_{\rm G}-V_{\rm TH}=-20$  V. The  $R_{\rm on}W$  values of the TFT with L=55  $\mu$ m are equal to 52.06 k $\Omega$  cm for  $V_{\rm G}-V_{\rm TH}=-4$  V and 13.12  $\Omega$  cm for  $V_{\rm G}-V_{\rm TH}=-20$  V. The  $R_{\rm C}W$  value is less than 10% of the  $R_{\rm on}W$  value even if  $V_{\rm G}-V_{\rm TH}=-4$  V. The low contact resistance supports no large channel-length dependence of  $\mu_{\rm lin}$  and  $\mu_{\rm sat}$ . The output characteristics of pentacene TFTs with different channel lengths are shown in Fig. S3. It seems that the contact resistance did not largely influence on the output characteristics.

Figure 2(d) shows  $R_{TFT}$  obtained as a function of  $(V_G-V_{TH})$ . A curve fitting to the plots is obtained as

$$R_{\text{TFT}} = \frac{1}{(0.63 \,\text{cm}^2 \,\text{V}^{-1} \,\text{s}^{-1}) \times C_{\text{OX}} |V_{\text{G}} - (V_{\text{TH}} + 0.10 \,\text{V})|}.$$

(14)

The threshold voltage requires a small calibration of 0.10 V. On the other hand, the mobility  $\mu_{\rm I}$  is estimated to be 0.63 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. Although  $R_{\rm TFT}$  does not include the influence of contact resistance, the mobility estimated from Fig. 2(d) is lower than  $\mu_{\rm lin}$  and  $\mu_{\rm sat}$  calculated from transfer curves. The slope of the  $|I_{\rm D}|^{1/2}$ - $V_{\rm G}$  curve in the saturation regime slightly increases with a decrease of  $V_{\rm G}$  as seen in Fig. S1. Also, the  $|I_{\rm D}|$ - $V_{\rm G}$  curve in the linear regime slightly differs from the linearly increase as seen in Fig. S2. The nonlinearity may lead to over-estimation in the mobility estimated from the transfer curve. Thus, it is possible that the mobility estimated from  $R_{\rm TFT}$  is close to the intrinsic mobility in the

#### pentacene layer.

#### 4.2 Characteristics of MOS capacitors

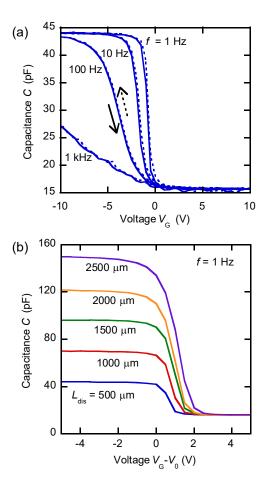

Figure 3(a) shows the capacitance-voltage (C-V) characteristics measured for a pentacene MOS capacitor of  $L_{\rm dis}=500~\mu m$ . The C-V characteristics had no large hysteresis in the forward and reverse sweep. For f=1 and 10 Hz, the capacitance approaches 44.1 pF with a decrease of  $V_{\rm G}$ . The value is close to  $(C_0+C_{\rm SiO2}+C_{\rm OX}~W_{\rm dis}~L_{\rm dis})=42.4$  pF. Thus, the approach is consistent with Eqs. (1), (2) and (7a). The capacitance of 44.1 pF indicates the accumulation of holes to the whole pentacene area of the pentacene/SiO<sub>2</sub>/Cr structure. On the other hand, the capacitance at  $V_{\rm G}>5$  V is about 15.7 pF for f=1 to 1k Hz. The value is close to  $\{C_0+1/(1/C_{\rm SiO2}+1/C_{\rm semi})\}=15.1$  pF. Thus, the capacitance at  $V_{\rm G}>5$  V is consistent with Eqs. (1), (2), and (7b). Note that it is difficult to know the accumulation of holes in the pentacene of the Au/pentacene/SiO<sub>2</sub>/Cr structure from the C-V characteristics. This is because the difference between  $1/(1/C_{\rm SiO2}+1/C_{\rm semi})=4.5$  pF and  $C_{\rm SiO2}=5.3$  pF is small. For f=1 Hz, the C value dramatically decreases between  $V_{\rm G}=-2$  and 0 V. The gate voltage around  $V_{\rm G}=-1$  V corresponds to the threshold voltage  $V_{\rm G}=-1$  in Eq. (9c) for a MOS capacitor.

Figure 3(b) shows the capacitance characteristics measured for pentacene MOS capacitors of  $L_{\rm dis}=500$  to 2500 µm at f=1 Hz. Since the MOS capacitors have different  $V_0$ , the horizontal axis is represented by  $(V_{\rm G}-V_0)$ . Here, the  $V_0$  value roughly estimated from the C-V characteristics was used for Fig. 3(b). For all  $L_{\rm dis}$ , the capacitance decreases down to 15.7 pF with an increase of  $(V_{\rm G}-V_0)$ . Since the MOS capacitors have the same  $S_0$  and  $S_{\rm MOS}$  values, the approach to 15.7 pF is reasonable. On the other hand, the capacitance at  $(V_{\rm G}-V_0)=-5{\rm V}$  depends on  $L_{\rm dis}$ . The value of (C-15.7 pF) is almost proportional to  $L_{\rm dis}$ . This indicates that holes accumulate to the whole pentacene area at  $(V_{\rm G}-V_0)=-5{\rm V}$  even for a long  $L_{\rm dis}$  of 2500 µm.

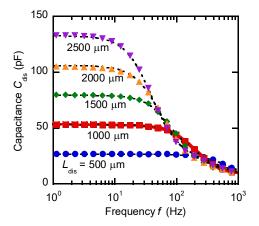

Figure 4 shows the frequency dependence of  $C_{\rm dis}$  at  $(V_{\rm G}-V_0)$  of about  $-10{\rm V}$  for  $L_{\rm dis}=500$  to 2500 µm. For each  $L_{\rm dis}$ , the  $C_{\rm dis}$  value at f=1 Hz almost equals  $(C-15.7~{\rm pF})$  for the C value at  $(V_{\rm G}-V_0)=-5{\rm V}$  shown in Fig. 3(b). The  $C_{\rm dis}$  value gradually decreases with an increase of f. The dotted lines in Fig. 4 were obtained by fitting to the plots of  $C_{\rm dis}$  with Eq. (3). For each  $L_{\rm dis}$ , the plots are almost on the dotted line. This indicates that the frequency dependence of

$C_{\rm dis}$  is reproduced by Eq. (3), which is derived from the equivalent circuit shown in Fig. 1(c). In other words,  $C_{\rm dis}$  at a certain  $V_{\rm G}$  is determined by  $R_{\rm sh}$  independent of f. Thus,  $R_{\rm sh}$  at a certain  $V_{\rm G}$  can be calculated from the  $C_{\rm dis}$  at the  $V_{\rm G}$  of the C-V characteristics using the inverse function of  $g(\alpha)$  defined in Eq. (5). Note that the calculation of  $R_{\rm sh}$  does not require the measurement of the frequency dependence of  $C_{\rm dis}$ . In addition, the plots of  $C_{\rm dis}$  measured are almost on the line fitting to them by use of Eq. (3) without the influence of the contact resistance. This suggests that the influence of the contact resistance on  $C_{\rm dis}$  is negligible in the range of 1 Hz to 1 kHz. The low contact resistance described in Sect 4.1 also supports the suggestion. On the other hand, if a MOS capacitor with low channel resistance and/or large contact resistance is evaluated, the influence of the contact resistance should be considered. In addition, the method is limited to a frequency range in which the presence of trap sites does not affect the admittance of evaluated MOS capacitor. If a MOS capacitor is evaluated at a frequency that trap sites affect the admittance, it is necessary to incorporate the component for the trap site into the admittance.

#### 4.3. Sheet resistance and mobility

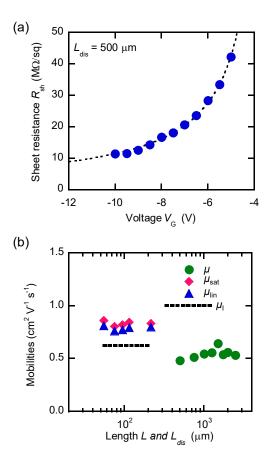

The sheet resistance of pentacene MOS capacitors were calculated on the basis of method described in Sect. 4.2. Figure 5(a) shows the  $V_G$  dependence of  $R_{\rm sh}$  for  $L_{\rm dis}$  = 500  $\mu$ m. Since the C-V characteristic at f = 100 Hz exhibits gradual change to  $V_G$  as seen in Fig. 3(a), the characteristic was used for the calculation of  $R_{\rm sh}$ . The  $\mu$  and  $V_0$  values were estimated by fitting a curve to the plots of  $R_{\rm sh}$  with Eq. (8). The plots are approximately on the dotted line obtained by the fitting. The agreement supports the validity of derivation process for Eq. (8) explained in Sect. 2.2.

Figure 5(b) shows mobilities  $\mu_{\rm sat}$ ,  $\mu_{\rm lin}$  and  $\mu_{\rm I}$  for pentacene TFTs, and  $\mu$  for pentacene MOS capacitors. The  $\mu$  values were calculated from the  $V_{\rm G}$  dependence of  $R_{\rm sh}$ , and were in the range of 0.48 to 0.64 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The average of  $\mu$  was 0.55 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. As shown in Sect. 4.1, the values of  $\mu_{\rm sat}$  and the value of  $\mu_{\rm I}$  were 0.84 and 0.63 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, respectively. On the other hand, the average of  $V_{\rm TH}$  for Eq. (10a), the value of  $V_{\rm TH}$  for Eq. (13), and the average of  $V_{\rm O}$  for Eq. (8) were -4.3, -4.2, and -3.7 V, respectively. The ascending order for  $V_{\rm TH}$  and  $V_{\rm O}$  corresponds to the order of  $\mu_{\rm sat}$ ,  $\mu_{\rm I}$ , and  $\mu$ . The difference among  $V_{\rm TH}$  and  $V_{\rm O}$  may relate to difference among  $\mu_{\rm sat}$ ,  $\mu_{\rm I}$ , and  $\mu$ . Another possibility of the reason is the difference in lateral

DC voltage in the channel layer. Drain current for calculation of the mobility in a TFT is measured under a condition that a DC voltage is applied to the drain electrode. On the other hand, capacitance for calculation of the mobility in a MOS capacitor is measured under a condition that no lateral DC voltage is applied to the channel layer. Thus,  $\mu$  represents the intrinsic carrier mobility in the channel material under no static electric field.

#### 5. Conclusions

We investigated the capacitance characteristics of pentacene MOS capacitors with pentacene area uncovered with the top electrode. The frequency dependence of the capacitance was reproduced using an equation including a capacitance component based on a distributed constant circuit for the uncovered pentacene area. The sheet resistance for the uncovered pentacene area was calculated as a function of gate voltage from the measured capacitance. The mobility of a MOS capacitor with a different length of an uncovered pentacene area was estimated by fitting a curve to the gate-voltage dependence of the sheer resistance. The mobility, which was in the range of 0.48 to 0.64 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, has no large dependence on the length. The mobility is considered as an intrinsic mobility evaluated under a condition of no static lateral electric field.

# **Acknowledgments**

This work was supported by JSPS KAKENHI Grant Numbers 19H02171, 19K15048, and 17H06229.

#### References

- 1) J. S. Chang, A. F. Facchetti, and R. Reuss, IEEE Trans. Emerg. Sel. Topics Circuits Syst. 7, 7 (2017).

- 2) D. M. Taylor, Jpn. J. Appl. Phys. 55, 02BA01 (2016).

- 3) N. T. Kalyani and S. J. Dhoble, Renew. Sust. Energ. Rev. 16, 2696 (2012).

- 4) D. Volz, J. Photon. Energy **6**, 020901 (2016).

- 5) R. Ganesamoorthy, G. Sathiyan, and P. Sakthivel, Sol. Energy Mater. Sol. Cells **161**, 102 (2017).

- 6) A. Wadsworth, M. Moser, A. Marks, M. S. Little, N. Gasparini, C. J. Brabec, D. Baran, and I. McCulloch, Chem. Soc. Rev. 48, 1596 (2019).

- 7) L. Torsi, M. Magliulo, K. Manoli, and G. Palazzo, Chem. Soc. Rev. 42, 8612 (2013).

- 8) J. Liao, H. Si, X. Zhang, and S. Lin, Sensors 19, 218 (2019).

- 9) K. Takimiya, I. Osaka, T. Mori, and M. Nakano, Acc. Chem. Res. 47, 1493 (2014).

- 10) A. F. Paterson, S. Singh, K. J. Fallon, T. Hodsden, Y. Han, B. C. Schroeder, H. Bronstein, M. Heeney, I. McCulloch, and T. D. Anthopoulos, Adv. Mater. **30**, 1801079 (2018).

- 11) C. Groves, Rep. Prog. Phys. **80**, 026502 (2017).

- 12) N. Lu, L. Li, D. Geng, and M. Liu, Org. Electron. 61, 223 (2018).

- 13) M. Kitamura and Y. Arakawa, J. Phys.: Condens. Matter 20, 184011 (2008).

- 14) E. J. Meijer, G. H. Gelinck, E. van Veenendaal, B.-H. Huisman, D. M. de Leeuw, and T. M. Klapwijk, Appl. Phys. Lett. **82**, 4576 (2003).

- D. J. Gundlach, L. Zhou, J. A. Nichols, T. N. Jackson, P. V. Necliudov, and M. S. Shur, J. Appl. Phys. 100, 024509 (2006).

- 16) M. Kitamura, S. Aomori, J. H. Na, and Y. Arakawa, Appl. Phys. Lett. 93, 033313 (2008).

- 17) I. Torres, D. M. Taylor, and E. Itoh, Appl. Phys. Lett. 85, 314 (2004).

- 18) H. Hatta, Y. Miyagawa, T. Nagase, T. Kobayashi, T. Hamada, S. Murakami, K. Matsukawa, and H. Naito, Appl. Sci. **8**, 1493 (2018).

- 19) M. Yun, S. Gangopadhyay, M. Bai, H. Taub, M. Arif, and S. Guha, Org. Electron. 8, 591 (2007).

- 20) K. Gooden, A. Laudari, G. Knotts, and S. Guha, Flex. Print. Electron. 1, 015004 (2016).

- 21) W. T. Wondmagegn, N. T. Satyala, I. Mejia-Silva, D. Mao, S. Gowrisanker, H. N. Alshareef, H. J. Stiegler, M. A. Quevedo-Lopez, R. J. Pieper, and B. E. Gnade, Thin Solid Films **519**,

- 4313 (2011).

- 22) M. Estrada, F. Ulloa, M. Ávila, J. Sánchez, A. Cerdeira, A. Castro-Carranza, B. Iñíguez, L. F. Marsal, and J. Pallarés, IEEE Trans. Electron Devices **60**, 2057 (2013).

- 23) Y. Shao, Y. Zhang, W. He, C. Liu, T. Minari, S. Wu, M. Zeng, Z. Zhang, X. Gao, X. Lu, and J-M Liu, Semicond. Sci. Technol. 30, 035005 (2015).

- 24) A. Nigam, P. R. Nair, M. Premaratne, and V. R. Rao, IEEE Electron Device Lett. **35**, 581(2014).

- 25) Md. Akhtaruzzaman, S. Ohmi, J. Nishida, Y. Yamashita, and H. Ishiwara, Jpn. J. Appl. Phys. 48, 04C178 (2009).

- 26) B. L. Anderson and R. Anderson, *Fundamentals of Semiconductor Devices* (McGraw-Hill Education, NY, USA 2018) 2nd ed. Chap. 7.

- 27) B. H. Hamadani, C. A. Richter, J. S. Suehle, and D. J. Gundlach, Appl. Phys. Lett. **92**, 203303 (2008).

- 28) F. V. Di Girolamo, M. Barra, V. Capello, M. Oronzio, C. Romano, and A. Cassinese, J. Appl. Phys. **107**, 114508 (2010).

- 29) K.-D. Jung, C. A. Lee, D.-W. Park, B.-G. Park, H. Shin, and J. D. Lee, IEEE Electron Device Lett. 28, 204 (2007).

- 30) T. Hayashi, N. Take, H. Tamura, T. Sekitani, and T. Someya, J. Appl. Phys. **115**, 093702 (2014).

- 31) C. Ucurum and H. Goebel, Microelectron. J. 44, 606 (2013).

- 32) D. M. Taylor and N. Alves, J. Appl. Phys. **103**, 054509 (2008).

- 33) M. Ullah, D. M. Taylor, R. Schwödiauer, H. Sitter, S. Bauer, N. S. Sariciftci, and Th. B. Singh, J. Appl. Phys. **106**, 114505 (2009).

- 34) Y. Kimura, Y. Hattori, and M. Kitamura, Compound Semiconductor Week, 2019, [DOI: 10.1109/ICIPRM.2019.8819249].

- 35) H. Takahashi, M. Kitamura, Y. Hattori, and Y. Kimura, Jpn. J. Appl. Phys. **58**, SBBJ04 (2019).

- 36) Y. Kimura, M. Kitamura, A. Kitani, and Y. Arakawa, Jpn. J. Appl. Phys. 55, 02BB14 (2016).

- 37) I. Torres and D. M. Taylor, J. Appl. Phys. 98, 073710 (2005).

# **Figure Captions**

- **Fig. 1.** (a) Cross section of a pentacene MOS capacitor with an uncovered area examined in this study. (b) Structures separated into three parts of Au/SiO<sub>2</sub>/Cr, Au/pentacene/SiO<sub>2</sub>/Cr, and pentacene/SiO<sub>2</sub>/Cr. (c) Distributed constant circuit adopted as an equivalent circuit for the pentacene/SiO<sub>2</sub>/Cr structure uncovered with a top electrode. (d) Microphotograph of a fabricated pentacene MOS capacitor.

- **Fig. 2.** (a) Cross section of a pentacene TFT. (b) Transfer characteristics measured at  $V_D = -20$  V for a pentacene TFT with L = 115 μm. (c) Width-normalized on-resistance  $R_{\rm on}$  W calculated for pentacene TFTs with L = 55, 75, ..., 215 μm. (d) Sheet resistance  $R_{\rm TFT}$  for pentacene TFTs calculated from the width-normalized on-resistance shown in (c); the dashed line is a line fitting to measured  $R_{\rm TFT}$  represented by filled diamonds using Eq. (13).

- **Fig. 3.** (a) C-V characteristics of a pentacene MOS capacitor with  $L_{\rm dis} = 500$  μm measured at f = 1, 10, 100, and 1k Hz. (b) C versus ( $V_{\rm G}$ – $V_0$ ) characteristics of pentacene MOS capacitors with different  $L_{\rm dis}$  measured at 1 Hz.

- **Fig. 4.**  $C_{\text{dis}}$  versus f characteristics of pentacene MOS capacitors with different  $L_{\text{dis}}$  measured at  $(V_{\text{G}}-V_{0})$  of about -10 V. The dasehed lines are lines fitting to measured  $C_{\text{dis}}$  data represented by filled plots using Eq. (3).

- Fig. 5. (a) Sheet resistance  $R_{\rm sh}$  for pentacene MOS capacitors calculated from C-V characteristics; the dashed line is a line fitting to measured  $R_{\rm sh}$  data (filled circule) using Eq. (8). (b) Mobility in the saturation regime ( $\mu_{\rm sat}$ ; filled diamond) and in the linear regime ( $\mu_{\rm lin}$ ; filled triangle) for individual pentacene TFTs; intrinsic mobility  $\mu_{\rm l}$  for pentacene TFTs (dashed line); carrier mobility  $\mu$  for pentacene MOS capacitors (filled circle).

**Table I.** Electrical properties of pentacene TFTs with different channel lengths: mobility in the linear regime  $\mu_{lin}$ , mobility in the saturation regime  $\mu_{sat}$ , and threshold voltage  $V_{TH}$ .

| <i>L</i> (μm) | $\mu_{ m lin} \ ({ m cm \ V^{-1} \ s^{-1}})$ | $\mu_{ m sat} \ ({ m cm~V^{-1}~s^{-1}})$ | <i>V</i> <sub>ТН</sub> (V) |

|---------------|----------------------------------------------|------------------------------------------|----------------------------|

| 55            | 0.81                                         | 0.86                                     | -4.2                       |

| 75            | 0.76                                         | 0.80                                     | -4.3                       |

| 95            | 0.77                                         | 0.82                                     | -4.5                       |

| 115           | 0.79                                         | 0.84                                     | -4.7                       |

| 215           | 0.80                                         | 0.83                                     | -3.5                       |

Fig.1.

Fig. 2.

Fig. 3.

Fig. 4.

Fig. 5.

# Evaluation of organic metal-oxide-semiconductor capacitors based on a distributed constant circuit

Yoshinari Kimura\*, Yoshiaki Hattori, and Masatoshi Kitamura\*\*

Department of Electrical and Electronic Engineering, Graduate School of Engineering, Kobe University, Kobe 657-8501, Japan

\*E-mail address: kimura@eedept.kobe-u.ac.jp

#### Supplementary data

#### 1. Transfer characteristics in the saturation regime of pentacene TFTs

**Fig. S1.** The transfer characteristics in the saturation regime at a drain voltage of -20 V of pentacene TFTs. The channel lengths are (a) 55 μm, (b) 75 μm, (c) 95 μm, (d) 115 μm, and (e) 215 μm. The solid and dotted, colored lines are data taken from positive-to-negative (forward) and negative-to-positive (reverse) gate-voltage sweeps, respectively. The black dotted line is a line fitting to the  $|I_D|^{1/2}$ - $V_G$  curve, being for estimation of  $\mu_{\rm sat}$  and  $V_{\rm TH}$ .

<sup>\*\*</sup>E-mail address: kitamura@eedept.kobe-u.ac.jp

### 2. Transfer characteristics in the linear regime of pentacene TFTs

**Fig. S2.** The transfer characteristics in the linear regime at a drain voltage of -1 V of pentacene TFTs. The channel lengths are (a) 55 μm, (b) 75 μm, (c) 95 μm, (d) 115 μm, and (e) 215 μm. The solid and dotted, colored lines are data taken from positive-to-negative (forward) and negative-to-positive (reverse) gate-voltage sweeps, respectively. The black dotted line is a line fitting to the  $|I_D|$ - $V_G$  curve, being for estimation of  $\mu_{lin}$ .

# 3. Output characteristics of pentacene TFTs

**Fig. S3.** The output characteristics at gate voltages of -4, -8, and -20 V of pentacene TFTs with channel lengths of (a) 55  $\mu$ m, (b) 75  $\mu$ m, (c) 95  $\mu$ m, (d) 115  $\mu$ m, and (e) 215  $\mu$ m.