PDF issue: 2025-12-05

Energy distribution of interface states generated by oxygen plasma treatment for control of threshold voltage in pentacene thinfilm transistors

Kimura, Yoshinari Hattori, Yoshiaki Kitamura, Masatoshi

(Citation)

Journal of Physics D: Applied Physics, 53(50):505106

(Issue Date) 2020-12-09

(Resource Type) journal article

(Version)

Accepted Manuscript

(Rights)

© 2020 IOP Publishing Ltd. This is the Accepted Manuscript version of an article accepted for publication in Journal of Physics D: Applied Physics. IOP Publishing Ltd is not responsible for any errors or omissions in this version of the manuscript or any version derived from it. The Version of Record is available online at…

(URL)

https://hdl.handle.net/20.500.14094/90007555

# Energy distribution of interface states generated by oxygen plasma treatment for control of threshold voltage in pentacene thin-film transistors

#### Yoshinari Kimura, Yoshiaki Hattori and Masatoshi Kitamura

Department of Electrical and Electronic Engineering, Graduate School of Engineering, Kobe University, 1-1 Rokkodai-cho, Nada, Kobe, Japan

E-mail: kimura@eedept.kobe-u.ac.jp and kitamura@eedept.kobe-u.ac.jp

Received xxxxxx Accepted for publication xxxxxx Published xxxxxx

#### **Abstract**

Pentacene metal-oxide-semiconductor (MOS) capacitors with a SiO<sub>2</sub> dielectric treated by oxygen plasma have been studied by capacitance-voltage (C-V) measurement to investigate the energy distribution of the interface states. Oxygen plasma treatment, which is used for control of the threshold voltage in pentacene thin-film transistors, shifted the C-V curves of pentacene MOS capacitors to positive gate voltage as well as the transfer curves of pentacene TFTs. The shift is explained by electrons captured at interface states generated by oxygen plasma treatment. The interface states capturing the electrons are expected to locate at low energy levels. The energy distribution of the interface states locating at middle or high energy levels was extracted by a method equivalent to Terman method. By use of the method in two steps, the interface state densities distributed at middle and high energy levels ( $D_{\rm M}$  and  $D_{\rm H}$ ) were separately obtained. The  $D_{\rm M}$  and  $D_{\rm H}$  were of the order of  $10^{10}-10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup>, and increased with an increase in plasma treatment time.

Keywords: interface states, MOS capacitors, C-V measurement, pentacene, oxygen plasma

## 1. Introduction

Organic thin-film transistors (TFTs) have attracted considerable attention because of their potential applications to large area, mechanically flexible, lightweight, and cost-effective devices [1-4]. In addition to the advantage, field-effect mobilities in organic TFTs have reached to about 10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> [5-9], which is close to those of oxide TFTs practically used in flat panel displays. For practical application, threshold voltage control in organic TFTs is an important issue as well as improvement of the performance. Some groups have been attempting threshold voltage control in organic TFTs using

various methods such as using self-assembled monolayers (SAM) on a gate dielectric [10-13], utilizing new polymer gate dielectrics [14-16], doping into organic layers [17-19], choosing gate metals [20-22], adjusting parasitic resistance [23,24], and using multi gate structures [25,26].

Another approach of threshold voltage control adopted oxygen plasma treatment to the surface of gate dielectrics [27-30]. Oxygen plasma treatment has been used to obtain a hydrophilic surface for formation of a SAM on a gate dielectric [31,32]. Thus, the threshold voltage control by oxygen plasma treatment does not require an additional process if the organic TFT requires a SAM layer. In addition,

xxxx-xxxx/xx/xxxxxx 1 © xxxx IOP Publishing Ltd

the threshold voltage gradually changes with plasma treatment time. The continuous change is suitable for application to integrated circuits of organic TFTs. In actual, we applied pentacene TFTs with the controlled threshold voltage to logic circuits [33,34]. Since the threshold voltage shifts to positive gate voltage with plasma treatment time, the threshold voltage change is probably attributed to electrons captured at interface states generated by oxygen plasma treatment. Although a concern is that the change is temporary, we reported that gate bias stress does not negate the threshold voltage change provided by oxygen plasma treatment [29]. This implies that the interface states work as deep traps at low energy levels for electrons. On the other hand, the presence of electron traps at middle or high energy levels has been unclear.

For Si metal-oxide-semiconductor (MOS) field-effect transistors (FET), electron states at the interface between semiconductors and gate dielectric have been examined using some methods including electron spin resonance spectroscopy [35], current-voltage measurements [36], and capacitancevoltage (C-V) measurements [37,38]. Among the methods, C-V measurement has an advantage that the measurement is performed without light irradiation and elevated temperature. Since organic TFTs are generally sensitive to light and temperature change, C-V measurement is suitable for evaluation of organic TFTs and MOS capacitors. In actual, interface traps in organic MOS capacitors have been investigated by C-V measurement [39-42]. Also, we have reported C-V characteristics of pentacene MOS capacitors with a large uncovered pentacene area [43]. Thus, C-V measurement will be used for evaluation of organic MOS capacitors with a SiO<sub>2</sub> dielectric treated by oxygen plasma.

In this paper, we report C-V characteristics of pentacene MOS capacitors with a SiO<sub>2</sub> gate dielectric treated by oxygen plasma to examine the energy distribution of interface states generated by the treatment. First, we show current-voltage characteristics of pentacene TFTs to compare the characteristics with those of the MOS capacitors. Then, C-V characteristics of the MOS capacitors are shown. The energy distribution of the interface states is calculated from the C-Vcharacteristics using a method equivalent to Terman method. [44-47]. The purpose of this study is to clarify the distribution, in particular, at middle or high energy levels. In addition, the originality of this study is that the C-V characteristics of a MOS capacitor without oxygen plasma treatment is used for a reference of the method. Actually, the C-V characteristics shifted by the threshold voltage change is adopted as the reference, and the influence of interface states at low energy levels, which relate to the threshold voltage change, is eliminated.

#### 2. Analytical method

#### 2.1 Threshold voltage of TFTs

Organic TFTs generally operate in the accumulation mode. The threshold voltage ( $V_{\rm TH}$ ) for an accumulation mode of MOS FETs equals a flat band voltage and is given by

$$V_{\rm TH} = \frac{\Phi_{\rm M} - \Phi_{\rm S}}{q} - \frac{Q}{C_{\rm OX}} \tag{1}$$

where q is the electron elementary charge,  $\Phi_{\rm M}$  and  $\Phi_{\rm S}$  are the work functions of the gate electrode and the organic semiconductor, respectively,  $C_{\rm OX}$  is the gate capacitance per unit area, and Q is the charge density [48]. Q is written as

$$Q = Q_{\rm S} + \int_0^d \frac{x}{d} \rho_{\rm OX}(x) dx \tag{2}$$

where  $Q_S$  is the surface charge density at the interface between the gate dielectric and the semiconductor, and  $\rho_{OX}(x)$  is the charge density per unit volume in the gate dielectric. The interfaces of the gate dielectric for the gate metal and the semiconductor are defined as x = 0 and d, respectively.

In this study,  $Q_S$  is assumed to be mainly induced by oxygen plasma treatment. Previous our work supports the assumption [29,30]. In addition, the work shows that  $Q_S$  is expressed as

$$Q_{\rm S} = q_{\rm P} t_{\rm P} \tag{3}$$

where  $q_P$  is the surface charge density per unit time induced by oxygen plasma treatment, and  $t_P$  is the plasma treatment time. Sbstituting Eqs. (2) and (3) into Eq. (1), the  $V_{TH}$  is written as

$$V_{\rm TH} = \frac{\Phi_{\rm M} - \Phi_{\rm S}}{q} - \frac{1}{C_{\rm OX}} (q_{\rm P} t_{\rm P} + Q_0)$$

(4)

where

$$Q_0 = \int_0^d \frac{x}{d} \rho_{\rm OX}(x) dx . \tag{5}$$

Under this assumption, the  $V_{\rm TH}$  linearly changes as a function of  $t_{\rm P}$ . Equation (4) is used for estimation of  $q_{\rm P}$  and  $Q_0$  in Sect. 4.

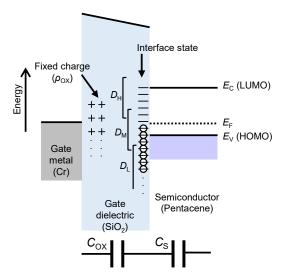

# 2.2 Characteristics of MOS capacitors

Figure 1 shows schematic band diagram of a  $SiO_2$ /pentacene MOS capacitor examined in this study. We attempt to estimate the interface state density by C-V measurement. The total capacitance per unit area of the MOS capacitor ( $C_G$ ) is expressed as

$$1/C_{\rm G} = 1/C_{\rm OX} + 1/C_{\rm S.} \tag{6}$$

where  $C_{\rm S}$  is the capacitance per unit area of the pentacene layer. The capacitances  $C_{\rm G}$  and  $C_{\rm S}$  are functions of the gate voltage ( $V_{\rm G}$ ) and are represented as  $C_{\rm G}(V_{\rm G})$  and  $C_{\rm S}(V_{\rm G})$ . The interface state density is experimentally classified into three groups denoted as  $D_{\rm L}$ ,  $D_{\rm M}$ , and  $D_{\rm H}$ . The  $D_{\rm L}$ ,  $D_{\rm M}$ , and  $D_{\rm H}$  are expected to be roughly distributed in ascending order shown in Fig. 1. Because the fixed charge in the gate dielectric is expect to be positive, it is represented by a plus sign.

Flat band voltage ( $V_{\rm FB}$ ) of a MOS capacitor without inversion mode is equal to  $V_{\rm TH}$  as described above, and is written as

Figure 1. Schematic band diagram of a SiO<sub>2</sub>/pentacene MOS structure.

$$V_{\rm FB} = \frac{\Phi_{\rm M} - \Phi_{\rm S}}{q} - \frac{Q}{C_{\rm OX}}.$$

(7)

When a  $V_{\rm FB}$  value is experimentally obtained, Q is calculated from Eq. (7) as well as Q in Eq. (1). Also,  $Q_{\rm S}$ ,  $Q_{\rm 0}$ , and  $q_{\rm P}$  can be calculated from  $V_{\rm TH}$  for TFTs or  $V_{\rm FB}$  for MOS capacitors. Thus, these values calculated from  $V_{\rm TH}$  and  $V_{\rm FB}$  are denoted such as  $Q_{\rm S}$ ,  $_{\rm TFT}$  and  $Q_{\rm S}$ ,  $_{\rm MOS}$ , respectively, when distinguish them. Also, the  $V_{\rm FB}$  value is used in an equation for surface potential shown below. An issue is how to determine  $V_{\rm FB}$  experimentally. In this study, the  $V_{\rm FB}$  value is experimentally determined as

$$C_{\rm S}(V_{\rm FB}) = 20 \, \min[C_{\rm S}(V_{\rm G})].$$

(8)

Although this definition is not standard, Eq. (8) for a MOS capacitor provides a  $V_{\rm FB}$  value close to a  $V_{\rm TH}$  value obtained from the current characteristics of a TFT prepared under the same condition as that of the MOS capacitor. Experimental results shown in Sect. 4 justify the definition of Eq. (8). Physically, Eq. (8) means that one twentieth thickness of a pentacene layer acts as insulator. In this study, the average thickness of a pentacene is about 22.5 nm as explained later. Thus, the one twentieth thickness is about 1.1 nm.

The interface state density  $(D_{\rm it})$  in an evaluated MOS capacitor is generally obtained as a function of the surface potential at the interface between the semiconductor and the gate dielectric. The surface potential  $\Psi_{\rm S}$  is expressed as [44,49]

$$\Psi_{\rm S}(V_{\rm G}) = V_{\rm G} - V_{\rm FB} - \int_{V_{\rm FB}}^{V_{\rm G}} \left(\frac{C_{\rm G}(V)}{C_{\rm OX}}\right) dV$$

(9)

as a function of  $V_{\rm G}$  and is constructed by using  $V_{\rm FB}$  and  $C_{\rm G}(V_{\rm G})$ . The calculation of  $D_{\rm it}$  requires the C-V characteristic of a MOS capacitor, which ideally has no interface state, as a reference. Here, the surface potential and the total capacitance of the reference MOS capacitor are denoted as  $\Psi_{\rm ref}(V_{\rm G})$  and  $C_{\rm ref}(V_{\rm G})$ , respectively. Using these notations,  $D_{\rm it}$  can be given by

$$D_{\rm it}(\Psi_{\rm S}(V_{\rm G})) = \lim_{\Delta V_{\rm G} \to 0} \frac{1}{q^2} \frac{\Delta Q_{\rm G} - \Delta Q_{\rm ref}}{\Psi_{\rm S}(V_{\rm G} + \Delta V_{\rm G}) - \Psi_{\rm S}(V_{\rm G})}$$

(10)

where

$$\Delta Q_{\rm G} = \int_{V_{\rm G}}^{V_{\rm G} + \Delta V_{\rm G}} C_{\rm G}(V) dV \tag{11a}$$

$$\Delta Q_{\text{ref}} = \int_{V_{G}'}^{V_{G}' + \Delta V_{G}'} C_{\text{ref}}(V) dV$$

(11b)

The  $V_{G}'$  and  $\Delta V_{G}'$  are defined as the following equations:

$$\Psi_{\text{ref}}(V_{\text{G}}') = \Psi_{\text{S}}(V_{\text{G}}), \tag{12a}$$

$$\Psi_{\text{ref}}(V_{\text{G}}' + \Delta V_{\text{G}}') = \Psi_{\text{S}}(V_{\text{G}} + \Delta V_{\text{G}}). \tag{12b}$$

The  $\Delta Q_{\rm G}$  and  $\Delta Q_{\rm ref}$  are charges stored in the evaluated and reference MOS capacitors, respectively, when the surface potential changes from  $\Psi_{\rm S}(V_{\rm G})$  to  $\Psi_{\rm S}$  ( $V_{\rm G}$ +  $\Delta V_{\rm G}$ ).  $V_{\rm G}$ ' and  $\Delta V_{\rm G}$ ' are calculated from Eq. (12a) when values of  $V_{\rm G}$  and  $\Delta V_{\rm G}$  are decided.

Equation (10) is mathematically equivalent to

$$D_{\rm it}(\Psi_{\rm S}) = \frac{C_{\rm OX}}{q^2} \frac{d(V_{\rm G} - V_{\rm G}')}{d\Psi_{\rm S}}$$

(13)

known as Terman method [44-47]. Derivation of Eq. (13) from Eq. (10) is written in the supplemental data. A calculated  $D_{\rm it}$  value generally contains numerical errors. Thus, a value calculated from Eq. (10) may be slightly different from that calculated from Eq. (13). In actual, the difference was less than 1 % for calculation of  $D_{\rm M}$  and less than 5 % for calculation of  $D_{\rm H}$ . In this paper,  $\Delta V_{\rm G} = 0.5$  V and  $D_{\rm it}$  calculated from Eq. (10) is shown. We show Eq. (10) for intuitive understanding that  $D_{\rm it}$  directly relates to the difference between the stored charges. Also, we can see the increases in accumulated charges  $\Delta Q_{\rm G}$  and  $\Delta Q_{\rm ref}$  in the calculation process. Since  $V_{\rm G}$  is discrete as  $\Delta V_{\rm G} = 0.5$  V, it is necessary to approximately perform Eqs. (9)-(13). The calculation was performed by linear interpolation.

In general, other methods have been also used for determination of interface states [49]. One of them is conductance method that requires measurement of continuous frequency dependence of the admittance. On the other hand, Terman method does not require measurement of frequency dependence of capacitance. In addition, Terman method does not directly contain conductance element. Therefore, we used the method equivalent to Terman method. The method may be suitable for evaluation of a MOS capacitor having a low-mobility channel material such as an organic semiconductor. This is because the low conductivity in the material possibly causes unintentional error in conductance method.

#### 3. Experimental method

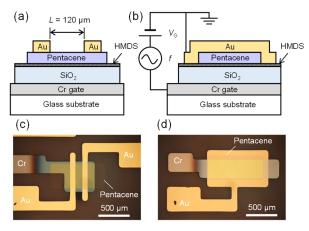

Figure 2(a) and 2(b) shows cross sections of a pentacene TFT and a MOS capacitor, respectively. The fabrication process is almost the same as that of our previous study except for oxygen plasma treatment [43]. TFTs and MOS capacitors were fabricated on glass substrates, Corning (R) EAGLE XG.

**Figure 2.** Cross sections of (a) a pentacene TFT and (b) a pentacene MOS capacitor. Microphotographs of (c) a fabricated pentacene TFT and (d) a fabricated pentacene MOS capacitor.

Each layer for the TFT and capacitor was deposited through a metal mask. First, a 20-nm-thick Cr layer was deposited as a gate electrode. Then, a SiO<sub>2</sub> layer was deposited as a gate dielectric by rf sputtering. The SiO<sub>2</sub> layer has a thickness of about 120 nm and a capacitance per unit area ( $C_{OX}$ ) of about 27 nF cm<sup>-2</sup>. Measured  $C_{\rm OX}$  values are determined as the average value near to the maximum of  $C_G$  in accumulation regime from C-V measurement, and are shown in Table 2. The substrates were cleaned with acetone, isopropanol, and UV/ozone. Then, the SiO<sub>2</sub> surfaces were exposed to oxygen plasma for a time  $(t_P)$  of 10 to 30 s under a condition of an  $O_2$ flow rate of 100 mL min<sup>-1</sup> and an AC power for plasma generation of 9.2 W. After oxygen plasm treatment, or UV/ozone treatment as a reference without oxygen plasma treatment, the substrate was immediately exposed to hexamethyldisilazane (HMDS) vapor for 30 min at 120°C. The TFT without oxygen plasma treatment is represented as  $t_P$ = 0 afterhere. A 45-nm-thick pentacene layer was deposited at a rate of 0.2 Å/s on the substrate of room temperature. Finally, a 45-nm-thick Au layer was thermally deposited as the top electrode of MOS capacitors and as the drain/source electrode of TFTs. For TFTs, the channel width (W) is 400 µm and the channel length (L) is 60, 80, 100, or 120  $\mu$ m. For MOS capacitors, the MOS capacitor area of Au/pentacene/SiO<sub>2</sub>/Cr structure is  $2.7 \times 10^{-3}$  cm<sup>2</sup>. The MOS capacitor has an area of Au/SiO<sub>2</sub>/Cr structure, which is  $0.3 \times 10^{-3}$  cm<sup>2</sup>. Capacitance values excluding the capacitance of the Au/SiO<sub>2</sub>/Cr area are shown as the capacitance of a MOS capacitor. Pentacene MOS capacitors and TFTs for a certain  $t_P$  value were fabricated at the same glass substrate.

All characteristics were examined in a dry-nitrogen filled glovebox at room temperature. The current-voltage characteristics of TFTs were measured by using a semiconductor parameter analyzer, Agilent Technologies, B1500A. The capacitance characteristics of MOS capacitors were measured by using a source/measurement unit, Keysight Technologies, B2912A. A 100-mVrms AC voltage of a

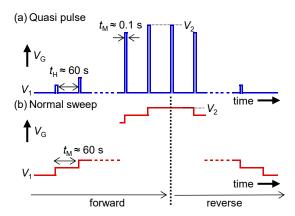

**Figure 3.** Waveforms of  $V_{\rm G}$  applied for C-V measurement in (a) a quasipulse wave and (b) a normal sweep. A 100-mVrms AC voltage of a frequency of 200 Hz is superimposed on the  $V_{\rm G}$  voltage for C-V measurement.

frequency of 200 Hz superimposed on a DC voltage ( $V_G$ ) was applied to the Cr electrode with respect to the Au electrode as seen in Fig. 2(b). The source/measurement unit exhibits good accuracy at frequencies of the order of 10 to 100 Hz rather than high frequencies. Thus, we measured C-V characteristics at a frequency of 200 Hz. The source/measurement unit can output a DC voltage more than 30 V for C-V measurement without an external power supply.

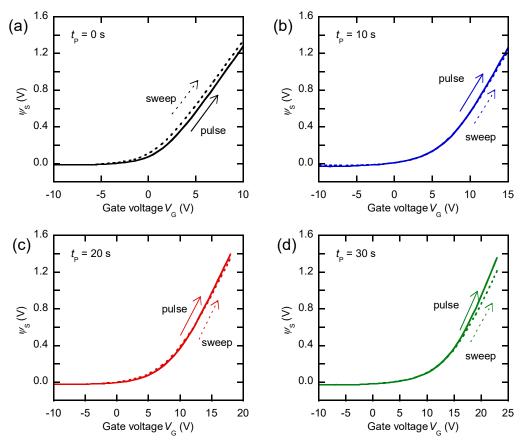

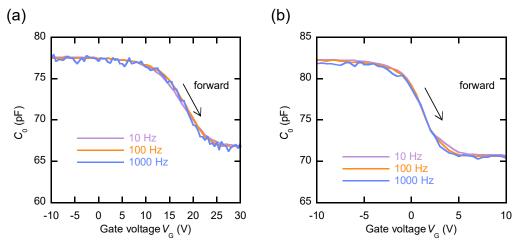

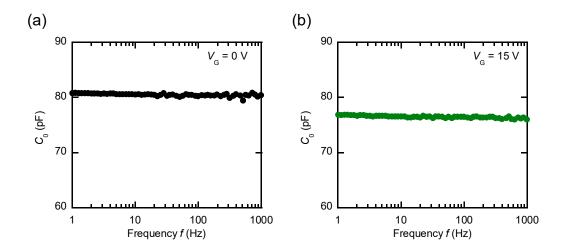

For MOS capacitors, the C-V measurement was performed in the range of  $V_G = V_1$  to  $V_2$  where  $V_1 = -10$  V,  $V_2 = 10$ , 15, 18, and 23 V for  $t_P = 0$ , 10, 20, and 30 s, respectively. To change the number of charges trapped in the interface states at a certain  $V_{\rm G}$ , we adopted two time-profiles of applied  $V_{\rm G}$ shown in Figs. 3(a) and 3(b). One is a quasi-pulse wave and the other is a normal sweep. The holding voltage in the quasipulse wave, which was set at -10 V, contributes to suppression of unintended charge transfer under a certain  $V_G$ .  $C_G$  measured by a quasi-pulse wave and a normal sweep is denoted as  $C_{G_i}$ <sub>pulse</sub> and  $C_{G, \text{sweep}}$  when distinguish them. In this study, the characteristics of capacitance is probably dominated by pulse width,  $t_{\rm M}$ , shown in fig. 3(a) rather than frequency. This is because the characteristics of capacitance measured at a normal sweep is different from that measured at quasi pulses as shown in Fig. 7. Particularly, C-V characteristics did not largely depend on frequency as seen in Fig. S6 of supplemental data. In addition, capacitance measured at a certain  $V_{\rm G}$  did not largely depends on frequency as seen in Fig. S7 of supplemental data.

#### 4. Results and discussion

#### 4.1 Transistor characteristics

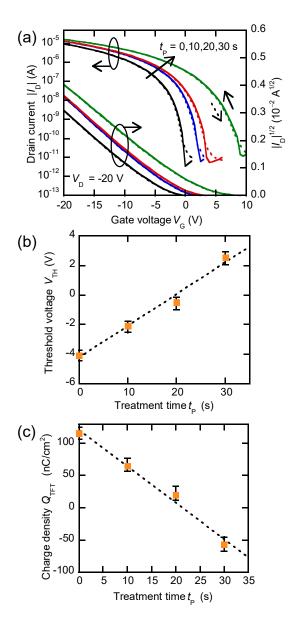

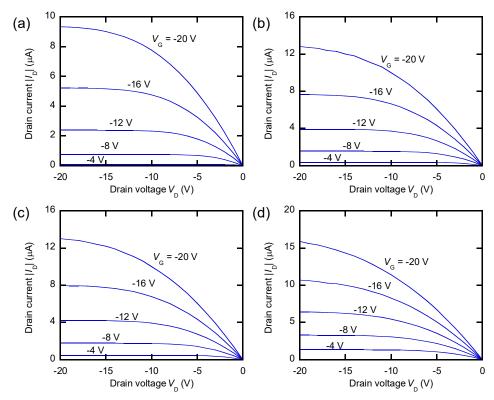

Figure 4(a) shows the drain current ( $I_D$ ) versus gate voltage ( $V_G$ ) characteristics of pentacene TFTs with  $L = 120 \mu m$  in the saturation regime at a drain voltage ( $V_D$ ) of -20 V. The  $I_D$ - $V_G$

**Figure 4.** (a) Drain current versus gate voltage characteristics measured  $V_{\rm D} = -20$  V for pentacene TFTs having SiO<sub>2</sub> gate dielectrics treated by oxygen plasma for  $t_{\rm P} = 0$ , 10, 20, and 30 s. (b) Threshold voltages estimated from the transfer characteristics of pentacene TFTs. (c) Charge density  $Q_{\rm TFT}$  calculated from the threshold voltages in (b). The top and bottom of the error bar indicate the maximum and minimum values measured, respectively.

characteristics were obtained by a normal sweep from a positive  $V_{\rm G}$  to -20 V, and the reverse sweep from -20 V to the positive  $V_{\rm G}$ . The plasma treatment time  $t_{\rm P}$  is 0, 10, 20, and 30 s. The  $I_{\rm D}\text{--}V_{\rm G}$  curves shift to positive gate voltages with increase in  $t_{\rm P}$ . For  $|I_{\rm D}| > 10^{-10}$  A, the  $I_{\rm D}\text{--}V_{\rm G}$  curves do not exhibit large hysteresis in the forward and reverse sweeps. For  $|I_{\rm D}| < 10^{-10}$  A, a small hysteresis appears in the sweep. The hysteresis may relate to shallow traps shown as  $D_{\rm M}$  and/or  $D_{\rm H}$  in Fig. 1. The output characteristics are shown in Fig. S1 of supplemental data.

**Table 1** Properties of pentacene TFTs estimated from the transfer characteristics: field-effect mobilities in the saturation regime  $\mu_{\text{SAT}}$ , threshold voltage  $V_{\text{TH}}$ , sub-threshold swing S, charge densities  $Q_{\text{S, TFT}}$ . The value after  $\pm$  indicates the standard deviation.

| <i>t</i> <sub>P</sub> (s) | $\mu_{SAT}$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | <i>V</i> <sub>TH</sub> (V) | S<br>(V/decade) | $Q_{ m S,TFT}$ (nF/cm <sup>2</sup> ) |

|---------------------------|----------------------------------------------------------------|----------------------------|-----------------|--------------------------------------|

| 0                         | $0.84 \pm 0.05$                                                | $-4.08 \pm 0.21$           | $0.56 \pm 0.14$ | -                                    |

| 10                        | $0.82 \pm 0.04$                                                | $-2.09 \pm 0.27$           | $0.65 \pm 0.04$ | $-53.0 \pm 7.9$                      |

| 20                        | $0.88 \pm 0.06$                                                | $-0.47 \pm 0.24$           | $0.72 \pm 0.33$ | $-100.7 \pm 6.2$                     |

| 30                        | $0.76 \pm 0.06$                                                | $2.53 \pm 0.38$            | $1.00 \pm 0.14$ | $-177.6 \pm 9.6$                     |

The filed-effect mobilities in the saturation regime ( $\mu_{SAT}$ ),  $V_{\rm TH}$ , and sub-threshold swing (S) are summarized in Table 1. These are the average measured for six to nine TFTs fabricated at the same substrate for each  $t_P$ . The  $\mu_{SAT}$  and  $V_{TH}$  values are calculated by fitting a line to  $|I_D|^{1/2}$ - $V_G$  plots as shown in Fig. S3 of supplemental data. The average  $\mu_{SAT}$  values, calculated using  $C_{\rm OX}$  value shown in Table 2, are in the range of 0.76 to  $0.88 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , and does not largely depend on  $t_P$ . On the other hand,  $V_{\text{TH}}$  increases with an increase in  $t_{\text{P}}$ . In Fig. 4(b),  $V_{\rm TH}$  is plotted with respect to  $t_{\rm P}$ . By assuming values of  $\Phi_{\rm M}$  and  $\Phi_{\rm S}$ , Q in Eq. (2) can be calculated as a function of  $t_{\rm P}$ . We used  $\Phi_{\rm M}$  = 4.8 eV and  $\Phi_{\rm S}$  = 4.5 eV for the calculation. Although Cr was used for the gate metal, the surface of Cr is easily oxidized in general. Thus, we adopted work function of 4.8 eV reported for  $Cr_2O_3$  [50] as  $\Phi_M$ . The  $\Phi_S$  value corresponds to the Fermi energy of pentacene. Some groups have reported the Fermi energy of pentacene deposited on a underlayer as following: -4.35 eV on Au (5.2 eV) [51], -4.20 eV on Au (4.65 eV) [52], -4.53 eV on Au (4.8 eV) [53], and -4.57 eV on MoO<sub>3</sub> (6.95 eV) [54]. The value in the parentheses is the work function of the underlayer. Since the work function of 4.8 eV for Au reported in [53] equals 4.8 eV for  $C_2O_3$ , we used 4.5 eV as  $\Phi_S$ .

Figure 4(c) shows  $Q_{\rm TFT}$  calculated from Eq. (1). The  $Q_{\rm S}$  (=  $q_{\rm P}$   $t_{\rm P}$ ) values are appended in Table 1. From the fitting curve,  $Q_0$  and  $q_{\rm P}$  are estimated to be 120 .5 nC/cm² and -5.64 nC cm² s¹¹. By assuming that positive charges are uniformly distributed in SiO<sub>2</sub>,  $\rho_0$  is calculated as  $2.0 \times 10^{-2}$  C/cm³ which corresponds to positive charges of  $1.2 \times 10^{17}$  cm⁻³. The negative  $q_{\rm P}$  value suggests that oxygen plasma treatment generates interface states serving as electron traps.  $Q_0$  and  $q_{\rm P}$  values have also been reported in our papers [29,33,34]. Note that  $Q_0$  value depends on ( $\Phi_{\rm M}$  -  $\Phi_{\rm S}$ ) values and contains error caused by the estimation errors of  $\Phi_{\rm M}$  and  $\Phi_{\rm S}$  values used. On the other hand,  $Q_{\rm S}$  and  $q_{\rm P}$  are not affected by the estimation error.

#### 4.2 MOS capacitor characteristics

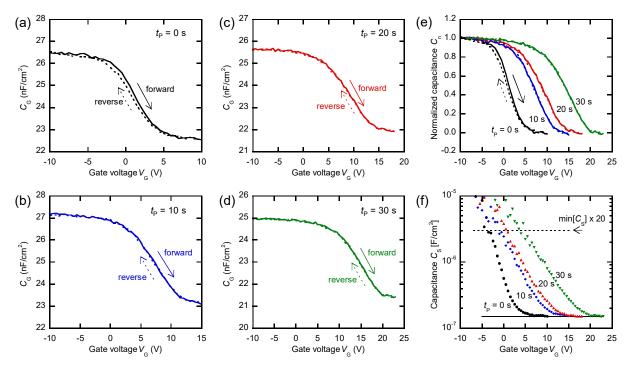

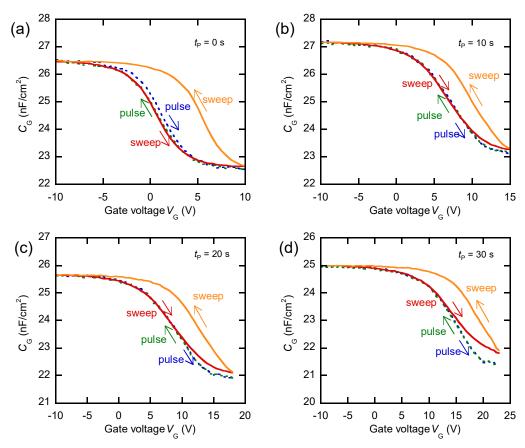

Figures 5(a)-5(d) shows the  $C_{\rm G, pulse}$  versus  $V_{\rm G}$  characteristics of pentacene MOS capacitors for  $t_{\rm P}=0$ , 10, 20, and 30 s. Properties extracted from the  $C_{\rm G, pulse}$  characteristics are summarized in Table 2. For  $t_{\rm P}=10$ , 20, and 30 s, the C-V

Figure 5. (a) C-V characteristics obtained by applying quasi-pulse waves of forward (solid line) and reverse (dotted line) for t<sub>P</sub> = (a) 0 s, (b) 10 s, (c) 20

Table 2 Properties of pentacene MOS capacitors

| <i>t</i> <sub>P</sub> (s) | C <sub>OX</sub> (nF/cm <sup>2</sup> ) | $ \min[C_{\rm S}] \\ (\rm nF/cm^2) $ | <i>V</i> <sub>FB</sub> (V) | Q <sub>S,MOS</sub> (nF/cm <sup>2</sup> ) | $ Q_{ m S,MOS}/q  \  m (cm^{-2})$ |

|---------------------------|---------------------------------------|--------------------------------------|----------------------------|------------------------------------------|-----------------------------------|

| 0                         | 26.5                                  | 155                                  | -3.57                      | -                                        | -                                 |

| 10                        | 27.2                                  | 158                                  | -0.77                      | -69.6                                    | 4.4×10 <sup>11</sup>              |

| 20                        | 25.6                                  | 153                                  | 0.64                       | -107                                     | 6.7×10 <sup>11</sup>              |

| 30                        | 25.0                                  | 153                                  | 3.61                       | -181                                     | 1.1×10 <sup>12</sup>              |

characteristics do not exhibit hysteresis in the forward and reverse measurement. This suggests that electrons trapped at the interface states by applying  $V_{\rm G} > -10$  V leave from the states when applying  $V_G = -10 \text{ V}$  for a holding time of about 60 s. On the other hand, the C-V characteristic for  $t_P = 0$  s exhibits a small hysteresis. The  $C_{G, pulse}$  in the reverse measurement is slightly lower than that in the forward measurement. This may be due to the presence of hole traps at the interface without oxygen plasma treatment. The reason has been under investigation. The  $C_{G, \text{sweep}}$  is shown with  $C_{G, \text{pulse}}$ in Fig. S3 of supplemental data. All  $C_{G, \text{sweep}}$ - $V_{G}$  curves exhibit large hysteresis in the forward and reverse sweeps. The hysteresis was observed in the  $C_{G, \text{sweep}}$ - $V_G$  curve for  $t_P = 0$  s as well as those for  $t_P = 10$ , 20, and 30 s. Thus, oxygen plasma treatment probably does not cause the hysteresis. We adopted guasi-pulse measurement to exclude the influence of the hysteresis.

The maximum and minimum values of  $C_G$  depend on the  $SiO_2$  thickness. Although the  $SiO_2$  layers were deposited under the same condition, unintentional difference in

conditions leads to the difference in the  $SiO_2$  thickness. For comparison of the C-V characteristics, we calculated a normalized capacitance  $C_n$  defined as

$$C_{\rm n}(V_{\rm G}) = \frac{C_{\rm G}(V_{\rm G}) - \min[C_{\rm G}(V_{\rm G})]}{\max[C_{\rm G}(V_{\rm G})] - \min[C_{\rm G}(V_{\rm G})]}.$$

(14)

In the calculation, average values near to the maximum and minimum of  $C_G(V_G)$  are adopted as values of functions  $\max[C_G(V_G)]$  and  $\min[C_G(V_G)]$ . As described in Sect. 3,  $\max[C_{G, \, \text{pulse}}(V_G)]$  was adopted as  $C_{\text{OX}}$ . Figure 5(e) shows  $C_{\text{n, pulse}}$  versus  $V_G$  of pentacene MOS capacitors for  $t_P = 0$ , 10, 20, and 30 s. The C-V curves shift to positive gate voltage with an increase in  $t_P$ .

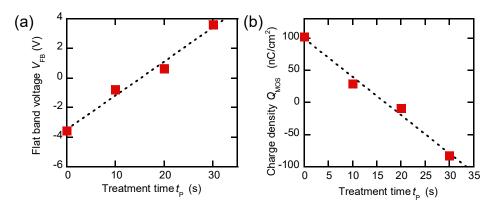

The  $V_{\rm FB}$  values were calculated based on Eq. (8). Figure 5(f) shows the  $C_S$  values calculated by substituting  $C_G$  values into Eq. (6). When  $V_G$  decrease to -20 V, accumulation of holes in the pentacene layer proceeds. Thus,  $C_S$  increases to infinity with a decrease in  $V_G$ . The increase in  $C_S$  shown in Fig. 5(f) is consistent with the explanation. On the other hand, the  $C_{\rm S}$  decreases with an increase in  $V_{\rm G}$ , and approaches 1.55, 1.58, 1.53, and 1.53 × 10<sup>-7</sup> F/cm<sup>2</sup> for  $t_P = 0$ , 10, 20, and 30 s, respectively. From Eq. (8), the  $V_{\rm FB}$  value, which equals  $V_{\rm G}$  that satisfies  $C_S = 3.06-3.16 \times 10^{-6} \text{ F/cm}^2$ , are estimated to be -3.57, -0.77, 0.64, 3.61 V for  $t_P = 0$ , 10, 20, and 30 s, respectively. The  $V_{\rm FB}$  values are summarized in Table 2 and Fig. S4(a). For each  $t_P$ , this value is close to the  $V_{TH}$  value shown in Table 1. The  $V_{\rm FB}$  as well as  $V_{\rm TH}$  can be used for estimation of Q,  $Q_0$ , and  $q_P$ . The calculated  $Q(Q_{MOS})$  is shown in Fig. S4(b).  $Q_0$  and  $q_P$  are estimated to be 98.7 nC/cm<sup>2</sup> and −5.92 nC cm<sup>-2</sup> s<sup>-1</sup>, which are not far from those estimated from

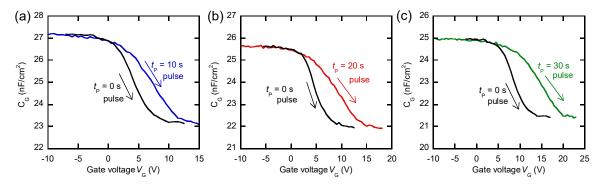

Figure 6.  $C_{G, pulse}$  versus  $V_G$  characteristics for calculation of  $D_M$  for  $t_P = (a) 10 s$ , (b) 20 s, and (c) 30 s.  $C_{G, pulse}$  for  $t_P = 0 s$  is shifted so that its  $V_{FB}$  equals  $V_{FB}$  of  $C_{G, pulse}$  for  $t_P = 10 s$ , 20 s, or 30 s and is adjusted as its maximum and minimum fit to those of  $C_{G, pulse}$  for  $t_P = 10 s$ , 20 s, or 30 s. The  $C_{G, pulse}$  for  $t_P = 0 s$  was used as  $C_{ref}$ .

Figure 7.  $C_{G, \text{ sweep}}$  versus  $V_{G}$  and  $C_{G, \text{ pulse}}$  versus  $V_{G}$  characteristics for calculation of  $D_{H}$  for  $t_{P} = (a) \ 10 \ s$ , (b) 20 s, and (c) 30 s. The  $C_{G, \text{ pulse}}$  was used as  $C_{ref.}$

$V_{\rm TH}$  because of small difference between  $V_{\rm FB}$  and  $V_{\rm TH}$ . Electrons that cause  $Q_{\rm S}$  (=  $q_{\rm P}$   $t_{\rm P}$ ) probably capture at interface states. We classify the interface state density into  $D_{\rm L}$ . This is because  $Q_{\rm S}$  does not cause hysteresis in the transfer characteristics of pentacene TFTs. This indicate that  $D_{\rm L}$  work as deep traps. Thus,  $D_{\rm L}$  corresponds to low energy levels as shown in Fig. 1.  $Q_{\rm S}$  is expressed as

$$Q_{\rm S} = q \int D_{\rm L} d\Psi \ . \tag{15}$$

as integral of  $D_{\rm L}$  with respective to potential  $\Psi$ . The area density  $|Q_{\rm S,\,MOS}/q|$  for  $D_{\rm L}$  is shown in Table 2.

An increase in  $V_{\rm G}$  leads to depletion of holes in the pentacene layer. Consequently, the minimum  $C_{\rm S}$  corresponds to the capacitance of pentacene serving as insulator. By assuming the thickness of pentacene, the relative dielectric constant of the pentacene layer can be calculated from the minimum  $C_{\rm S}$ . The thickness of 45 nm described in Sect. 3 is the thickness at the top of the pentacene. A pentacene generally has a dendritic structure. Thus, the average thickness is roughly assumed to be a half of 45 nm. Under this assumption, the relative dielectric constant is estimated to be 3.9. This value is almost the same as that reported by a group [55].

#### 4.3 Interface state density

For calculation of  $D_{\rm it}(\Psi_{\rm S})$ ,  $C_{\rm G, pulse}$  and  $C_{\rm G, sweep}$  measured in the forward shown in Fig. 3 were used. The calculation of  $D_{\rm it}(\Psi_{\rm S})$  from Eq. (10) requires  $C_{\rm ref}(V_{\rm G})$  and  $\Psi_{\rm ref}(V_{\rm G})$ . First,  $D_{\rm it}(\Psi_{\rm S})$  calculated from  $C_{\rm G, pulse}(V_{\rm G})$  for  $t_{\rm P}=10$ , 20, and 30 s are examined. For the calculation,  $C_{\rm G, pulse}(V_{\rm G})$  for  $t_{\rm P}=0$  s are used as  $C_{\rm ref}(V_{\rm G})$ . The  $D_{\rm it}(\Psi_{\rm S})$  is assigned as  $D_{\rm M}$ . Next,  $D_{\rm it}(\Psi_{\rm S})$  calculated from  $C_{\rm G, sweep}$  ( $V_{\rm G}$ ) for  $t_{\rm P}=10$ , 20, and 30 s are examined.  $C_{\rm G, pulse}(V_{\rm G})$  for  $t_{\rm P}=10$ , 20, and 30 s are used as  $C_{\rm ref}(V_{\rm G})$  for the calculation from  $C_{\rm G, sweep}$  ( $V_{\rm G}$ ) for  $t_{\rm P}=10$ , 20, and 30 s, respectively. The  $D_{\rm it}(\Psi_{\rm S})$  is assigned as  $D_{\rm H}$ . The justification of the assignment for  $D_{\rm M}$  and  $D_{\rm H}$  is discussed below. The  $\Psi_{\rm S}(V_{\rm G})$  calculated from  $C_{\rm G, pulse}$  and  $C_{\rm G, sweep}$  measured in the forward is shown in Fig. S5 of supplemental data.

Since a MOS capacitor of  $t_P = 0$  s has no interface state generated by oxygen plasma treatment, we chose  $C_{G, \, pulse}(V_G)$  of  $t_P = 0$  as  $C_{ref}(V_G)$ . However,  $C_{G, \, pulse}(V_G)$  of  $t_P = 10$ , 20, and 30 s involves the change in  $V_{FB}$  induced by the influence of  $D_L$ . To eliminate the influence, we shifted  $C_{G, \, pulse}(V_G)$  of  $t_P = 0$  by the difference in  $V_{FB}$  and used it as  $C_{ref}(V_G)$ . In addition, the maximum and minimum of  $C_{ref}(V_G)$  were adjusted to the maximum and minimum of  $C_G(V_G)$  of  $t_P = 10$ , 20, or 30 s, respectively. Figures 6(a)-6(c) shows  $C_G(V_G)$  and  $C_{ref}(V_G)$  curves for  $t_P = 10$ , 20, and 30 s. The  $C_G(V_G)$  of  $t_P > 0$  is larger than  $C_G(V_G)$  of  $t_P = 0$ . The difference in  $C_G(V_G)$  corresponds to electrons trapped at interface states for  $D_M$ .

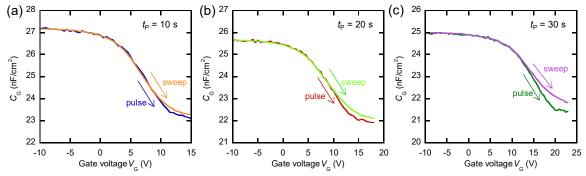

**Figure 8.** Interface state densities  $D_{\rm M}$  and  $D_{\rm H}$  for  $t_{\rm P}=10~{\rm s}$ , 20 s, and 30 s. (b) Interface state densities calculated as  $(D_{\rm M}+D_{\rm H})$ .

For quasi-static voltage of the normal sweep, the bias stress at each  $V_G$  for about 60 s leads to electrons trapped at interface states locating at high energy levels. Figure 7 shows  $C_G$ ,  $P_{pulse}(V_G)$  and  $C_{G, sweep}(V_G)$  versus  $V_G$ . For  $t_P = 10$ , 20, and 30, the difference in  $C_{G, pulse}(V_G)$  and  $C_{G, sweep}(V_G)$  increase at  $V_G > 10$ . The difference in  $C_G(V_G)$  corresponds to electrons trapped at interface states for  $D_H$ . The  $C_{G, pulse}(V_G)$  adopted as  $C_{ref}(V_G)$  involves the influence of  $D_M$ . It is expected that  $D_H$  is distributed at high energy levels.

Figure 8(a) shows  $D_{\rm M}$  and  $D_{\rm H}$  calculated form  $C_{\rm G}(V_{\rm G})$  and  $C_{\text{ref}}(V_{\text{G}})$  explained above. Indeed,  $D_{\text{M}}$  locates near  $q\Psi_{\text{S}}=0$  as shown in Fig. 1 and gradually decreases with an increase in  $\Psi_{\rm S}$ . The  $D_{\rm M}$  are distributed in the range of  $q\Psi_{\rm S}=0.0-0.6$  eV. For example, the  $D_{\rm M}$  values at  $q\Psi_{\rm S}=0.2$  eV are  $7.6\times10^{11}, 9.3$  $\times 10^{11}$ , and 1.3  $\times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> for  $t_P = 10$ , 20, and 30 s, respectively. These values increase with plasma treatment time. For  $q\Psi_{\rm S} > 0.8$  eV,  $D_{\rm M}$  is less than  $D_{\rm H}$ . On the other hand,  $D_{\rm H}$  obtained by a normal sweep is distributed at high energy as compared with  $D_{\rm M}$  obtained by a quasi-pulse wave. The result is also expected from Fig. 7. The  $D_{\rm H}$  is broadly distributed in the range of  $q\Psi_S = 0.4 - 1.3$  eV, and is in the range of  $4 \times 10^{10}$  to  $2 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>. For  $q\Psi_S = 0.6 - 1.0$  eV, the  $D_{\rm H}$  is about 5.6 × 10<sup>10</sup>, 9.7 × 10<sup>10</sup>, and 1.8 × 10<sup>11</sup>cm<sup>-2</sup> eV<sup>-1</sup> on average for  $t_P = 10$ , 20, and 30, respectively. In the method of this study,  $D_{\rm M}$  and  $D_{\rm H}$  can be interpreted as density of states

which trap electrons at each  $\Psi_{\rm S}$  for  $t_{\rm M}$ . Since  $t_{\rm M}=0.1$  s for  $D_{\rm M}$  and  $t_{\rm M}=60$  s for  $D_{\rm H}$ ,  $D_{\rm H}$  represents states that take a long time to trap as compared to  $D_{\rm M}$ . Thus, Fig. 8(a) suggests that the trapping at  $q\Psi_{\rm S}>0.7$  eV takes longer time than that at  $q\Psi_{\rm S}<0.7$  eV.

Figure 8(b) shows interface state densities calculated as  $(D_{\rm M} + D_{\rm H})$ . The total distribution of the interface state can be seen from Fig. 8(b). The  $(D_{\rm M} + D_{\rm H})$  monotonically decreases on average with an increase in  $q\Psi_{\rm S}$ . The values of  $(D_{\rm M} + D_{\rm H})$ are comparable to those of MOS capacitors having crystal Si [35], amorphous Si [36], SiC [56], GaN [57], and polymers [58,59] as a semiconductor. When integrating  $(D_{\rm M} + D_{\rm H})$  with respect to  $q\Psi_{\rm S}$ , the area densities are obtained as 4.9, 6.2, and  $9.7 \times 10^{11} \,\mathrm{cm^{-2}}$  for  $t_P = 10, 20, \text{ and } 30 \,\mathrm{s}$ , respectively. The area density is close to  $Q_{S,MOS}/q$  relating to  $D_L$  shown in Table 2. The increase of  $(D_{\rm M} + D_{\rm H})$  with  $t_{\rm P}$  is similar to the increases in  $Q_{S,MOS}/q$ . We predict that the origin of the trap is excess oxygen atoms, such as  $\equiv Si-O-O-Si\equiv$ ,  $\equiv Si-O-O\cdot$ , and  $\equiv Si-O\cdot$ , generated by oxygen plasm treatment [24,60]. Here, "=" and "-" denote three and one network between O and Si, respectively, and "." represents an unpaired electron. The increase in  $t_P$  leads to the increase of the excess oxygen atoms in SiO<sub>2</sub>. The explanation is consistent with the increases of  $(D_{\rm M} + D_{\rm H})$  and  $Q_{\rm S,MOS}/q$ . The energy levels of point defects for  $\equiv$ Si-O-O-Si $\equiv$ ,  $\equiv$ Si-O-O $\cdot$ , and  $\equiv$ Si-O $\cdot$  are placed between the valence band edge of perfect SiO2 and the energy level of the highest occupied molecular orbital of pentacene [24]. Probably, total distribution of  $(D_L + D_M + D_H)$  exhibits the maximum at an energy level close to those of the point defect. Generally, the energy level of point defects in amorphous material has distribution. Thus, the decrease in Fig. 8 may exhibit tail of the distribution of  $(D_L + D_M + D_H)$ .

Probably, the interface states for  $D_{\rm M}$  and  $D_{\rm H}$  do not largely influence on the characteristics of TFTs when TFTs operates at  $V_{\rm G} < 0$ . Conversely, positive  $V_{\rm G}$  may temporarily lead to threshold voltage shift by electrons trapped at the interface states for  $D_{\rm M}$  and  $D_{\rm H}$ . The finding in this study is useful for operational stability in organic TFTs. The interface states at high energy level such as  $D_{\rm M}$  and  $D_{\rm H}$  may be used for applications that intentionally require temporary characteristic changes.

#### 5. Conclusion

We measured C-V characteristics of pentacene MOS capacitors with a SiO<sub>2</sub> dielectric treated by oxygen plasma to extract the energy distribution of the interface states. For the pentacene MOS capacitors, the  $V_{\rm FB}$  determined by the definition in this study were close to those of threshold voltages estimated from transfer curves of pentacene TFTs. The  $V_{\rm FB}$  values increased with an increase in plasma treatment time. First, the C-V characteristics of MOS capacitors without oxygen plasma treatment was used as a reference for extraction of energy distribution. The interface states

extracted from the C-V characteristics measured by applying a quasi-pulse wave voltage were distributed in the range of  $\Psi_{\rm S}$  = 0.0 – 0.6 eV. The interface state density has the maximum of about  $4\times10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> and gradually decreases with an increase in  $\Psi_{\rm S}$ . Next, the C-V characteristics for a quasi-pulse wave voltage was used as a reference. The interface states extracted from the C-V characteristics measured by applying a normal sweep voltage were broadly distributed in the range of  $\Psi_{\rm S}=0.4-1.3$  eV. The interface density is in the range of  $4\times10^{10}$  to  $2\times10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>. The information of the energy distribution contributes to development of inorganic FET with oxide gate dielectric as well organic TFTs.

#### Acknowledgements

This work was supported by JSPS KAKENHI Grant Number 19H02171 and 19K15048.

#### **ORCID iDs**

Yoshiaki Hattori https://orcid.org/0000-0002-5400-8820 Masatoshi Kitamura https://orcid.org/0000-0003-1342-4796

#### References

- [1] Dimitrakopoulos C D and Malenfant P R L 2002 Organic thin film transistors for large area electronics *Adv. Mater.* **14** 99

- [2] Coropceanu V, Cornil J, Filho D A da S, Olivier Y, Silbey R, Brédas J-L 2007 Charge transport in organic semiconductors Chem. Rev. 107 926

- [3] Taylor D M 2016 Progress in organic integrated circuit manufacture Jpn. J. Appl. Phys. 55 02BA01

- [4] Zschieschang U and Klauk H 2019 Organic transistors on paper: a brief review J. Mater. Chem. C 7 5522

- [5] Kang M J, Doi I, Mori H, Miyazaki E, Takimiya K, Ikeda M and Kuwabara H 2011 Alkylated dinaphtho[2,3- b:2',3'-f]thieno[3,2-b]thiophenes(C<sub>n</sub>-DNTTs): Organic semiconductors for high-performance thin-film transistors Adv. Mater. 23 1222

- [6] Nakayama K, Hirose Y, Soeda J, Yoshizumi M, Uemura T, Uno M, Li W, Kang M J, Yamagishi M, Okada Y, Miyazaki E, Nakazawa Y, Nakao A, Takimiya K and Takeya J 2011 Patternable solution-crystallized organic transistors with high charge carrier mobility Adv. Mater. 23 1626

- [7] Minemawari H, Yamada T, Matsui H, Tsutsumi J, Haas S, Chiba R, Kumai R and Hasegawa T 2011 Inkjet printing of single-crystal films *Nature* 475 364

- [8] He K, Li W, Tian H, Zhang J, Yan D, Geng Y and Wang F 2017 Asymmetric conjugated molecules based on [1]Benzothieno[3,2-b][1]benzothiophene for high-mobility organic thin-film transistors: Influence of alkyl chain length ACS Appl. Mater. Interfaces 9 35427

- [9] Haas S, Takahashi Y, Takimiya K and Hasegawa T 2009 Highperformance dinaphtho-thieno-thiophene single crystal fieldeffect transistors Appl. Phys. Lett. 95 022111

- [10] Kobayashi S, Nishikawa T, Takenobu T, Mori S, Shimoda T, Mitani T, Shimotani H, Yoshimoto N, Ogawa S and Iwasa Y

- 2004 Control of carrier density by self-assembled monolayers in organic field-effect transistors *Nature Mater.* **3** 317

- [11] Pernstich K P, Haas S, Oberhoff D, Goldmann C, Gundlach D J, Batlogg B, Rashid A N and Schitter G 2004 Threshold voltage shift in organic field effect transistors by dipole monolayers on the gate insulator J. Appl. Phys. 96 6431

- [12] Salinas M, Jäger C M, Amin A Y, Dral P O, Meyer-Friedrichsen T, Hirsch A, Clark T and Halik M 2012 The relationship between threshold voltage and dipolar character of self-assembled monolayers in organic thin-film transistors *J. Am. Chem. Soc.* 134 12648

- [13] Hirata I, Zschieschang U, Yokota T, Kuribara K, Kaltenbrunner M, Klauk H, Sekitani T and Someya T 2015 High-resolution spatial control of the threshold voltage of organic transistors by microcontact printing of alkyl and fluoroalkylphosphonic acid self-assembled monolayers *Org. Electron.* 26 239

- [14] Dao T T, Matsushima T, Friedlein R and Murata H 2013 Controllable threshold voltage of a pentacene field-effect transistor based on a double-dielectric structure *Org. Electron*. 14 2007

- [15] Wu W-J, Lee C-H, Hsu C-H, Yang S-H and Lin C-T 2013 Adjustable threshold-voltage in all-inkjet-printed organic thin film transistor using double-layer dielectric structures *Thin* Solid Films 548 576

- [16] Pak K, Seong H, Choi J, Hwang W S, and Im S G 2016 Synthesis of ultrathin, homogeneous copolymer dielectrics to control the threshold voltage of organic thin-film transistors Adv. Funct. Mater. 26 6574

- [17] Abe Y, Hasegawa T, Takahashi Y, Yamada T and Tokura Y 2005 Control of threshold voltage in pentacene thin-film transistors using carrier doping at the charge-transfer interface with organic acceptors Appl. Phys. Lett. 87 153506

- [18] Belasco J, Mohapatra S K, Zhang Y, Barlow S, Marder S R and Kahn A 2014 Molecular doping and tuning threshold voltage in 6,13-bis(triisopropylsilylethynyl)pentacene/polymer blend transistors *Appl. Phys. Lett.* **105** 063301

- [19] Nie G, Dong B, Wu S, Zhan S, Xu Y, Sheng W, Liu Y and Wu X 2019 Mechanistic analysis of embedded copper oxide in organic thin-film transistors with controllable threshold voltage ACS Omega 4 8506

- [20] Chung Y, Johnson O, Deal M, Nishi Y, Murmann B and Bao Z 2012 Engineering the metal gate electrode for controlling the threshold voltage of organic transistors *Appl. Phys. Lett.* 101 063304

- [21] Moon H, Im D and Yoo S, 2013 Controlling the threshold voltage of organic thin-film transistors by transition metal oxides *IEEE Electron Device Lett.* **34** 1014

- [22] Shiwaku R, Yoshimura Y, Takeda Y, Fukuda K, Kumaki D and Tokito S 2015 Control of threshold voltage in organic thinfilm transistors by modifying gate electrode surface with MoO<sub>X</sub> aqueous solution and inverter circuit applications *Appl. Phys. Lett.* 106 053301

- [23] Schroeder R, Majewski L A and Grell M. 2003 A study of the threshold voltage in pentacene organic field-effect transistors *Appl. Phys. Lett.* 83 3201

- [24] Kitamura M, Kuzumoto Y, Aomori S, Kamura M, Na J H and Arakawa Y 2009 Threshold voltage control of bottom-contact

- n-channel organic thin-film transistors using modified drain/source electrodes *Appl. Phys. Lett.* **94** 083310

- [25] Iba S, Sekitani T, Kato Y, Someya T, Kawaguchi H, Takamiya M, Sakurai T and Takagi S 2005 Control of threshold voltage of organic field-effect transistors with double-gate structures Appl. Phys. Lett. 87 023509

- [26] Lee S, Yokota T and Someya T 2017 Threshold voltage control for organic thin-film transistors using a tri-gate structure with capacitive coupling *Jpn. J. Appl. Phys.* **56** 04CL01

- [27] Wang A, Kymissis I, Bulović V and Akinwande A I 2006 Engineering density of semiconductor-dielectric interface states to modulate threshold voltage in OFETs IEEE Trans. Electron Devices 53 9

- [28] Fukuda K, Sekitani T, Zschieschang U, Klauk H, Kuribara K, Yokota T, Sugino T, Asaka K, Ikeda M, Kuwabara H, Yamamoto T, Takimiya K, Fukushima T, Aida T, Takamiya M, Sakurai T and Someya T 2011 A 4 V operation, flexible braille display using organic transistors, carbon nanotube actuators, and organic static random-access memory Adv. Funct. Mater. 21 4019

- [29] Kimura Y, Kitamura M, Kitani A and Arakawa Y 2016 Operational stability in pentacene thin-film transistors with threshold voltages tuned by oxygen plasma treatment *Jpn. J. Appl. Phys.* 55 02BB14

- [30] Kitani A, Kimura Y, Kitamura M and Arakawa Y 2016 Threshold voltage control in dinaphthothienothiophene-based organic transistors by plasma treatment: Toward their application to logic circuits *Jpn. J. Appl. Phys.* 55 03DC03

- [31] Halik M, Klauk H, Zschieschang U, Schmid G, Dehm C, Schütz M, Maisch S, Effenberger F, Brunnbauer M and Stellacci F 2004 Low-voltage organic transistors with an amorphous molecular gate dielectric *Nature* **431** 963

- [32] Zen A, Neher D, Silmy K, Holländer A, Asawapirom U, and Scherf U 2005 Improving the performance of organic field effect transistor by optimizing the gate insulator surface *Jpn. J. Appl. Phys.* **44** 3721

- [33] Takahashi H, Hanafusa Y, Kimura Y and Kitamura M 2018 Application of pentacene thin-film transistors with controlled threshold voltages to enhancement/depletion inverters *Jpn. J. Appl. Phys.* 57 03EH03

- [34] Takahashi H, Kitamura M, Hattori Y and Kimura Y 2019 A ring oscillator consisting of pentacene thin-film transistors with controlled threshold voltages *Jpn. J. Appl. Phys.* **58** SBBJ04

- [35] Lenahan P M and Conley J F1998 What can electron paramagnetic resonance tell us about the Si/SiO<sub>2</sub> system *J. Vac. Sci. Technol. B* **16** 2134

- [36] Powell M J, van Berkel C, Franklin A R, Deane S C and Milne W I 1992 Defect pool in amorphous-silicon thin-film transistors *Phys. Rev. B* 45 4160

- [37] Reed M L and Plimmer J D 1988 Chemistry of Si-SiO<sub>2</sub> interface trap annealing *J. Appl. Phys.* **63** 5776

- [38] Witczak S C, Suehle J S and Gaitan M 1992 An experimental comparison of measurement techniques to extract Si-SiO<sub>2</sub> interface trap density *Solid State Electron*. **35** 345

- [39] Yang Y S, Kim S H, Lee J-I Chu H Y, Do L-M, Lee H, Oh J, Zyung T, Ryu M K and Jang M S 2002 Deep-level defect characteristics in pentacene organic thin films *Appl. Phys. Lett.* 80 1595

- [40] Jang J, Kim J, Bae M, Lee J, Kim D M, Kim D H, Lee J, Lee B-L. Koo B and Jin Y W 2012 Extraction of the sub-bandgap density-of-states in polymer thin-film transistors with the multi-frequency capacitance-voltage spectroscopy *Appl. Phys. Lett.* 100 133506

- [41] Liu Y, Lai P T, Yao R and Deng L 2012 Interface states in polymer thin-film transistors based on poly(3-hexylthiophene) Semicond. Sci. Technol. 27 055015

- [42] Yun M, Gangopadhyay S, Bai M, Taub H, Arif M and Guha S 2007 Interface states in polyfluorene-based metal-insulatorsemiconductor devices Org. Electron. 8 591

- [43] Kimura Y, Hattori Y and Kitamura M 2020 Evaluation of organic metal-oxide-semiconductor capacitors based on a distributed constant circuit *Jpn. J. Appl. Phys.* **59** 036503

- [44] Schroder D K 2006 Semiconductor Material and Device Characterization, 3rd ed. (New York, USA, Wiley) ch 6 pp.350-352

- [45] Terman L M 1962 An investigation of surface states at a silicon/silicon oxide interface employing metal-oxide-silicon dioes Solid-State Electronics 5 285

- [46] Zeng K, Jia Y and Singisetti U 2016 Interface state density in atomic layer deposited SiO<sub>2</sub>/β-Ga<sub>2</sub>O<sub>3</sub> (200) MOSCAPs *IEEE Electron Device Lett.* 37 906

- [47] Novkovski N 2015 Determination of interface states in metal(Ag,TiN,W)–Hf: Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>x</sub>N<sub>y</sub>–Si structures by different compact methods *Materials Science in Semiconductor Processing* **39** 308

- [48] Kitamura M and Arakawa Y 2008 Pentacene-based organic field-effect transistors J. Phys.: Condens. Matter 20 184011

- [49] Kuhn M 1970 A quasi-static technique for MOS C-V and surface state measurements Solid-State Electronics 13 873

- [50] Wilde M, Beauport I, Stuhl F, Al-Shamery K and Freund H.-J. 1999 Adsorption of potassium on Cr<sub>2</sub>O<sub>3</sub>(0001) at ionic and metallic coverages and uv-laser-induced desorption *Phys. Rev.* B 59 13401

- [51] Koch N, Kahn A, Ghijsen J, Pireaux J-J, Schwartz J, Johnson R L and Elschner A 2003 Conjugated organic molecules on metal versus polymer electrodes: Demonstration of a key energy level alignment mechanism *Appl. Phys. Lett.* 82 70

- [52] Kim W-K and Lee J-L 2007 In situ analysis of hole injection barrier of O<sub>2</sub> plasma-treated Au with pentacene using photoemission spectroscopy *Electrochem. Solid-State Lett.* 10 H104

- [53] Yun D-J, Chung J G, Jung C H, Han H-S, Lee J C, Anass B, Lee S, Kyung Y and Park S-H 2013 Pentacene orientation on source/drain electrodes and its effect on charge carrier transport at pentacene/electrode interface, investigated using in situ ultraviolet photoemission spectroscopy and device characteristics J. Electrochem. Soc. 160 H436

- [54] Liu X, Wang C, Wang C, Irfan I, and Gao Y 2015 Interfacial electronic structures of buffer-modified pentacene/C<sub>60</sub>-based charge generation layer *Org. Electron.* 17 325

- [55] Schwenn P E, Burn P L and Powell B J 2011 Calculation of solid state molecular ionisation energies and electron affinities for organic semiconductors *Org Electron*. 12 394

- [56] Cooper JR J A 1997 Advances in SiC MOS technology *Phys. Stat. Sol. A* 162 305

- [57] Ren B, Sumiya M, Liao M, Koide Y, Liu X, Shen Y and Sang L 2018 Interface trap characterization of Al<sub>2</sub>O<sub>3</sub>/GaN vertical-

- type MOS capacitors on GaN substrate with surface treatments *J. Alloys Compouds* **767** 600

- [58] Hatta H, Miyagawa Y, Nagase T, Kobayashi T, Hamada T, Murakami S, Matsukawa K and Naito H 2018 Determination of interface-state distributions in polymer-based metalinsulator-semiconductor capacitors by impedance spectroscopy *Appl. Sci.* 8 1493

- [59] Yun M, Ravindran R, Hossain H, Gangopadhyay S, Scherf U, Bunnagel T, Galbrecht, Arif M and Guha S 2006 Capacitancevoltage characterization of polyfluorene-based metal-insulatorsemiconductor diodes Appl. Phys. Lett. 89 013506

- [60] Pacchioni G and Ierano G 1998 *Ab initio* theory of optical transitions of point defects in SiO<sub>2</sub> *Phys. Rev. B* **57** 818.

# Energy distribution of interface states generated by oxygen plasma treatment for control of threshold voltage in pentacene thin-film transistors

Yoshinari Kimura\*, Yoshiaki Hattori, and Masatoshi Kitamura\*\*

Department of Electrical and Electronic Engineering, Graduate School of Engineering, Kobe University, Kobe 657-8501, Japan

\*E-mail address: kimura@eedept.kobe-u.ac.jp

# Supplementary data

## 1. Derivation of the equation for Terman method

In this section, Eq. (13) used for Terman method is derived from Eq. (10):

$$D_{\rm it}(\Psi_{\rm S}(V_{\rm G})) = \lim_{\Delta V_{\rm G} \to 0} \frac{1}{q^2} \frac{\Delta Q_{\rm G} - \Delta Q_{\rm ref}}{\Psi_{\rm S}(V_{\rm G} + \Delta V_{\rm G}) - \Psi_{\rm S}(V_{\rm G})}.$$

(10)

By substituting Eq. (9) into Eq. (11a), we obtain

$$\begin{split} \Delta Q_{\rm G} &= \int_{V_{\rm G}}^{V_{\rm G} + \Delta V_{\rm G}} C_{\rm G}(V) dV \\ &= \left[ -C_{\rm OX} \Psi_{\rm S}(V_{\rm G} + \Delta V_{\rm G}) + C_{\rm OX} \left( V_{\rm G} + \Delta V_{\rm G} - V_{\rm FB} \right) \right] - \left[ -C_{\rm OX} \Psi_{\rm S}(V_{\rm G}) + C_{\rm OX} \left( V_{\rm G} - V_{\rm FB} \right) \right] \\ &= -C_{\rm OX} \left[ \Psi_{\rm S}(V_{\rm G} + \Delta V_{\rm G}) - \Psi_{\rm S}(V_{\rm G}) \right] + C_{\rm OX} \Delta V_{\rm G} \end{split} \tag{S1}$$

Surface potential  $\Psi_{ref}(V_G)$  is expressed as

$$\Psi_{\text{ref}}(V_{\text{G}}) = V_{\text{G}} - V_{\text{FB}}' - \int_{V_{\text{FB}}}^{V_{\text{G}}} \left( \frac{C_{\text{ref}}(V)}{C_{\text{OX}}} \right) dV$$

(S2)

where  $V_{\rm FB}$  is flat band voltage determined from  $C_{\rm ref}(V_{\rm G})$ . By substituting Eq. (S2) into Eq. (11b), we have

$$\begin{split} \Delta Q_{\text{ref}} &= \int_{V_{\text{G}}'}^{V_{\text{G}}' + \Delta V_{\text{G}}'} C_{\text{ref}}(V) dV \\ &= \left[ -C_{\text{OX}} \Psi_{\text{ref}}(V_{\text{G}}' + \Delta V_{\text{G}}') + C_{\text{OX}} \left( V_{\text{G}}' + \Delta V_{\text{G}}' - V_{\text{FB}}' \right) \right] - \left[ -C_{\text{OX}} \Psi_{\text{ref}}(V_{\text{G}}') + C_{\text{OX}} \left( V_{\text{G}}' - V_{\text{FB}}' \right) \right] \\ &= -C_{\text{OX}} \left[ \Psi_{\text{ref}}(V_{\text{G}}' + \Delta V_{\text{G}}') - \Psi_{\text{S}}(V_{\text{G}}') \right] + C_{\text{OX}} \Delta V_{\text{G}}' \end{split} \tag{S3}$$

as well as Eq. (S1). Using (S1) and (S3), we get

$$\Delta Q_{\rm G} - \Delta Q_{\rm ref} = \left\{ -C_{\rm OX} \left[ \Psi_{\rm S} (V_{\rm G} + \Delta V_{\rm G}) - \Psi_{\rm S} (V_{\rm G}) \right] + C_{\rm OX} \Delta V_{\rm G} \right\}

- \left\{ -C_{\rm OX} \left[ \Psi_{\rm ref} (V_{\rm G}' + \Delta V_{\rm G}') - \Psi_{\rm S} (V_{\rm G}') \right] + C_{\rm OX} \Delta V_{\rm G}' \right\}.$$

$$= C_{\rm OX} \left( \Delta V_{\rm G} - \Delta V_{\rm G}' \right) \tag{S4}$$

Here, we use Eqs. (12a) and (12b). By substituting (S4) into Eq. (10), Eq. (13) is obtained as following:

$$D_{it}(\Psi_{S}(V_{G})) = \lim_{\Delta V_{G} \to 0} \frac{1}{q^{2}} \frac{\Delta Q_{G} - \Delta Q_{ref}}{\Psi_{S}(V_{G} + \Delta V_{G}) - \Psi_{S}(V_{G})}$$

$$= \lim_{\Delta V_{G} \to 0} \frac{1}{q^{2}} \frac{C_{OX}(\Delta V_{G} - \Delta V_{G}')}{\Psi_{S}(V_{G} + \Delta V_{G}) - \Psi_{S}(V_{G})} .$$

$$= \frac{C_{OX}}{q^{2}} \frac{d(V_{G} - V_{G}')}{d\Psi_{S}} .$$

(S5)

Thus,  $V_G$  and  $V_{G'}$  satisfy the relationship Eq. (12a). In other word,  $V_{G'}$  is calculated from Eq. (12a) when a value of  $V_G$  is decided.

<sup>\*\*</sup>E-mail address: kitamura@eedept.kobe-u.ac.jp

# 2. Pentacene TFT characteristics

**Figure S1.** Output characteristics of typical pentacene TFTs with  $L = 120 \mu m$  for  $t_P = (a) 0 s$ , (b) 10 s, (c) 20 s, and (d) 30 s.

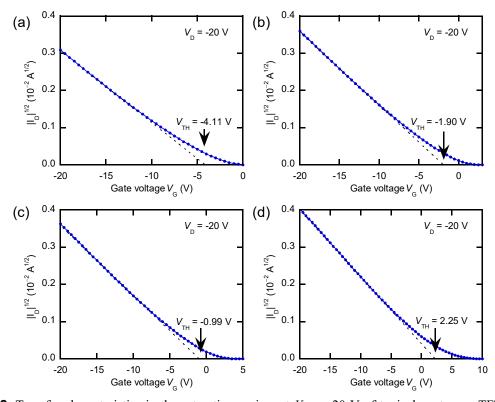

Figure S2. Transfer characteristics in the saturation regime at  $V_D = -20$  V of typical pentacene TFTs with  $L = 120 \mu m$  for  $t_P = (a) 0 s$ , (b) 10 s, (c) 20 s, and (d) 30 s. The fitting lines for estimation of field-effect mobilities and threshold voltage are shown in these figures with estimated  $V_{TH}$  values.

# 3. Pentacene MOS capacitor characteristics

**Figure S3.**  $C_{G, pulse}$  versus  $V_{G}$  and  $C_{G, sweep}$  versus  $V_{G}$  characteristics for pentacene MOS capacitors for  $t_{P} = (a) \ 0 \ s$ , (b)  $10 \ s$ , (c)  $20 \ s$ , and (d)  $30 \ s$ .

**Figure S4.** (a)  $V_{FB}$  versus  $t_P$  determined from  $C_S$  shown in Fig. 5(f). (b)  $Q_{MOS}$  versus  $t_P$  calculated from Eq. (7) and  $V_{FB}$  values shown in (a).

**Figure S5.** Surface potential  $\Psi_S$  calculated from Eq. (9),  $C_{G, pulse}$ , and  $C_{G, sweep}$  shown in Fig. 7 for  $t_P = (a) \ 0 \ s$ , (b)  $10 \ s$ , (c)  $20 \ s$ , and (d)  $30 \ s$ .

**Figure S6.** C-V<sub>G</sub> characteristics for capacitance (C<sub>0</sub>) including the Au/SiO<sub>2</sub>/Cr area for t<sub>P</sub> = (a) 0 s and (b) 30 s, which were measured at normal sweep that f = 10, 100, and 1000 Hz and t<sub>M</sub> =0.8, 0.2, and 0.1 s, respectively.

**Figure S7.** *C-f* characteristics for capacitance ( $C_0$ ) including the Au/SiO<sub>2</sub>/Cr area for  $t_P$  = (a) 0 s and (b) 30 s, which were measured at  $V_G$  = 0 and 15 V, respectively.