PDF issue: 2025-12-05

# An interface trap charge model for simulation of graphene-based synaptic field effect transistors

Oshio, Reon Souma, Satofumi

(Citation)

Journal of Applied Physics, 131(2):024301

(Issue Date) 2022-01-14

(Resource Type) journal article

(Version)

Version of Record

(Rights)

This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. This article appeared in Journal of Applied Physics 131, 024301 (2022) and may be found at at https://doi.org/10.1063/5.0059066

(URL)

https://hdl.handle.net/20.500.14094/90008995

# Journal of Applied Physics

# An interface trap charge model for simulation of graphene-based synaptic field effect transistors

Cite as: J. Appl. Phys. **131**, 024301 (2022); https://doi.org/10.1063/5.0059066 Submitted: 05 June 2021 • Accepted: 16 December 2021 • Published Online: 10 January 2022

Reon Oshio and D Satofumi Souma

Journal of Applied Physics

SPECIAL TOPIC: Shock Behavior of Materials

# An interface trap charge model for simulation of graphene-based synaptic field effect transistors

Cite as: J. Appl. Phys. 131, 024301 (2022); doi: 10.1063/5.0059066

Submitted: 5 June 2021 · Accepted: 16 December 2021 ·

Published Online: 10 January 2022

Reon Oshio and Satofumi Souma 1000

#### **AFFILIATIONS**

Department of Electrical and Electronic Engineering, Kobe University, 1-1 Rokkodai, Nada, Kobe 657-8501, Japan

a)Author to whom correspondence should be addressed: ssouma@harbor.kobe-u.ac.jp

#### **ABSTRACT**

We propose a compact computational method based on the capacitance model for the efficient design of graphene-based synaptic field effect transistors (FETs), in which the hysteresis of conduction characteristics due to the channel-gate interface trap is used as synaptic plasticity. Using our method to calculate the conduction properties of graphene and armchair graphene nanoribbon (AGNR) superlattice FETs, it is shown that the AGNR can achieve an efficient conductance change rate  $\Delta w$ , which is approximately 7.4 times that of graphene. It was also found that  $\Delta w$  was the greatest when the gate oxide thickness was around 2-3 nm, which is near the limit of miniaturization. These results suggest that the proposed synaptic FETs are a promising approach to realize large scale integration chips for biological timescale computation.

Published under an exclusive license by AIP Publishing. https://doi.org/10.1063/5.0059066

#### I. INTRODUCTION

With the advent of the big data era and the demand for real-time edge computing, the development of high speed and low power consumption electronic devices is becoming more important. Neuromorphic computing has attracted great attention as one of the promising directions in realizing low power signal processing by means of electronic circuit mimicking of biological nervous systems that are highly energy efficient.<sup>1-4</sup> It also has the potential to contribute to the development of medicine and neuroscience through mutual computation with the biological nervous system.5,

Generally, a neuromorphic processor has two main components. The first one is the synapse, which is memory that stores binding weights with biologically relevant analog values. The second is the neuron, which generates spike outputs in response to spike inputs via the synapse. In recent years, synaptic devices using memristors, two-terminal devices whose resistance changes according to the current flowing through themselves via the phase change mechanisms, such as the formation of conductive filaments, have attracted attention and are expected to be applied to large scale integrated neuromorphic systems because of their ultrahigh speed drive, ultralow power consumption, and high scalability.73 However, resistive two-terminal devices have difficulty in simultaneously transmitting synaptic signals and learning unlike natural synapses. Such difficulties can be overcome by using three terminal

synaptic devices based on FETs, which have been shown to enable simultaneous synaptic signal transmission and learning with good stability and controllable device characteristics and have attracted attention as a new approach to replace two-terminal synaptic devices.9-11

As materials in FET fabrication, two-dimensional atomic film materials, such as graphene, have been attracting attention as nextgeneration materials due to their unique physical characteristics, such as high electron mobility and wider control of electronic transport properties by changing their widths. 12-14 For neuromorphic applications, high-performance synaptic devices can be realized by exploiting their sensitivity to the surrounding environment, such as charge trapping at the surface, which results in the hysteresis of conduction properties and makes it possible to realize synaptic functionality as experimentally reported in Refs. 15-17. From this viewpoint, twodimensional atomic film materials are highly advantageous since the conducting channel is directly contacted to its surrounding environment, that is, insulating materials, such as SiO<sub>2</sub>.

Despite recent experimental progress, an efficient and reliable computational methodology to study the synaptic behavior of graphene FET quantitatively has not been explored enough thus far except for a few simulation and modeling studies, 18-23 where the interface trap charge and the channel charge are treated in a separate way. Further detailed analysis of synaptic FETs for various

materials requires a unified general framework to treat the interface trap charge and the channel charge on equal footing. Moreover, it has not been studied enough so far how the controllable device parameters of graphene FET, such as the oxide thickness and the width of graphene in the form of the graphene nanoribbon (GNR), influence the device performance from the viewpoint of the synaptic functionality. With this motivation in mind, we propose a compact computational method to clarify the performance of graphene and GNR FETs as synaptic devices, in which the hysteresis of conduction characteristics due to the channel–gate interface trap is used as synaptic plasticity.

The remainder of the paper is organized as follows: Section II describes the method used to calculate the band structure and electrical conduction properties of the channel material and the model used to simulate the hysteresis of the conduction properties due to the interface trapping charge. Section III presents the results of the calculations, and Sec. IV discusses the results and summarizes the paper.

#### II. THEORETICAL FORMALISM

#### A. Tight-binding (TB) formalism

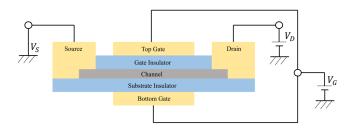

Figure 1 shows a schematic of the device structure considered in this study, where the channel property is described using the tight-binding (TB) method. In the TB formalism, the electronic properties of graphene and the GNR channel can be obtained by solving the eigenvalue problem  $H(\mathbf{k})|\psi_l(\mathbf{k})\rangle = E_l(\mathbf{k})|\psi_l(\mathbf{k})\rangle$ , where  $H(\mathbf{k})$  is the wavenumber  $\mathbf{k}$  dependent Bloch Hamiltonian of graphene or GNR spanned by the  $p_z$  orbitals within the unit cell and  $E_l(\mathbf{k})$  describes the lth energy band.

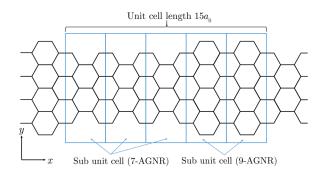

Regarding GNR, we focus our attention to armchair GNR (AGNR) because of its semiconducting property with the finite bandgap that depends on the width of the AGNR. In particular, we consider the AGNR superlattices, in which the number of atoms in the width direction of AGNR is periodically varied. In the present study, we examine the superlattice of 7-AGNR and 9-AGNR illustrated in Fig. 2, where it has been theoretically shown that the occurrence of a zero-dimensional topological interface state at the interface between the topologically non-trivial region and another topologically non-trivial region generates a new band near the Fermi

**FIG. 1.** Model diagram of the field effect transistors (FETs) assumed in this study. Double gating improves the gate voltage effect and doubles the interface area. In addition, it is thought to be able to prevent disturbances from factors other than the channel–oxide film interface.

**FIG. 2.** Unit cell of the armchair graphene nanoribbon (AGNR) superlattice, which we call 7(3)/9(2)-AGNR from the number of sub-unit cells in the 7-AGNR (3) and 9-AGNR (2) regions, respectively.

surface,<sup>24,25</sup> resulting in the narrowing of the bandgap depending on the lengths of the 7-AGNR and 9-AGNR regions.

### B. Current calculation method under ballistic conditions

Once the band structure  $E_l(\mathbf{k})$  and the wave function  $|\psi_l(\mathbf{k})\rangle$  are calculated, the current density of a channel with ideal electrodes at both ends can be calculated as

$$I = \frac{q}{\hbar} \frac{1}{N_{\text{kp}} S_{\text{UC}}} \sum_{l}^{N_{\text{UC}}^{\text{orb}}} \sum_{\mathbf{k} \in \text{BZ}}^{N_{\text{kp}}} |\nu_{l}(\mathbf{k})|$$

$$\times \left[ f(E_{l}(\mathbf{k}) + U_{\text{C}} - E_{\text{FL}}) - f(E_{l}(\mathbf{k}) + U_{\text{C}} - E_{\text{FR}}) \right],$$

(1)

$$v_l(\mathbf{k}) = \frac{1}{\hbar} \frac{\mathrm{d}E_l(\mathbf{k})}{\mathrm{d}\mathbf{k}} = \frac{1}{\hbar} \left\langle \psi_l(\mathbf{k}) \left| \frac{\mathrm{d}H(\mathbf{k})}{\mathrm{d}\mathbf{k}} \right| \psi_l(\mathbf{k}) \right\rangle. \tag{2}$$

Here,  $N_{\rm kp}$  is the total number of **k** sampling points within the 1st BZ;  $N_{\rm UC}^{\rm orb}$  is the total number of orbitals in the unit cell; q=-e is the charge of an electron;  $E_l({\bf k})$  and  $v_l({\bf k})$  are the energy and the group velocity for the energy eigenstate  $|\psi_l({\bf k})\rangle$ , respectively; f(E) is the Fermi distribution function, where  $E_{\rm FL/FR}$  is the Fermi energy in the left/right electrode; and  $U_{\rm C}$  is the electrostatic potential of the channel. Note that in the case of nanoribbons, the current, not the current density, is derived because the wavenumber direction is considered only in one dimension.

# C. Capacitance model considering interface trapped charge

In this subsection, we propose a computational methodology to analyze FETs with interface trapping charges with the assumption of the following properties. First, only trapping charges near the interface are considered, and trapping on defects inside the bulk oxide film are not considered. Second, the effect of trapping charges is uniformly distributed throughout the channel. The given trapping/de-trapping time constants and the interface density of

states are used, and the interface density of states is assumed to be constant with respect to energy.

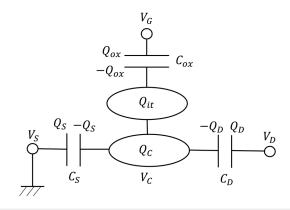

The channel voltage  $V_{\rm C}$  actually felt by electrons in the graphene channel is diminished from the applied gate voltage  $V_{\rm G}$  due the channel induced charge  $Q_{\rm C}$  and the interface trapped charge  $Q_{\rm it}$ . To calculate the channel electrostatic potential  $U_{\rm C}=-eV_{\rm C}$  taking the channel and the trapped charge into account, we use a capacitance model that considers the FET as a set of capacitors. Figures 1 and 3 show the geometry of the FETs considered in the present study and the corresponding capacitance model that is electrostatically equivalent to Fig. 1. In this model, the following equation holds:

$$Q_{\rm C} + Q_{\rm it} = C_{\rm ox}(V_{\rm C} - V_{\rm G}) + C_{\rm D}(V_{\rm C} - V_{\rm D}) + C_{\rm S}(V_{\rm C} - V_{\rm S}),$$

(3)

where  $C_S$  and  $C_D$  are the source and drain capacitances derived from the metal–semiconductor junction, respectively;  $C_{ox}$  is the gate oxide capacitance; and  $V_S$  and  $V_D$  are the source and drain voltages, respectively. Assuming source grounding and  $C_S$ ,  $C_D \ll C_{ox}$ , Eq. (3) can be rewritten as

$$V_{\rm C} = V_{\rm G} + \frac{Q_{\rm C}(V_{\rm C})}{C_{\rm ox}} + \frac{Q_{\rm it}(V_{\rm C})}{C_{\rm ox}},$$

(4)

where we emphasize that  $Q_{\rm C}$  and  $Q_{\rm it}$  are functions of  $V_{\rm C}$ . The channel charge  $Q_{\rm C}$  can be expressed as the product of the channel area, the elementary charge, and the number of electrons per unit area as follows:

$$Q_{\rm C}(V_{\rm C}) = S_{\rm channel} \times (-e) \times \frac{N_{\rm ele/UC}^{\rm neq} - N_{\rm ele/UC}^{\rm eq}}{S_{\rm UC}}, \tag{5}$$

where  $S_{\text{channel}}$  is the channel area,  $N_{\text{ele/UC}}^{\text{neq}}$  is the number of electrons per unit cell in the non-equilibrium state, and  $N_{\text{ele/UC}}^{\text{eq}}$  is the number of electrons per unit cell in the charge-neutral state ( $N_{\text{ele/UC}}^{\text{eq}} = 2$  for

**FIG. 3.** Capacitance model electrostatically equivalent to the FET geometry shown in Fig. 1.

graphene without doping). Here,  $N_{\rm ele/UC}^{\rm neq}$  is calculated as

$$N_{\text{ele/UC}}^{\text{neq}} = \frac{2}{N_{kp}} \sum_{l}^{N_{\text{orb/UC}}} \sum_{k \in BZ}^{N_{kp}} \times \left[ \frac{f(E_{l}(\mathbf{k}) + U_{\text{C}} - E_{\text{FL}})}{2} + \frac{f(E_{l}(\mathbf{k}) + U_{\text{C}} - E_{\text{FR}})}{2} \right], \quad (6)$$

with  $E_{\rm FL/FR}$  being the Fermi energy of the left/right electrode, defined in terms of the drain voltage  $V_{\rm D}$  as  $E_{\rm FL}=E_{\rm F}$  and  $E_{\rm FR}=E_{\rm F}-eV_{\rm D}$ .

Before describing how to derive  $Q_{\rm it}$ , we will discuss the assumed phenomenon. It is known that hysteresis can be observed in the drain current  $I_{\rm D}$  as a function of  $V_{\rm G}$  depending on the surface condition of the gate oxide film in contact with the channel material.  $^{27-29}$  In the case of SiO<sub>2</sub> oxide films, hysteresis characteristics are observed when there are many silanol groups (–SiOH) on the surface of the gate oxide film due to the trapping and de-trapping of channel electrons at the interface states derived from these groups.  $^{30}$

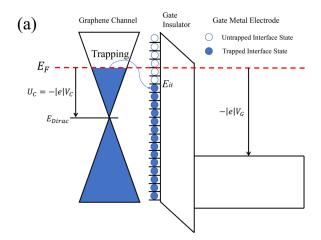

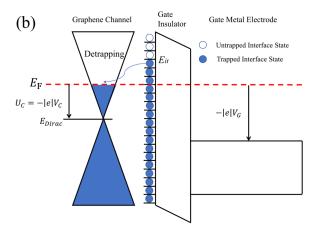

We introduce a model of the interface trap charge as shown in Fig. 4. Electron transfer from the channel to the interface states (trapping) occurs when the Fermi level  $E_{\rm F}$  is higher than the top of the occupied interface level (hereafter denoted as  $E_{\rm it}$ ), while that from the interface states to the channel (de-trapping) occurs when  $E_{\rm F}$  is lower than  $E_{\rm it}$ . In the subsequent formulation to calculate  $E_{\rm it}$ , we set the origin of energy at the Dirac point of graphene so that the Fermi energy is always positioned at  $E=eV_{\rm C}$  in graphene. On the basis of this phenomenological treatment, for a given arbitrary time varying gate voltage profile  $V_{\rm G}^{(j)}$  (not necessarily a monotonically increasing/decreasing function) with a time index j and time step  $\Delta t$ ,  $Q_{\rm it}$  at the jth  $V_{\rm G}$  is calculated sequentially starting from  $Q_{\rm it}^{(0)}$  according to the following recurrence equations:

$$Q_{it}^{(j)} = Q_{it}^{(j-1)} + \Delta Q_{it}^{(j)}, \tag{7}$$

$$\Delta Q_{\rm it}^{(j)} = -|e| \int_{E_u^{(j-1)}}^{E_{\rm it}^{(j)}} D_{\rm it}(E) dE, \tag{8}$$

$$E_{it}^{(j)} = \left(eV_{\rm C}(V_{\rm G}^{(j)}) - E_{it}^{(j-1)}\right) \left(1 - \exp(-\Delta t/\tau_{\rm trap})\right) + E_{it}^{(j-1)},$$

(9)

$$E_{\rm it}^{(0)} = eV_{\rm C}(V_{\rm G}^{(0)}), Q_{\rm it}^{(0)} = 0,$$

(10)

where  $E_{\rm it}$  is the top of the occupied interface level measured from the Dirac point in graphene,  $V_{\rm C}(V_{\rm G})$  is the graphene channel potential for a given gate voltage  $V_{\rm G}$ ,  $D_{\rm it}(E)$  (eV<sup>-1</sup> m<sup>-2</sup>) is the interface density of states, and  $\tau_{\rm trap}$  (ms) is the trapping/de-trapping time constant. On the basis of the experimental results of previous studies,  $D_{\rm it}(E)$  in Eq. (8) is treated as an energy independent constant.<sup>29</sup> In the special case of the linearly increasing or decreasing gate voltage, the time step is given in terms of the gate voltage sweep rate  $\chi_{\rm sweep}$  (V/ms) as  $\Delta t = \Delta V_{\rm G}/\chi_{\rm sweep}$ , which is interpreted as the time required to sweep the gate voltage by  $\Delta V_{\rm G}$ . The factor

**FIG. 4.** Energy band diagram of FET and schematization of the interfacial trapping/de-trapping process at different bias conditions: (a)  $E_{it} < E_F$  and (b)  $E_{it} > E_F$ . This figure is based on Figs. 2(c) and 2(d) in Ref. 29.

$1-\exp(-\Delta t/ au_{\rm trap})$  is the probability that the interface states are actually trapped during the time step  $\Delta t$ .

In our actual simulations, this factor  $1-\exp(-\Delta t/\tau_{\rm trap})$  is approximated as  $\Delta t/\tau_{\rm trap}$  since  $\Delta t \ll \tau_{\rm trap}$  in our simulation conditions. Equation (10) is used as the initial condition of the recurrence formulas. That is, under the assumption that the gate voltage is fixed at its initial value  $V_{\rm G}^{(0)}$  for a sufficiently long time, the trapping/de-trapping probability becomes one and then  $E_{\rm it}^{(0)}$  coincides with  $eV_{\rm C}(V_{\rm G}^{(0)})$ .

In the above proposed model, various electronic properties, such as the channel charge density, the channel potential, and the interface density of states, are assumed to be homogeneous. However, our model can be generalized to account for their spatial inhomogeneity, where the nonequilibrium Green function (NEGF) method plays a central role in performing a self-consistent calculation with the Poisson equation to account for the real spatial effects of the channel potential.<sup>31</sup>

#### **III. RESULTS AND DISCUSSIONS**

#### A. Hysteresis of conduction characteristics

To clarify the usefulness of the above proposed method, we first examine the case of linear gate voltage sweep and analyze the hysteretic properties. We employ the following parameter values in this paper unless otherwise noted. The parameter values for interface trap are  $\tau_{\rm trap}=100~{\rm ms}$  and  $D_{\rm it}=1.875\times10^{16}~{\rm eV^{-1}~m^{-2}}$ , which are experimentally reported values. Since we consider the double-gated FET structure as shown in Fig. 1, the value of  $D_{\rm it}$  is actually doubled. The relative permittivity of the SiO<sub>2</sub> oxide film was given as  $\kappa=3.8$  and the thickness of the gate oxide film as  $t_{\rm ox}=3~{\rm nm}$ .

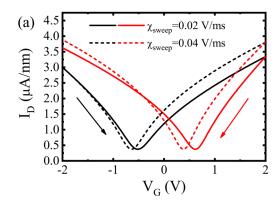

In this subsection, we biased the graphene FETs with  $V_{\rm D}=0.1~{\rm V}$  and swept  $V_{\rm G}$  linearly from -2 to  $2~{\rm V}$  (forward sweep) with the various gate sweep rate  $\chi_{\rm sweep}$ , assuming that  $V_{\rm G}$  was initially fixed at  $-2~{\rm V}$  for a sufficiently long time and subsequently swept  $V_{\rm G}$  from 2 to  $-2~{\rm V}$  (backward sweep) with the same sweep rate. The calculated results of the  $I_{\rm D}$ - $V_{\rm G}$  properties are shown in Fig. 5

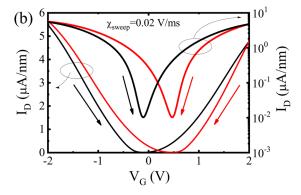

**FIG. 5.** Conduction characteristics of graphene-based FETs under linear gate voltage sweeps for (a) graphene and (b) 7(3)/9(2)-AGNR to demonstrate the appearance of the hysteresis behavior. In both (a) and (b), black and red curves correspond to the forward sweep (from -2 to 2 V) and backward sweep (from 2 to -2 V), respectively. In (a), results for two different gate sweep rates  $\chi_{\rm sweep}=0.02$  (solid curves) and 0.04 (dashed curves) V/ms are compared, while in (b), the result for  $\chi_{\rm sweep}=0.02$  is plotted in the linear (left axis) and logarithmic (right axis) scales. We note that in (b), the current flowing through AGNR is divided by the effective AGNR width to obtain the current density (see the text for detail).

for graphene (a) and AGNR (b). We note that in (b), the current flowing through 7(3)/9(2)-AGNR (in units of  $\mu$ A) is divided by the effective AGNR width 1.08 nm to obtain the current density to compare with the case of graphene, where the effective width of 7(3)/9(2)-AGNR is defined by  $[N_7(7+1)+N_9(9+1)] \times (\sqrt{3}a_0/2)/N_{\text{tot}}$  with  $N_7=3$ ,  $N_9=2$ , and  $N_{\text{tot}}=N_7+N_9$ .

Here, it is observed that the overall conduction characteristics for backward  $V_{\rm G}$  sweep is shifted to the positive  $V_{\rm G}$  direction compared to that for backward V<sub>G</sub> sweep. The direct reason for this behavior is that the channel voltage  $V_C$  at a given specific  $V_G$  is lower for the backward sweep case than for the forward sweep case, where the behind physical mechanism is that the interface trapped charge  $[Q_{it}(V_C) < 0]$  is continuously accumulated during the forward sweep, and in the subsequent backward sweep, this accumulated (negative) trapped charge causes the value of  $V_C$  to be less than the forward sweep through the third term in the RHS of Eq. (4). This result agrees qualitatively with the experimentally observed behavior, 21,28,29 suggesting that our model can capture the essential physics in the trap/detrap behavior. We also note that the amount of the shift of the  $I_D$ - $V_G$  curve due to the interface trapped charge is larger for smaller values of gate sweep rate  $\chi_{\text{sweep}}$ . This is because slower gate sweep results in larger probability for electrons to be trapped at the interface. Similar behavior can be observed for the case of 7(3)/9(2)-AGNR (hereafter, we simply call AGNR) channel as demonstrated in Fig. 5(b). It can be seen that the opening of a bandgap of about 0.50 eV creates an off region where almost no  $I_D$  flows. The width of the off region (transport gap) is approximately 200 mV if we define the off state as when  $I_{\rm D} < 20\,{\rm nA}$ . Such a relatively narrow but clear transport gap and the significant shift of the  $I_D$ – $V_G$  curve due to the interface trapped charge are preferable in designing energy efficient synaptic devices utilizing a biologically plausible spike voltage displacement of approximately 100-150 mV.

#### **B. Synaptic FET application**

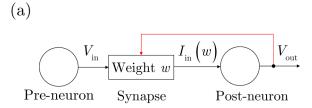

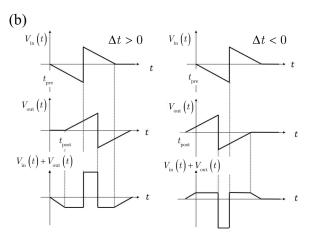

So far, we have discussed the hysteresis behavior of graphene and AGNR FETs due to charge trap/detrap processes. Such hysteresis behavior can be used as a key mechanism to realize synaptic functionality as explained below. In Fig. 6(a), we show the schematic illustration of the synapse-neuron system premised in this study, where the pre-neuron is connected to the post-neuron via the synapse made of FET. Then, the superposition of voltage spikes launched by the pre- and post-neurons [i.e.,  $V_{in}(t) + V_{out}(t)$  in Fig. 6(b)] is assumed to be used as the time-dependent gate voltage  $V_{\rm G}(t)$  applied to synapse FET. Here, we illustrate in Fig. 6(b) the representative example of the time-dependence of  $V_{in}(t)$ ,  $V_{out}(t)$ , and  $V_{\rm G}(t) = V_{\rm in}(t) + V_{\rm out}(t)$ . As illustrated in this figure, the time-dependence of  $V_G(t)$  is different depending on whether  $\Delta t \equiv t_{\rm post} - t_{\rm pre} > 0$  or  $\Delta t < 0$ . Then, the required functionality of synaptic FET is that the electronic conduction property (more specifically the current or conductance at a reference gate voltage, for example, at  $V_G = 0$ ) is changed between before and after completing the voltage pulse  $V_G(t)$  shown in Fig. 6(b) in a way depending on the sign and/or value of  $\Delta t$ . This process is interpreted as the spike-timing dependent update of the synapse weight represented by the conductance value and is the essence of the mechanism

**FIG. 6.** (a) Schematic illustration of a synapse-neuron system. (b) Representative example of time-dependence of  $V_{\rm in}(t)$ ,  $V_{\rm out}(t)$ , and  $V_{\rm G}(t) = V_{\rm in}(t) + V_{\rm out}(t)$ . Time-dependence of  $V_{\rm G}(t)$  is different depending on whether  $\Delta t \equiv t_{\rm post} - t_{\rm pre} > 0$  or  $\Delta t < 0$ .

called the spike-timing dependent plasticity (STDP). Therefore, the performance of synaptic FET can be evaluated by the current change rate (interpreted as the normalized synapse weight change)  $\Delta w \equiv (I_{\rm D, \, after} - I_{\rm D, \, before})/I_{\rm D, \, before},$  where  $I_{\rm D, \, before(after)}$  is the drain current at a reference  $V_{\rm G}$  before (after) the voltage pulse  $V_{\rm G}(t)$  that starts and ends at  $V_{\rm G}=0$ . We note that normalized synapse weight w is updated every time a new voltage pulse is applied, and the resulting update of w is interpreted as the update of weight in the context of the spiking neural network (SNN).

# C. Comparison of the conductance change rate between graphene and AGNR superlattices

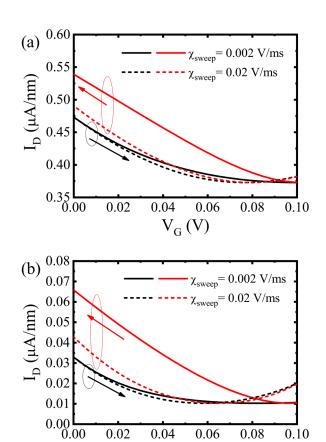

To focus our discussion on how the weight w is changed by voltage pulses in graphene and AGNR FET systematically, we assume the simple linear functional forms of the voltage pulse [instead of a more realistic but complicated pulse form, such as illustrated in Fig. 6(b)], expressed as  $V_G(t) = \chi_{\rm sweep} t$  for  $t \leq t_0$ ,  $V_G(t) = \chi_{\rm sweep} (2t_0 - t)$  for  $t_0 < t \leq 2t_0$ , and otherwise  $V_G(t) = 0$ , where  $t_0 \equiv V_{\rm Gmax}/\chi_{\rm sweep}$  is the time required to reach the maximum gate voltage  $V_{\rm Gmax}$  for a given gate sweep rate  $\chi_{\rm sweep}$ . In Fig. 7, we show the forward and backward  $I_D - V_G$  curves for graphene and AGNR cases, where we set  $V_{\rm Gmax} = 0.1 \, {\rm V}$  while  $\chi_{\rm sweep} = 0.002$  or  $0.02 \, {\rm V/ms}$ . By comparing the current at  $V_G = 0$  between the forward and backward sweep, one can estimate the weight change  $\Delta w$  as  $\Delta w = 13.8$  (4.2)% for graphene and

**FIG. 7.** Conduction characteristics and a conductance change rate of graphene-based FETs under a 0–100 mV linear gate voltage sweep: (a) graphene and (b) 7(3)/9(2)-AGNR. For the AGNR case, the current is divided by the effective AGNR width to obtain the current density. In both (a) and (b), black and red curves correspond to the forward sweep (from -2 to 2 V) and the backward sweep (from 2 to -2 V), respectively, and the results for two different gate sweep rates  $\chi_{\rm sweep}=0.002$  (solid curves) and 0.02 (dashed curves) V/ms are compared.

$V_{G}(V)$

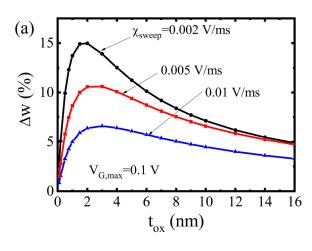

$\Delta w = 102.5$  (28.6)% for AGNR FET for  $\chi_{\rm sweep} = 0.002$  (0.02) V/ms. A large  $\Delta w$  means a large memory window, suggesting that 7(3)/9 (2)-AGNR can construct a better synaptic FET than graphene. So far, we have assumed that the gate oxide thickness is  $t_{\rm ox} = 3$  nm. Next, we consider how  $t_{\rm ox}$  and thus  $C_{\rm ox}$  influence the synapse weight  $\Delta w$ . According to Eq. (4), one can see that  $C_{\rm ox}$  suppresses the effect of the channel charge  $Q_{\rm c}$  and interface trap charge  $Q_{\rm it}$  on the channel voltage  $V_{\rm C}$ . If the effect of  $Q_{\rm C}$  is large,  $V_{\rm C}$  becomes small and the effect of  $V_{\rm G}$  degrades (quantum capacitance effect), which in turn reduces  $Q_{\rm it}$  from Eqs. (7)–(9). From this observation, it looks that it is preferable to increase  $C_{\rm ox}$  to diminish the effect of  $Q_{\rm C}$ . However, larger  $C_{\rm ox}$  results in the decrease of  $Q_{\rm it}$  and suppresses the hysteresis behavior, which is not preferable as a synaptic device. Therefore, it is important to optimize  $C_{\rm ox}$  to maximize the synapse weight change  $\Delta w$ . For this purpose, we plot  $\Delta w$  as a function of  $t_{\rm ox}$

**FIG. 8.** Synapse weight changes  $\Delta w$  in the case of linear voltage sweep (see the text for detail) are plotted for (a) graphene and (b) 7(3)/9(2)-AGNR FETs as a function of the SiO<sub>2</sub> gate oxide film thickness  $t_{\rm ox}$ . Results for various gate sweep rates  $\chi_{\rm sweep}$  are compared.

of the SiO<sub>2</sub> gate oxide film for various  $\chi_{\rm sweep}$  in Fig. 8. It can be seen that  $\Delta w$  reaches a maximum at  $t_{\rm ox}=2-3$  nm. One interesting feature seen here is that a faster gate sweep rate  $\chi_{\rm sweep}$  results in the shift of the  $\Delta w$  peak to the thicker  $t_{\rm ox}$  direction. This is because a faster gate sweep results in smaller amounts of trapped charge. Then, a too thin  $t_{\rm ox}$  suppresses the hysteresis behavior. We also note that the thickness  $t_{\rm ox}=2-3$  nm is around the scaling limit for a SiO<sub>2</sub> gate when tunneling is concerned, indicating that the scaling strategy works well for the synapse FET as well.

# D. Long-term potentiation (LTP)/long-term depression (LTD) properties of synaptic FETs

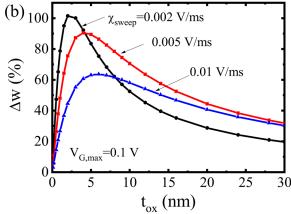

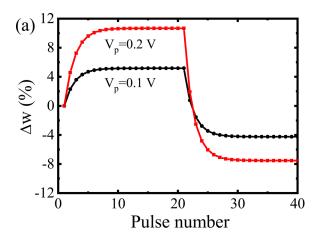

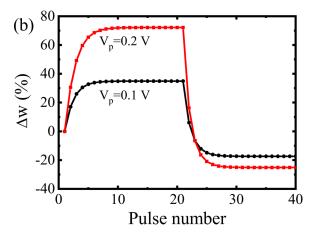

So far, we have considered the linear gate sweep to clarify the fundamental aspects of graphene-based synapses. Finally, we consider a more experimentally accessible case, a square pulse train sweep given by  $V_{\rm G}(t) = \sum_i V_i \theta(t-t_i) \theta(t_i + T_{\rm pulse} - t)$ , where  $V_i$  is the pulse voltage,  $t_i$  is the pulse arrival time, and  $T_{\rm pulse}$  is the

pulse width. We assume that i runs from 1 to 40,  $V_i = V_p$  for  $1 \le i \le 20$  and  $V_i = -V_p$  for  $21 \le i \le 40$  with  $V_p$  mentioned later,  $T_{\rm pulse} = 5$  ms, and  $t_i = \left(T_{\rm pulse} + T_{\rm interval}\right)i$  with  $T_{\rm interval} = 20$  ms. In Fig. 9, we show the results for graphene (a) and AGNR (b), where the results for two different pulse voltage values  $V_p = 0.1$  and 0.2 V are compared. For both graphene and AGNR, the calculated  $\Delta w$  gradually increases as the multiple positive voltage pulses are applied and is saturated as the charging process is completed. When the pulse voltage becomes negative at i = 21,  $\Delta w$  is abruptly turned to negative, meaning that the synapse weight is turned from potentiation to depression and is interpreted as the realization of so-called long-term potentiation (LTP) and long-term depression (LTD), respectively. As we can expect from Figs. 7 and 8, AGNR shows a larger magnitude of  $\Delta w$ . It is also observed that the LTP

**FIG. 9.** Synapse weight changes  $\Delta w$  in the case of square pulse train voltage sweep (see the text for detail) are plotted for (a) graphene and (b) 7(3)/9 (2)-AGNR FETs as a function of the  $SiO_2$  gate oxide film thickness  $t_{\rm ox}$ . Results for two different pulse voltage values  $V_{\rm p}=0.1$  and 0.2 V are compared. We note that the first and second half of the voltage sweep correspond to the synaptic long-term potentiation (LTP) and synaptic long-term depression (LTD), respectively, as explained in the text.

process shows larger  $|\Delta w|$  than in the LTD process. Such asymmetricity of  $|\Delta w|$  between LTP and LTD is more significant in the AGNR case than graphene. To equalize the magnitudes of the positive and negative changes, the pulse waveform must be adjusted. The confirmed saturation and asymmetry have also been experimentally observed in the synaptic FETs based on MoTe<sub>2</sub> as a channel.<sup>33</sup> The above-mentioned asymmetry is basically due to the positive drain voltage  $V_{\rm D}$  (= 0.1 V), which pushes the minimum current voltage to the positive V<sub>G</sub> side. The larger asymmetry in GNR superlattices can be attributed to the presence of off-regions, which are absent in graphene. Although it has been said that synaptic devices with symmetry and linearity are ideal, it is noted that STDP-based unsupervised SNNs obtain high classification accuracy values in the modified National Institute of Standards and Technology (MNIST) classification by having synapses with nonlinear behavior.3

#### IV. CONCLUSION

In this paper, we proposed a compact computational method based on the capacitance model for the efficient design of graphenebased synaptic field effect transistors (FETs), in which the hysteresis of conduction characteristics due to the channel-gate interface trap was used as synaptic plasticity. Using our method to calculate the conduction properties of graphene and armchair graphene nanoribbon (AGNR) superlattice FETs, we have succeeded to obtain the hysteresis behavior in the  $I_D$ - $V_G$  curves of graphene and AGNR FETs, where it was clarified that the current modulation due to the hysteresis behavior (interpreted as the synaptic weight change) can be tuned by changing the gate sweep rate  $\chi_{\text{sweep}}$  and the gate oxide thickness  $t_{\text{ox}}$ . Moreover, it was shown that the AGNR can achieve an efficient conductance change rate  $\Delta w$ , which is approximately 7.4 times that of graphene. It was also found that  $\Delta w$  was the greatest when the gate oxide thickness was around 2-3 nm, which is near the limit of miniaturization. We have also examined the case of square voltage pulse train sweep and demonstrated the pulse voltage dependent asymmetricity in the long-term potentiation/long-term depression behaviors. These results suggest that the proposed synaptic FETs are a promising approach to realize large scale integration chips for biological timescale computation.

#### **ACKNOWLEDGMENTS**

This work was partially supported by JSPS KAKENHI under Grant No. 19H04546. The authors would like to thank Enago (www.enago.jp) for the English language review.

#### **AUTHOR DECLARATIONS**

#### **Conflict of Interest**

The authors have no conflicts to disclose.

#### **DATA AVAILABILITY**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### **REFERENCES**

- <sup>1</sup>J. Misra and I. Saha, Neurocomputing 74(1-3), 239-255 (2010).

- <sup>2</sup>J. Hasler and B. Marr, Front. Neurosci. 10, 118 (2013).

- <sup>3</sup>S. Furber, J. Neural Eng. 13, 051001 (2016).

- <sup>4</sup>A. Taherkhani, A. Belatreche, Y. Li, G. Cosma. L. P. Maguire, and T. M. McGinnity, Neural Netw. **122**, 253–272 (2020).

- <sup>5</sup>K. Kumarasinghe, N. Kasabov, and D. Taylor, Sci. Rep. 11, 2486 (2021).

- <sup>6</sup>F. Boi, T. Moraitis, V. D. Feo, F. Diotalevi, C. Bartolozzi, G. indiveri, and A. Vato, Front. Neurosci. **10**, 563 (2016).

- <sup>7</sup>W. Zhongrui, J. Saumil, S. Sergey E, J. Hao, M. Rivu, L. Peng, J. Miao, G. Ning, S. John Paul, L. Zhyong, W. Qing, B. Mark, L. Geng-Lin, X. Huolin. L, W. L. Stanley, X. Qiangfei, and Y. J. Joshua, Nat. Mater. 16, 101–108 (2017).

- <sup>8</sup>W. Yi, K. K. Tsang, S. K. Lam, X. Bai, J. A. Crowell, and E. A. Flores, Nat. Commun. 9, 4661 (2018).

- <sup>9</sup>V. K. Sangwan and M. C. Hersam, Nat. Nanotechnol. **15**, 517–528 (2020).

- <sup>10</sup>H. Han, H. Yu, H. Wei, J. Gong, and W. Xu, Nano Micro Small 15, 1900695 (2019).

- <sup>11</sup>H. Zhong, Q-C. Sun, G. Li, J.-Y. Du, H.-Y. Huang, E.-J. Guo, M. He, C. Wang, G.-Z. Yang, C. Ge, and K.-J. Jin, Chin. Phys. B 29, 040703 (2020).

- <sup>12</sup>D. Akinwande, C. J. Brennan, J. S. Bunch, P. Egberts, J. R. Felts, H. Gao, R. Huang, J. Kim, T. Li, Y. Li, K. M. Liechti, N. Lu, H. S. Park, E. J. Reed, P. Wang, B. I. Yakobson, T. Zhang, Y. Zhang, Y. Zhou, and Y. Zhu, Extreme Mech. Lett. 13, 42–77 (2017).

- <sup>13</sup>K. S. Novoselov, V. I. Fal'ko, L. Colombo, P. R. Gellert, M. G. Schwab, and K. Kim, Nature 490, 192 (2012).

- <sup>14</sup>S. Souma and M. Ogawa, Appl. Phys. Lett. **104**, 183103 (2014).

- 15T. Ko, H. Li, S. A. Mofid, C. Yoo, E. Okogbue, S. S. Han, M. S. Shawkat, A. Krishnaprasad, M. M. Islam, D. Dev, Y. Shin, K. H. Oh, G. Lee, T. Roy, and Y. Jung, iScience 23(11), 101676 (2020).

- <sup>16</sup>T. F. Schranghamer, A. Oberoi, and S. Das, Nat. Commun. 11, 5474 (2020).

- <sup>17</sup>I. E. Esqueda, X. Yan, C. Rutherglen, and A. Kane, ACS Nano 12(7), 7352–7361 (2018).

- <sup>18</sup>H. Wang, N. C. Laurenciu, Y. Jiang, and S. D. Cotofana, in *2019 ISCAS Nano Devices & Circuits* (IEEE, 2019).

- 19H. Wang, N. C. Laurenciu, Y. Jiang, and S. D. Cotofana, in 2019 IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH) (IEEE, 2019).

- <sup>20</sup>M. Winters, E. Ö. Sveinbjörnsson, and N. Rorsman, J. Appl. Phys. 117, 074501 (2015).

- <sup>21</sup>M. Bonmann, A. Vorobiev, J. Stake, and O. Engström, J. Vac. Sci. Technol. B 35, 01A115 (2017).

- <sup>22</sup>M. Winters, E. Ö. Sveinbjörnsson, C. Melios, O. Kazakova, W. Strupiński, and N. Rorsman, AIP Adv. 6, 085010 (2016).

- <sup>23</sup> A. Pacheco-Sanchez, N. Mavredakis, P. C. Feijoo, W. Wei, E. Pallecchi, H. Happy, and D. Jiménez, IEEE Trans. Electron Devices 67, 5790 (2020).

- <sup>24</sup>G. Oliver, W. Shiyong, Y. Xuelin, P. Carlo A, B. Gabriela, D. Colin, C. Andrew, M. Vincent, F. Xinliang, N. Akimitsu, M. Klaus, R. Rascal, and F. Roman, Nature 209, 209–213 (2018).

- <sup>25</sup>D. J. Rizzo, G. Veber, T. Cao, C. Bronner, T. Chen, F. Zhao, H. Rodriguez, S. G. Louie, M. F. Crommie, and F. R. Fischer, Nature **560**, 204–208 (2018).

- <sup>26</sup>K. Arihori, M. Ogawa, S. Souma, J. Sato-Iwanaga, and M. Suzuki, J. Appl. Phys. **130**, 084302 (2021).

- <sup>27</sup>H. Wang, Y. Wu, C. Cong, J. Shang, and T. Yu, ACS Nano 4(12), 7221–7228 (2010).

- 28 J. Yang, K. Jia, S. Yajuan, and C. Yang, J. Semicond. 35(9), 094003 (2014).

- 29D. Mao, S. Wang, S. Peng, D. Zhang, J. Shi, X. Huang, M. Asif, and Z. Jin, J. Mater. Sci.: Mater. Electron. 27, 9847–9852 (2016).

- **30**K. Nagashio, T. Yamashita, J. Fujita, T. Nishimura, K. Kita, and A. Toriumi, in 2010 International Electron Devices Meeting, San Francisco, CA (IEEE, 2010).

- S. Souma and M. Ogawa, J. Appl. Phys. 127, 094304 (2020).

U. Jung, Y. J. Kim, Y. Kim, Y. G. Lee, and B. H. Lee, IEEE Electron Device

- Lett. 36(4), 297 (2015).

33S. Rehman, M. F. Khan, M. K. Rahmani, H. Kim, H. Patil, S. A. Khan,

- M. H. Kang, and D. Kim, Nanomaterials 10(12), 2326 (2020).

S. Brivio, D. R. B. Ly, E. Vianello, and S. Spiga, Front. Neurosci. 15, 27 (2021).