PDF issue: 2025-01-16

## Development and Study of the Level-1 Trigger System for the ATLAS Experiment at the Large Hadron Collider

Ichimiya, Ryo

<mark>(Degree)</mark> 博士(理学)

(Date of Degree) 2006-03-25

(Date of Publication) 2012-08-27

(Resource Type) doctoral thesis

(Report Number) 甲3695

(URL) https://hdl.handle.net/20.500.14094/D1003695

※ 当コンテンツは神戸大学の学術成果です。無断複製・不正使用等を禁じます。著作権法で認められている範囲内で、適切にご利用ください。

### 博 士 論 文

Doctoral Dissertation

Development and Study of the Level-1 Trigger System for the ATLAS Experiment at the Large Hadron Collider (LHC 加速器における ATLAS 実験用 Level-1 トリガシステムの開発及びその研究)

Ryo Ichimiya

February, 2006

Graduate School of Science and Technology Kobe University

#### Abstract

The main objectives of the ATLAS Experiment at the Large Hadron Collider are to search for the Higgs boson(s), to verify the Standard Model, to measure Standard Model parameters more precisely and to explore the physics beyond the Standard Model in higher energy range of up to a few TeV. This experiment has to handle tremendous data flow, far more than any experiment have done ever. Therefore extremely powerful trigger system to reduce the event rate efficiently is essential. The ATLAS Trigger system consists of three trigger stages: Level-1 Trigger, Level-2 Trigger and Event Filter. In order to extract interesting physics results efficiently from high luminosity proton-proton interactions in high radiation environment, special architecture and devices are required in the Level-1 Trigger and data acquisition system (TDAQ).

The author developed two key devices for the TDAQ of the ATLAS Endcap muon Trigger system which use detectors called Thin Gap Chamber (TGC). This Trigger system was designed through a physics performance study with Monte Carlo simulation. Furthermore a trigger logic simulator has developed to check the correctness trigger logic system. Due to the space availability and timing consideration, the TGC front-end electronics will be placed on the TGC surface where the radiation level is high ( $\sim 210$  Gy for ten years). The high radiation level causes not only damage to the devices but also limitation of access for maintenance. This situation made the design work for the trigger electronics much more difficult.

We chose and developed Application Specific Integrated Circuit (ASIC) for the front-end core part of the TDAQ. The ASICs are manufactured using the latest technology to have inherently higher radiation tolerance level. It also has favorable characteristics of high-speed data processing, low power consumption, low cost (in mass production) and small area. A lot of efforts were made to develop the ASIC with high enough performance for the ATLAS Experiment.

The Endcap muon Trigger system has flexibility in setting threshold of transverse momentum level to classify incoming muons. This part of function is done at the Sector Logic, the final part of the Endcap muon Trigger system located in electronics hut. We chose to use the latest Field Programmable Gate Array (FPGA) for the Sector Logic. The Sector Logic needs to operate with low latency and needs to have flexibility in setting different threshold level. The author developed the algorithm and made the final prototype of the Sector Logic.

In order to confirm the radiation tolerance of the semiconductor devices used in the Endcap muon Trigger electronics system, we have executed  $\gamma$ -ray and proton beam irradiation tests for these devices.

The ATLAS TDAQ system has been developed and constructed. The ATLAS Experiment is scheduled to start taking data in 2007.

## Acknowledgement

I would like to thank my supervisor Prof. Hiroshi Takeda and Prof. Hisaya Kurashige for their support and guidance over the entire years. I also give my special thanks to Prof. Osamu Sasaki who continuously gave me valuable guidance and support. I would like to express special thanks to Mr. Masahiro Ikeno for technical suggestion and support at the electronics development. I would also like to address special thanks to Prof. Yasuo Arai for technical/theoretical suggestion and support in the development of the ASICs and in the semiconductor irradiation tests. I would like to express thanks to Dr. Hiroyuki Kano for technical support and advice in the ASIC development. I'm very grateful to Dr. Kentaro Mizouchi for co-works in the ASIC development and various discussions with me. I would like to thank to Mr. Takeshi Ogata for co-works for the Sector Logic development. I also would like to express special thanks to Mrs. Yumi Yokoyama for various support of our studies at our laboratory.

I would like to thank to Prof. Takahiko Kondo, Prof. Chikara Fukunaga, Prof. Hiroshi Sakamoto, Dr. Masaya Ishino, Prof. Mitsuaki Nozaki, Prof. Kiyotomo Kawagoe, Dr. Atsuhiko Ochi, Dr. Kazumi Hasuko, Prof. Tokio Kenneth Ohska, Prof. Hiroyuki Iwasaki and Prof. Tomio Kobayashi for their support and advice.

I would like to give special thanks to Prof. Tohru Takeshita for giving a chance to enter this exciting world of experimental particle physics studies.

I would like to thank all colleagues at Kobe University, at the ATLAS TGC Electronics Group and at the ATLAS collaboration.

Finally, I would like to thank my parents and family for their continuous and tremendous support plus encouragement until now.

# Contents

| 0        | Intr | oducti | ion                                                                                         | 9  |

|----------|------|--------|---------------------------------------------------------------------------------------------|----|

| 1        | The  | ATLA   | AS Experiment                                                                               | 12 |

|          | 1.1  | The L  | Large Hadron Collider                                                                       | 12 |

|          |      | 1.1.1  | The LHC Accelerator Complex                                                                 | 12 |

|          |      | 1.1.2  | The Bending (Dipole) Magnets in the LHC                                                     | 14 |

|          | 1.2  | Physic | cs at the ATLAS Experiment                                                                  | 15 |

|          |      | 1.2.1  | The Standard Model                                                                          | 15 |

|          |      | 1.2.2  | Physics Potential                                                                           | 16 |

|          |      | 1.2.3  | Higgs Boson                                                                                 | 17 |

|          | 1.3  | The A  | ATLAS Detector                                                                              | 19 |

|          |      | 1.3.1  | Overview                                                                                    | 19 |

|          |      | 1.3.2  | Inner Detector                                                                              | 20 |

|          |      | 1.3.3  | Calorimetry                                                                                 | 20 |

|          |      |        | 1.3.3.1 Electromagnetic Calorimeter                                                         | 21 |

|          |      |        | 1.3.3.2 Hadronic Calorimeter $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 21 |

|          |      | 1.3.4  | $Muon \ Spectrometer \ \ . \ . \ . \ . \ . \ . \ . \ . \ . $                                | 23 |

|          |      |        | 1.3.4.1 Monitored Drift Tube (MDT) $\ldots \ldots \ldots \ldots \ldots \ldots$              | 24 |

|          |      |        | 1.3.4.2 Cathode Strip Chamber (CSC) $\ldots \ldots \ldots \ldots \ldots \ldots$             | 24 |

|          |      |        | 1.3.4.3 Resistive Plate Chamber (PRC)                                                       | 25 |

|          |      |        | 1.3.4.4 Thin Gap Chamber (TGC)                                                              | 26 |

| <b>2</b> | The  | ATLA   | AS Trigger/Data-Acquisition (TDAQ) System                                                   | 28 |

|          | 2.1  | Level- | 1 (LVL1) Trigger Overview                                                                   | 30 |

|          |      | 2.1.1  | Muon Trigger                                                                                | 31 |

|          | 2.2  | Timin  | ng, Trigger and Control (TTC) distribution system                                           | 32 |

| 3        | The  | Endc   | ap Muon (TGC) Trigger System                                                                | 33 |

|          | 3.1  | Layou  | at and its Algorithm                                                                        | 33 |

|          | 3.2  | Impler | mentation on the Electronics System                                                         | 34 |

|          | 3.3  | Trigge | er Sector                                                                                   | 36 |

|   | 3.4             | Laten  | cy                                                                                                                                                                       | ;      |

|---|-----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 4 | $\mathbf{Syst}$ | tem D  | evelopment Issues 40                                                                                                                                                     | )      |

|   | 4.1             | Techn  | ology selections for the system components                                                                                                                               | )      |

|   | 4.2             | Slave  | Board ASIC                                                                                                                                                               | ;      |

|   |                 | 4.2.1  | Overview                                                                                                                                                                 | ;      |

|   |                 | 4.2.2  | Master-Slave Structure                                                                                                                                                   | F      |

|   |                 | 4.2.3  | Block Diagram                                                                                                                                                            | F      |

|   |                 | 4.2.4  | Input Block                                                                                                                                                              | )      |

|   |                 | 4.2.5  | Low- $p_T$ trigger Block                                                                                                                                                 | ;      |

|   |                 |        | 4.2.5.1 Coincidence Matrix for Doublets pair (DSB) 47                                                                                                                    | ,      |

|   |                 |        | 4.2.5.2 Triplet Slave Board (TSB) $\ldots \ldots \ldots$ | )      |

|   |                 |        | 4.2.5.3 EI/FI Slave Board (EFSB) $\ldots \ldots 53$                                                       | ;      |

|   |                 | 4.2.6  | Readout Block                                                                                                                                                            | ;      |

|   |                 | 4.2.7  | JTAG Block                                                                                                                                                               | ;      |

|   |                 | 4.2.8  | Implementation on the ASIC                                                                                                                                               | 3      |

|   |                 | 4.2.9  | Validation                                                                                                                                                               | 3      |

|   | 4.3             | Sector | Logic                                                                                                                                                                    | _      |

|   |                 | 4.3.1  | Overview                                                                                                                                                                 | _      |

|   |                 | 4.3.2  | Design of the Sector Logic                                                                                                                                               | _      |

|   |                 |        | 4.3.2.1 R- $\phi$ coincidence                                                                                                                                            | 2      |

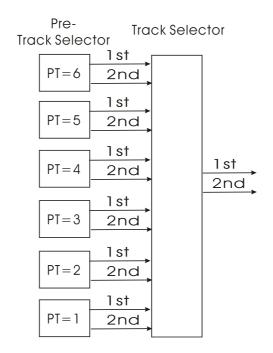

|   |                 |        | 4.3.2.2 Track Selection Logic (Pre-Track Selector, Track Selector) 63                                                                                                    | \$     |

|   |                 |        | 4.3.2.3 Decoder                                                                                                                                                          | \$     |

|   |                 |        | 4.3.2.4 Encoder                                                                                                                                                          | )      |

|   |                 | 4.3.3  | The first prototype (Prototype-0)                                                                                                                                        | 2      |

|   |                 |        | 4.3.3.1 Specification                                                                                                                                                    | 2      |

|   |                 |        | 4.3.3.2 Implementation                                                                                                                                                   | \$     |

|   |                 |        | 4.3.3.3 Validation                                                                                                                                                       | F      |

|   |                 |        | 4.3.3.4 Integration test with the MUCTPI                                                                                                                                 | F      |

|   |                 |        | 4.3.3.5 Test beam at H8 beam line in CERN                                                                                                                                | F      |

|   |                 | 4.3.4  | Final Design of whole Sector Logic system                                                                                                                                | ;<br>) |

|   |                 |        | 4.3.4.1 Final Design of Sector Logic board                                                                                                                               | 7      |

|   | 4.4             | Radia  | tion Tolerance                                                                                                                                                           | )      |

|   |                 | 4.4.1  | Test for Total Ionization Dose (TID)                                                                                                                                     | )      |

|   |                 |        | 4.4.1.1 TID Test Procedure                                                                                                                                               | )      |

|   |                 |        | 4.4.1.2 Results of the TID tests                                                                                                                                         | _      |

|   |                 | 4.4.2  | Test for Single Event Effect (SEE)                                                                                                                                       | ;      |

|   |                 |        | 4.4.2.1 SEE Test Procedure                                                                                                                                               | 7      |

| R | eference |                                                 | 92 |

|---|----------|-------------------------------------------------|----|

| 5 | Summary  | and Conclusions                                 | 90 |

|   | 4.4.3    | Summary of the irradiation tests                | 89 |

|   |          | 4.4.2.2 SEE cross sections for individual chips | 88 |

# List of Figures

| 1.1  | LHC and Injection Complex at CERN                                               |    |  |  |  |

|------|---------------------------------------------------------------------------------|----|--|--|--|

| 1.2  | Schematic layout of the LHC. Beam 1 circulates clockwise and Beam 2 Counter-    |    |  |  |  |

|      | Clockwise.                                                                      | 13 |  |  |  |

| 1.3  | Cross Section of LHC Tunnel with showing the LHC machine cross section          | 15 |  |  |  |

| 1.4  | Feynman-Diagrams for Higgs Boson Production.                                    | 18 |  |  |  |

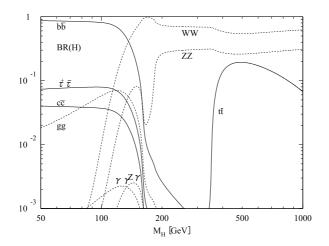

| 1.5  | Decay branching fraction of StandardModelHiggs.                                 | 18 |  |  |  |

| 1.6  | The ATLAS detector overview.                                                    | 20 |  |  |  |

| 1.7  | Inner Detector.                                                                 | 21 |  |  |  |

| 1.8  | Layout of the Calorimeters.                                                     | 22 |  |  |  |

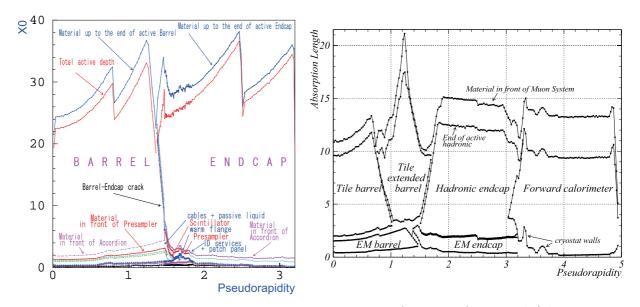

| 1.9  | Total thickness (in radiation length) of the ATLAS EM calorimeter as a function |    |  |  |  |

|      | of $\eta$ .                                                                     | 22 |  |  |  |

| 1.10 | Amount of material (absorption length) in the ATLAS Calorimetry as a function   |    |  |  |  |

|      | of $\eta$ .                                                                     | 22 |  |  |  |

| 1.11 | R-Z View of the ATLAS Muon Spectrometer                                         | 24 |  |  |  |

| 1.12 | The MDT (Monitored Drift Tube)                                                  | 24 |  |  |  |

| 1.13 | The CSC (Cathode Strip Tube).                                                   | 25 |  |  |  |

| 1.14 | The RPC (Resistive Plate Chamber)                                               | 25 |  |  |  |

| 1.15 | TGC structure showing anode wires, graphite cathodes, G-10 layers, and read-    |    |  |  |  |

|      | out strip orthogonal to the wires                                               | 26 |  |  |  |

| 1.16 | Cross-section of a triplet (left) and of a doublet of TGCs (right). $\ldots$ .  | 27 |  |  |  |

| 2.1  | Schematic diagram of the ATLAS Trigger and DAQ System.                          | 29 |  |  |  |

| 2.2  | ATLAS LVL1 Trigger System                                                       | 30 |  |  |  |

| 2.3  | Layout of the ATLAS Muon Trigger Chambers                                       | 31 |  |  |  |

| 3.1  | The Longitudinal view of the TGC system.                                        | 33 |  |  |  |

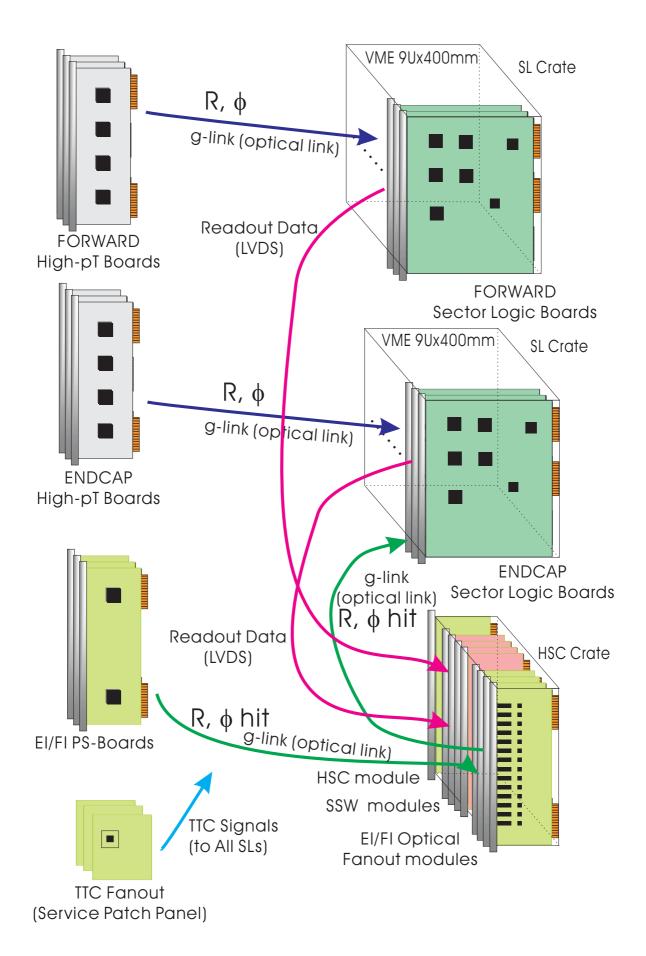

| 3.2  | Overview of the TGC LVL1 Trigger electronics system.                            | 35 |  |  |  |

| 3.3  | TGC electronics placement.                                                      | 37 |  |  |  |

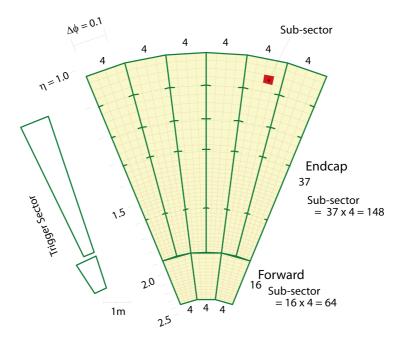

| 3.4  | TGC LVL1 Trigger segmentation for an octant (one eights of pivot plane). One                                 |    |

|------|--------------------------------------------------------------------------------------------------------------|----|

|      | octant wheel is divided into six ENDCAP sectors and three FORWARD sectors.                                   |    |

|      | Bold lines in the figure indicate individual trigger sectors. They are further                               |    |

| ~ -  | subdivided into trigger subsectors.                                                                          | 38 |

| 3.5  | Wire-signal segmentation. Each small box represents a segment of 32 channels,                                |    |

|      | corresponding to 4 subsectors                                                                                | 39 |

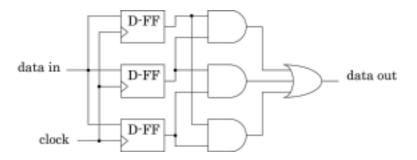

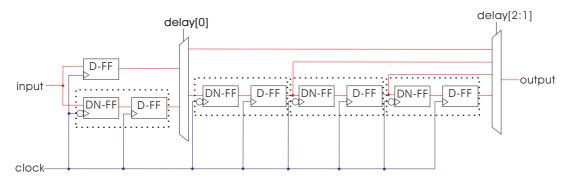

| 4.1  | Voting Logic implementation: Three D-type FlipFlops are used to implement                                    |    |

|      | 1bit Voting Register. Even if any one register value flipped, the data out keeps                             |    |

|      | the initial value.                                                                                           | 41 |

| 4.2  | Device selection at the TGC electronics system                                                               | 42 |

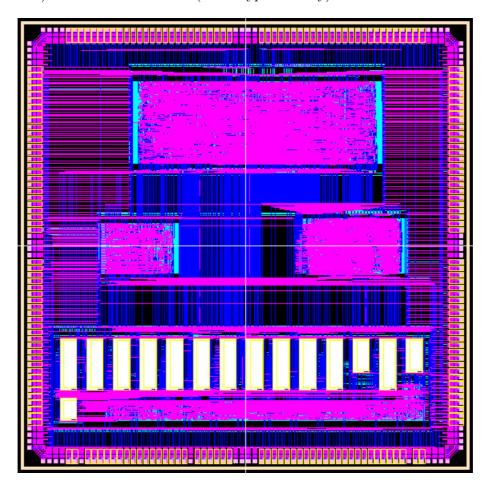

| 4.3  | Layout Mask pattern of SLB ASIC Version 6. This version is final design and                                  |    |

|      | mass-production has done with this design. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$    | 43 |

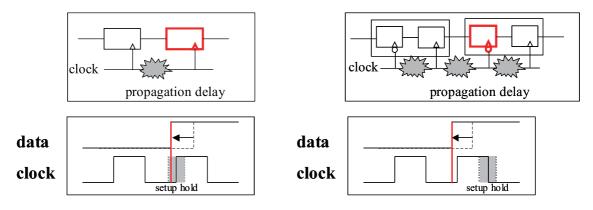

| 4.4  | Normal Shift Register.                                                                                       | 44 |

| 4.5  | Master-Slave Shift Register                                                                                  | 44 |

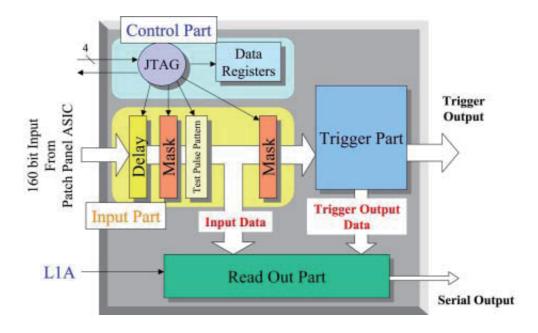

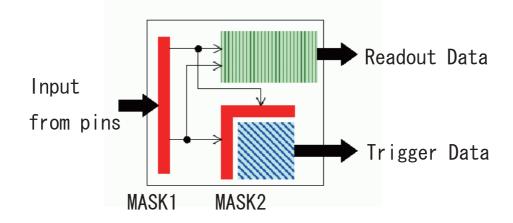

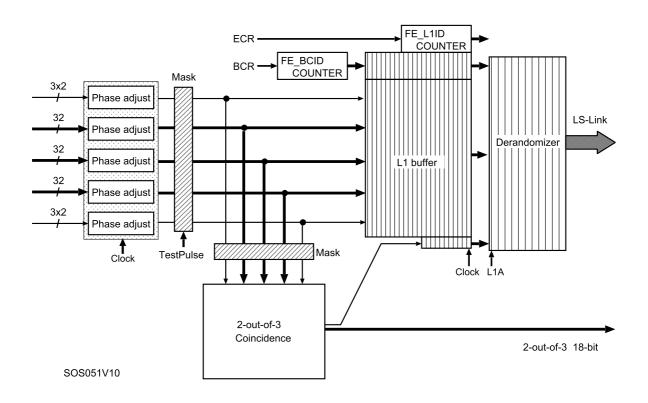

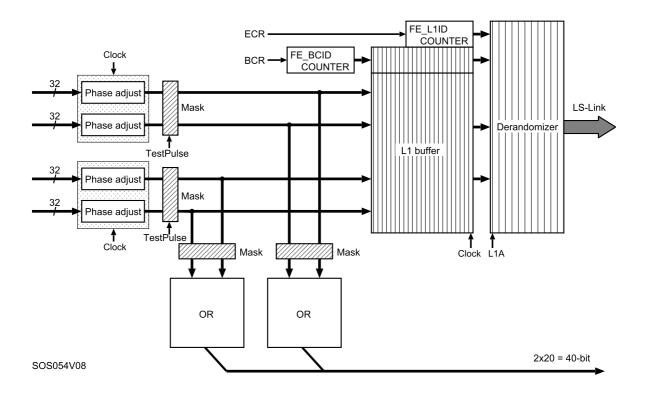

| 4.6  | Block Diagram of the SLB ASIC                                                                                | 45 |

| 4.7  | Double mask scheme implemented in the SLB ASIC, two masks are shown in                                       |    |

|      | the (red) solid squares. One is common for the Readout and the Matrix, and                                   |    |

|      | the other one is only for the trigger matrix. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 46 |

| 4.8  | Schematic of Delay Circuit of SLB ASIC Input block. At first, the input signal                               |    |

|      | is latched either on Positive edge (D-FF) or Negative edge (DN-FF). Following                                |    |

|      | delay shift register circuit is formed by the Master-Slave structure                                         | 46 |

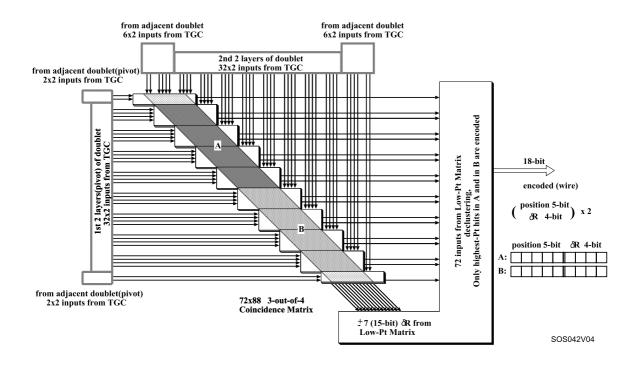

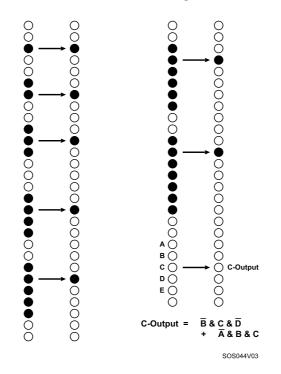

| 4.9  | The functional structure of a Slave Board for the TGC doublet pairs. Shown is                                |    |

|      | the wire Slave Board; the strip Slave Board has 16-bit output instead. $\ldots$ .                            | 47 |

| 4.10 | Structure of a 3-out-of-4 Doublet Slave Board Low- $p_T$ matrix and the encoded                              |    |

|      | output information. The wire (r) Slave Board is shown. The strip Doublet Slave                               |    |

|      | Board is similar, but with $\Delta \phi = \pm 3$                                                             | 48 |

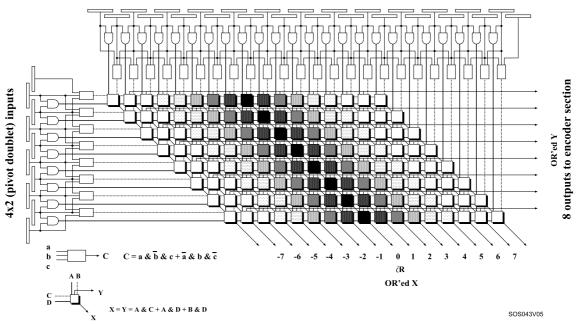

| 4.11 | Detailed structure of the 3-out-of-4 Low- $p_T$ matrix for wires. Also shown is the                          |    |

|      | function of a matrix element. Cells with the same shading have the same $\Delta r$ .                         |    |

|      | The matrix for $\phi$ is the same, except $\Delta\phi$ goes from -3 to +3. (Actually X and                   |    |

|      | Y in the figure are the same.) $\ldots$                                                                      | 49 |

| 4.12 | Declustering rules. When a hit pattern wider than two is found, the rules shown                              |    |

|      | assign a position to the track                                                                               | 50 |

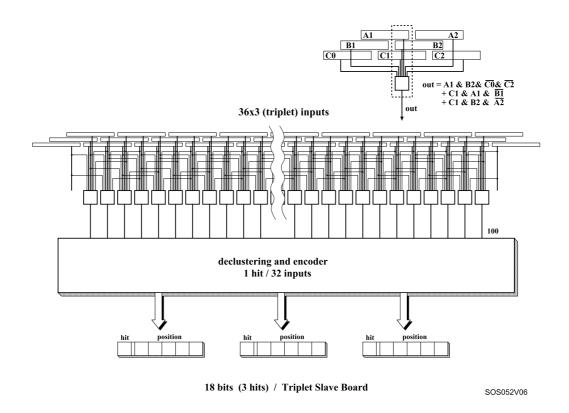

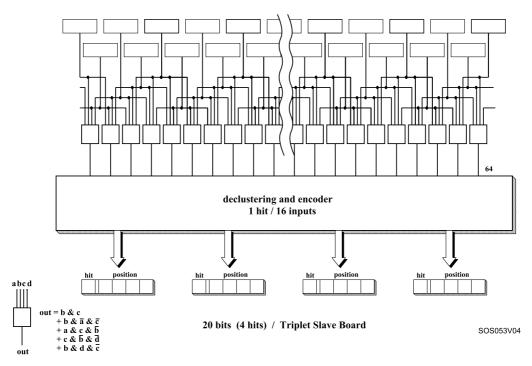

| 4.13 | Slave Board for TGC Triplets (for wire signals)                                                              | 51 |

| 4.14 | Structure of the Triplet logic for wire signals. Logic to deal with the staggering                           |    |

|      | of triplet layers and the output format after encoding is also shown                                         | 51 |

| 4.15 | Functional structure of a Slave Board for TGC Triplet strip signals. There are                 |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | only two active layers of strips per "triplet". One chip handles up to two triplet             |    |

|      | units independently.                                                                           | 52 |

| 4.16 | The functional structure of the triplet Slave Board for strip signals. Logic to                |    |

|      | deal with the staggering of triplet layers and output format after the encoder                 |    |

|      | section is also shown.                                                                         | 53 |

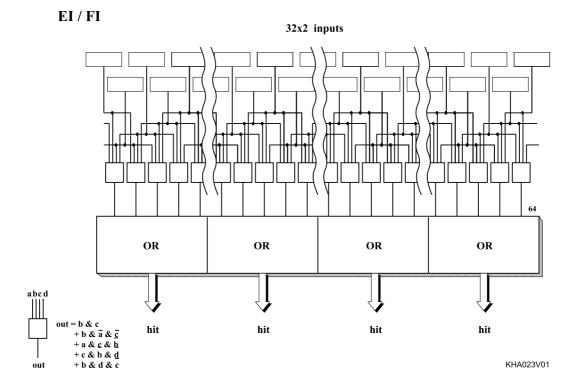

| 4.17 | Slave Board for the EI/FI TGC doublet                                                          | 54 |

| 4.18 | The functional structure of the EI/FI Slave Board. Logic to deal with the                      |    |

|      | staggering of doublet layers and output format after the encoder section is also               |    |

|      | shown                                                                                          | 54 |

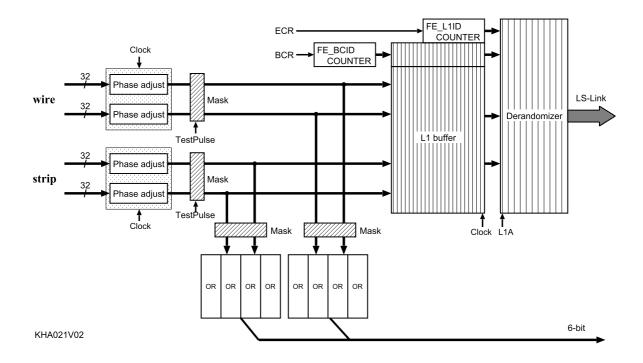

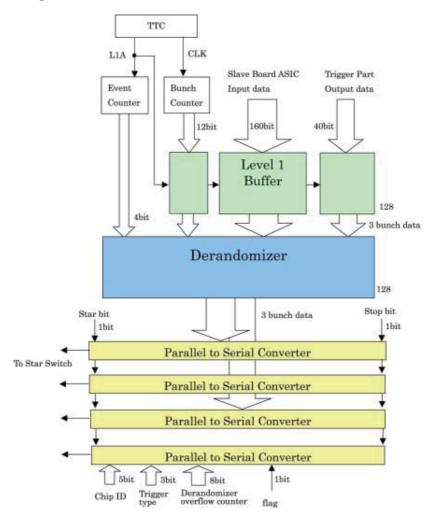

| 4.19 | Block Diagram of the SLB Readout Block                                                         | 55 |

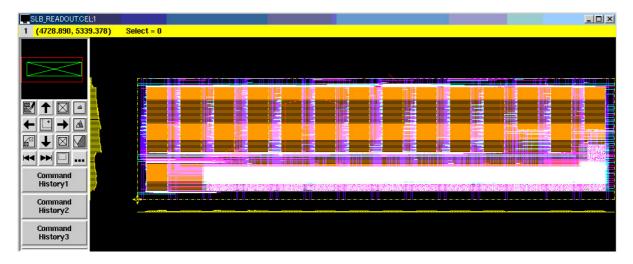

| 4.20 | Layout of the Readout macro-core. In this figure, alligned rectangles means the                |    |

|      | location of the memory macro cells.                                                            | 56 |

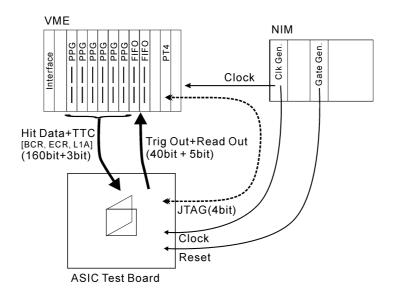

| 4.21 | A Schematic View of SLB ASIC Test Setup                                                        | 59 |

| 4.22 | Various SLB Test Vectors and Results                                                           | 60 |

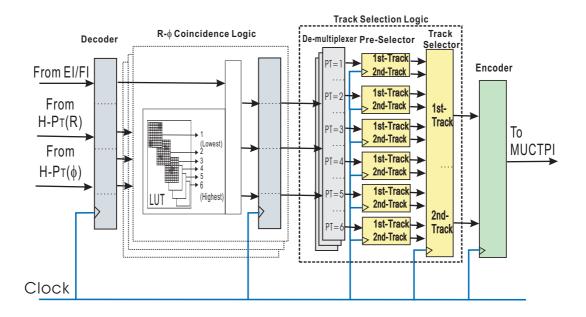

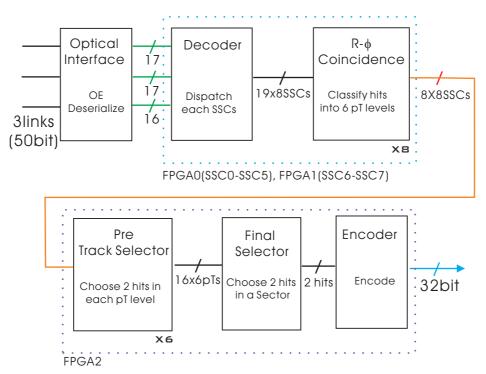

| 4.23 | Block Diagram of Sector Logic (trigger logic functional view)                                  | 62 |

| 4.24 | Detail of Sub Sector Cluster (SSC) for the R- $\phi$ coincidence to<br>gher with hit inputs.   | 63 |

| 4.25 | A schematic of Track Selection logic block.                                                    | 64 |

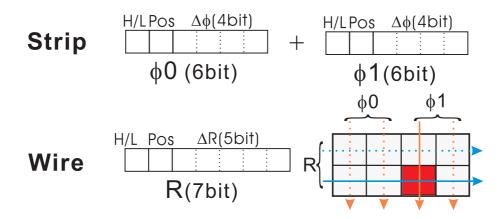

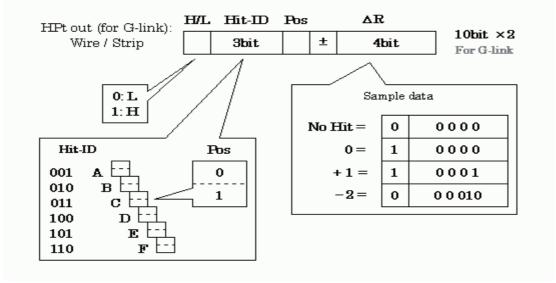

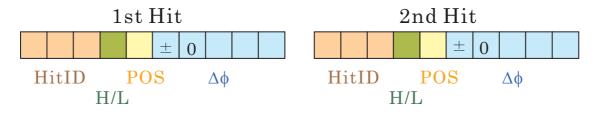

| 4.26 | Data Format from Hi-p <sub>T</sub> ASIC chip (Wire mode). $\ldots \ldots \ldots \ldots \ldots$ | 64 |

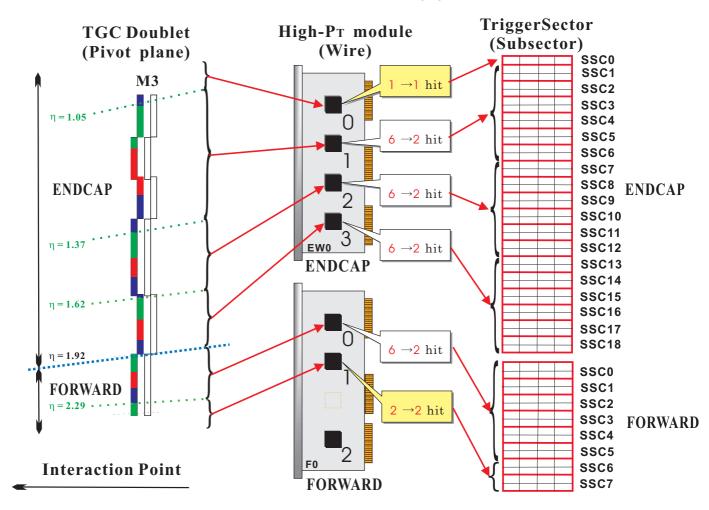

| 4.27 | Wire High- $p_T$ Boards coverage and its correspondant SSCs                                    | 65 |

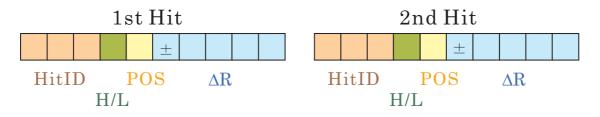

| 4.28 | Wire (R) input signal from from Wire High- $p_T$ Board                                         | 66 |

| 4.29 | Strip $(\phi)$ input signal from from Strip High-p <sub>T</sub> Board                          | 67 |

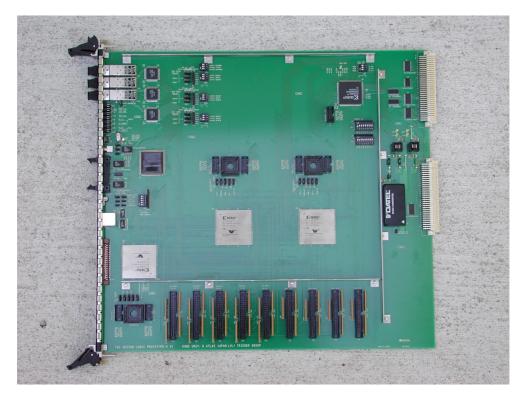

| 4.30 | A Photograph of TGC Sector Logic Prototype-0 (top view)                                        | 72 |

| 4.31 | Block Diagram of Sector Logic Prototype-0 (FORWARD Region type)                                | 73 |

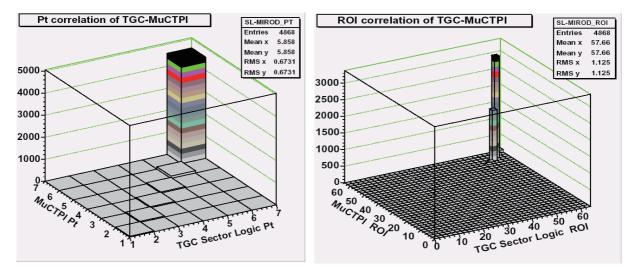

| 4.32 | Correlation plots of $p_T$ levels (left) and ROI location(right) for trigger words             |    |

|      | read out by Sector Logic vs MUCTPI.                                                            | 75 |

| 4.33 | The Sector Logic system.                                                                       | 76 |

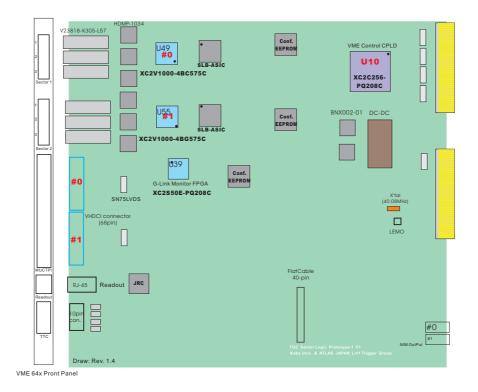

| 4.34 | The layout of TGC FORWARD Sector Logic (top view)                                              | 79 |

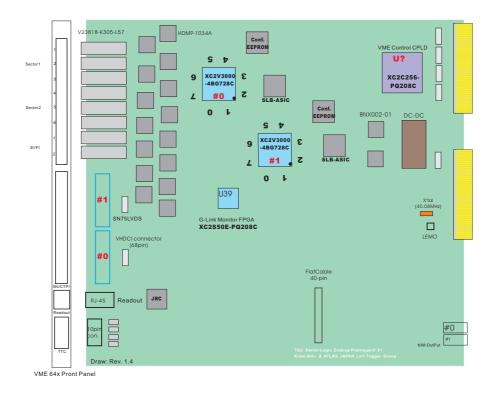

| 4.35 | The layout of TGC ENDCAP Sector Logic (top view)                                               | 79 |

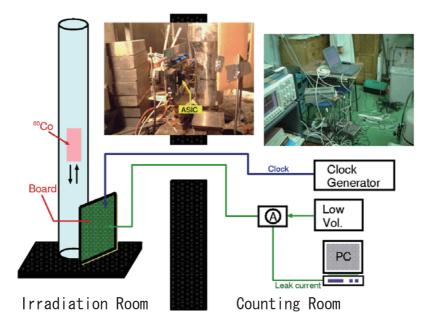

| 4.36 | $\gamma$ -ray irradiation test setup                                                           | 81 |

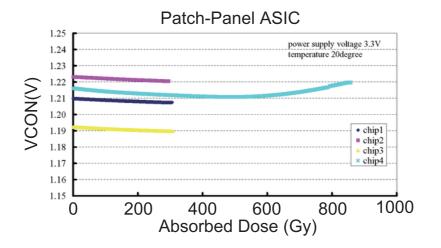

| 4.37 | VCON voltages of PP ASIC for $\gamma$ -ray irradiation                                         | 82 |

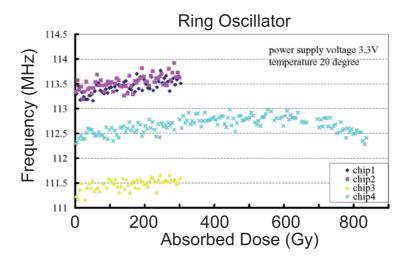

| 4.38 | Frequencies of Ring Oscillator on Rohm 0.35 $\mu m$ for $\gamma$ -ray irradiation              | 82 |

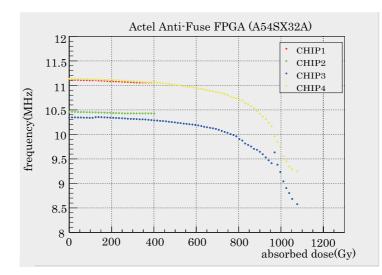

| 4.39 | Consumption current of A54SX32A for $\gamma$ -ray irradiation.                                 | 84 |

| 4.40 | Frequencies of Ring Oscillator on A54SX32A for $\gamma$ -ray irradiation                       | 84 |

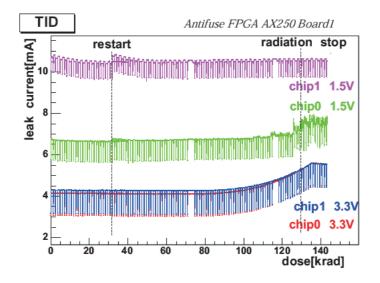

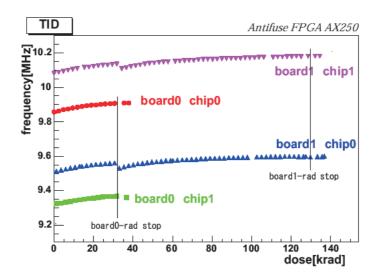

| 4.41 | Consumption current of AX250 for $\gamma$ -ray irradiation. (1 krad = 10 Gy)                   | 85 |

| 4.42 | Frequencies of Ring Oscillator on AX250 for $\gamma$ -ray irradiation. (1 krad = 10 Gy)        | 85 |

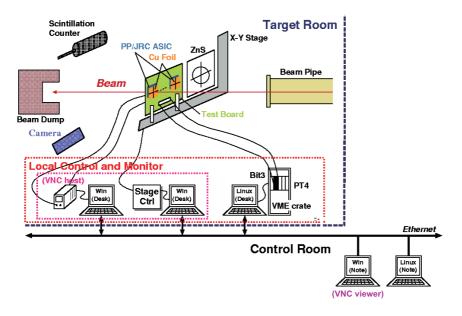

| 4.43 | Schematic of proton beam test setup                                                            | 87 |

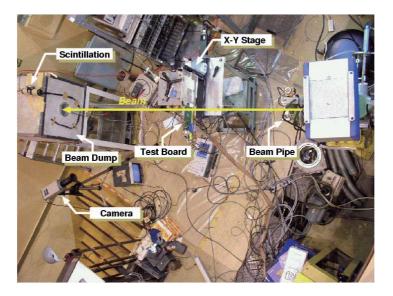

| 4.44 | Picture of proton beam test setup.                                                             | 88 |

# List of Tables

| 1.1 | Parameters of the LHC.                                                                                                                                                                                         | 14 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Main Parameters of the dipole magnet                                                                                                                                                                           | 14 |

| 1.3 | Fundamental Forces and their Bosons.                                                                                                                                                                           | 16 |

| 3.1 | contributions to the total estimated TGC latency, in bunch-crossing in number of bunch crossing. (BC) $(1 \text{ BC} = 25 \text{ ns}) \dots \dots$ | 39 |

| 4.1 | Control Registers in SLB ASIC                                                                                                                                                                                  | 57 |

| 4.2 | Data format between Sector Logic and MUCTPI [16]                                                                                                                                                               | 70 |

| 4.3 | Compilation of the SEE test results.                                                                                                                                                                           | 89 |

## Chapter 0

## Introduction

The Standard Model (SM) is a very successful model in describing interactions of the matter components, applicable to very small scale and high energies. Past experiments, performed with the Large Electron Positron collider (LEP), have confirmed the validity of the SM up to the energy of about 200 GeV. However, there still are questions to be answered in the SM framework such as the existence of the Higgs boson. The next generation collider, where protons are chosen as the beam particles, is now being built in the LEP tunnel at CERN. Since the synchrotron radiation is not a serious problem for proton beams at this energy level, the collider, named as "the Large Hadron Collider" (LHC), can accelerate the beams up to 7 TeV. The collider offers a large range of physics opportunities and provides the potential to make tests of the model with the highest energy and to search for signature of physics beyond the Standard Model.

Since most of the physics questions involve interactions that has very low cross section, not only the high energy but also the highest possible luminosity is required. The LHC will reach a luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, with inter-bunch crossing time of 25 ns and more than ~  $10^9$  interactions per second are expected.

ATLAS Experiment is one of the general purpose experiments scheduled to start taking data at the LHC in 2007. A lot of work is currently underway to complete the ATLAS detector system. In addition, detailed simulation works are performed in order to estimate the sensitivity of the ATLAS Experiment to various interesting physics processes. This thesis is devoted to developments and studies of electronics systems mostly for the Level-1 Trigger of the ATLAS Experiment.

The ATLAS Trigger and data-acquisition system is an essential part to reduce the data from the initial interaction rate  $\sim 10^9$  Hz to  $\sim 200$  Hz for the permanent storage. Since this requires an overall rejection factor of  $10^7$  against "minimum-bias" or QCD processes, an extremely excellent trigger system, essential for rare new physics such as Higgs boson decays, is required. This requirement is by far the most difficult one compared with any other experiments in the past. There are many technical difficulties needed to be overcome in producing the ATLAS Trigger system. The Level-1 (LVL1) Trigger system locates at the front-end part of the ATLAS Trigger system and must be operated in synchronous with 40.08 MHz LHC clock. The LVL1 Trigger makes an initial selection to reduce the rate into 100 kHz, based on reduced-granularity information from the calorimeters and muon detectors.

An essential requirement on the LVL1 Trigger is that it should uniquely identify the bunch crossing of the interest event(s) occured. Given the short bunch crossing interval, this is a non-trivial consideration. In the case of the muon Trigger, the physical size of the muon spectrometer implies times-of-flight comparable to the bunch crossing period.

It is also important to keep the latency (time taken to form and distribute the trigger decision) to a minimum. During this waiting time all signals in detector channels has to be retained in "pipeline" memories. These memories are generally contained in custom integrated circuits, placed on or close to the detector, usually in inaccessible area and under a high-radiation environment. For reasons of cost and reliability, it is desirable to keep the pipeline lengths as short as possible. The LVL1 latency, measured from the time of the proton-proton collision until the trigger decision is made available to the front-end electronics, is required to be less than 2.5  $\mu$ s. In order to achieve this, the LVL1 Trigger is implemented as a system of dedicated hardware processors.

For today's electronics, the system clock of 40.08 MHz is relatively slow. Many CPUs operates over a GHz. This high frequency operation is achieved not only by the latest device technologies but also by the long length pipeline architecture, where each step in the pipeline has minimized logics. (i.e. This aims lowest latency in each step.) This is a straightforward way to achieve the high performance in the viewpoint of data throughput.<sup>1</sup>

On the other hand, the LVL1 Trigger system is required to minimize the latency.<sup>2</sup> In addition, due to the trigger logic of our system needs to cover large geometrical area of which signals are correlated each other, one unit trigger logic has large number of input channels. From the viewpoint of implementation, each step of the pipeline should process these signals all together, so that breakdown of these processes into smaller steps might be limited. Therefore, we have to implement large-scale logics into steps synchronized with the system clock of 40.08 MHz with sufficient timing margin. To meet this requirement, technical challenges were needed to develop the logic design.

The author made efforts to finalize the one of front-end core components implementing Application Specific Integrated Circuit (ASIC), named Slave Board (SLB) ASIC, which makes both trigger decisions and data read out by using "pipeline" memories. The ASIC is manufactured with a full custom 0.35  $\mu$ m CMOS technology in 9.86 mm × 9.86 mm die size. The ASIC has over 2×10<sup>5</sup> gates. To equip enough performance and reliability, various techniques were developed in both logic implementations and gate layouting in the die.

<sup>&</sup>lt;sup>1</sup>Throughput is the amount of data processed in a unit time.

<sup>&</sup>lt;sup>2</sup>In general, latency and throughput are in the relation of tradeoff.

The Sector Logic, which is the final part of the Endcap muon Trigger system, combines two-dimensional muon track information and finds muons with high transverse momentum. From the physics requirements, the Sector Logic should have wide flexibility of muon selection criteria of changing  $p_T$  threshold at any value. The author has developed the Sector Logic by using Field Programmable Gate Array (FPGA) devices with Look-Up Table (LUT) method.

From the viewpoint of minimization of latency for the LVL1 Trigger system, many components are needed to install near the detector as far as possible, where the radiation level is considerable high. Devices robust against such a hard radiation environment of ten years of ATLAS Experiment were chosen for our system. Devices should not be fatally damaged against total ionization doze (TID) and should be strong against large ionization event by energetic hadrons (>20 MeV) (Single Event Effect (SEE)). In order to confirm the radiation tolerance of these devices, we have executed irradiation tests ( $\gamma$ -ray for TID effects, proton beam for SEE effects).

In this thesis, following issues are mainly discussed:

- 1. Architecture and its implementation of the Level-1 Trigger, especially Endcap muon Trigger (Thin Gap Chamber (TGC) Trigger),

- 2. Functions of Slave Board (SLB) ASIC for the Endcap muon Trigger system and its development,

- 3. Sector Logic functions and its development,

- 4. Irradiation tests for the semiconductor devices used in the system.

This thesis is organized as follows: In Chapter 1, overview of the LHC and ATLAS Experiment and its subsystem are described. In Chapter 2, the design of the ATLAS Trigger/DAQ (TDAQ) system is described. In Chapter 3, the design of the Endcap (TGC) muon Trigger system is described. Chapter 4 is the main part of this thesis and is devoted for both the discussions on (1) technology selection and radiation tolerance test, and (2) the detailed design and its specification of the components that the author developed. In Chapter 5, discussion and summary of the study are described.

### Chapter 1

# The ATLAS Experiment

#### 1.1 The Large Hadron Collider

The Large Hadron Collider (LHC) is the latest proton-proton collider being built at CERN, which will provide a center of mass energy of  $\sqrt{s} = 14$  TeV with a design luminosity of  $L = 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. The beam crossing will occur at every 25 ns and, in each crossing, about 23 interactions are expected on average. For the first three years, it will be operated with a lower luminosity of  $L = 10^{33}$  cm<sup>-2</sup>s<sup>-1</sup> (denoted as "Low-Lumi."), then the luminosity will be increased to the design value ("High-Lumi."). The details are summarized in Table 1.1. The LHC offers a wide range of physics opportunities. The primary goal of the ATLAS project is to discover the origin of particle masses at the electroweak scale. In addition, there are several important goals such as the searches for heavy W- and Z-like objects, supersymmetric particles, compositeness of the fundamental fermions, as well as the investigation of CP violation in B-decays, and detailed studies of the top quark.

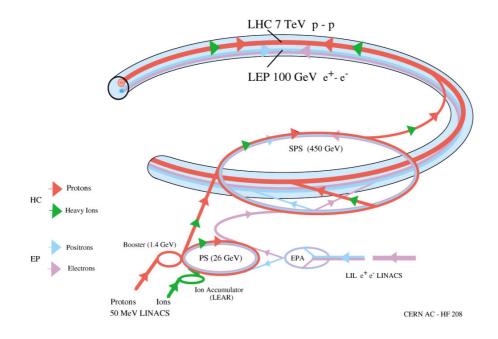

#### 1.1.1 The LHC Accelerator Complex

The LHC, whose construction was approved in 1994, will be operational in 2007. It will be accommodated in the LEP tunnel. The existing accelerator complex, which consists of the 50 MeV linac, the 1 GeV booster, the 26 GeV Proton Synchrotron (PS) and 450 GeV Super Proton Synchrotron (SPS), will be employed as the injection system for the LHC as shown in Figure 1.1. The LHC is also designed to be used for heavy ion collisions and reaches for lead ions a center of mass energy of up to  $\sqrt{s} = 1312$  TeV.

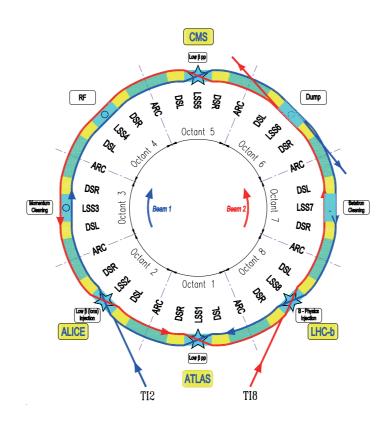

As shown in Figure 1.2, four experiments are proposed and being constructed. Two experiments (ATLAS [1] and CMS) are for general purpose, one (ALICE) for heavy ion experiment and one (LHCb) for b-physics experiment. One additional experiment (TOTEM), which hosts on CMS, is an experiment to measure the total cross section, elastic scattering and diffractive processes at the LHC.

Figure 1.1: LHC and Injection Complex at CERN.

Figure 1.2: Schematic layout of the LHC. Beam 1 circulates clockwise and Beam 2 Counter-Clockwise.

| Parameter          | Normal (High-Lumi.) | Low-Lumi.    | Ultimate     | Unit                                   |

|--------------------|---------------------|--------------|--------------|----------------------------------------|

| Circumference      | 27                  |              |              | km                                     |

| Proton Energy      | 7.0                 | <i>~</i>     | <i>~</i>     | TeV                                    |

| # of Protons/Bunch | 1.1                 | 0.17         | 1.67         | $10^{11}$                              |

| # of Bunch         | 2835                | $\leftarrow$ | $\leftarrow$ |                                        |

| Bunch Spacing      | 25                  | $\leftarrow$ | <i>~</i>     | ns                                     |

| Current            | 0.56                | 0.087        | 0.850        | А                                      |

| Trans. emittance   | 3.75                | 1.0          | 3.75         | $\mu$ rad                              |

| Beam size at IP    | 16                  | $\leftarrow$ | $\leftarrow$ | $\mu$ rad                              |

| Crossing Angle     | 300                 | $\leftarrow$ | $\leftarrow$ | $\mu$ rad                              |

| Luminosity         | 1.0                 | 0.1          | 2.3          | $10^{34} \text{cm}^{-2} \text{s}^{-1}$ |

| Life Time          | 10                  | <i>~</i>     | <i>~</i>     | Hour                                   |

| Filling Time       | 3                   | <i>~</i>     | <i>~</i>     | Min                                    |

Table 1.1: Parameters of the LHC.

Table 1.2: Main Parameters of the dipole magnet.

| Operational field                           | 8.33 T              |

|---------------------------------------------|---------------------|

| Coil Aperture at 293K                       | $56.00 \mathrm{mm}$ |

| Distance between aperture axes at 1.9K      | 194.00 mm           |

| Magnetic length at 1.9K and at normal field | 14312 mm            |

| Current at normal field                     | 11850 A             |

| Operating Temperature                       | 1.9 K               |

#### 1.1.2 The Bending (Dipole) Magnets in the LHC

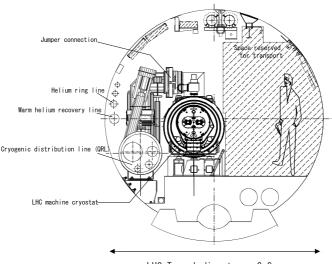

In order to realize the highest beam energy with the given ring circumference, and also considering spatial limitation of the tunnel, superconducting dipole magnets [2], made with a special technique, are employed in the LHC beam bending system. Due to the space constraint, (See Figure 1.3) the magnet has two beam pipes for counter-rotating proton beams and provides an anti-parallel magnetic field of 8.33 T for them. To realize such strong magnetic field, copperclad niobium-titanium windings are employed and they are operated under a temperature of 1.9 K with liquid helium. The parameters are summarized in Table 1.2. A total of 1,232 main dipole magnets will be installed in the ARC area, (see Figure 1.2) where the number is maximized to achieve the highest energy. The cryogenics system for the magnets will contain about 700 kl of liquid helium and have a power consumption of about 140 kW.

LHC Tunnel diameter = 3.8m

Figure 1.3: Cross Section of LHC Tunnel with showing the LHC machine cross section.

#### 1.2 Physics at the ATLAS Experiment

The ATLAS Experiment is designed to try to reveal the mechanism of electroweak symmetry breaking and to study a variety of other physics which would appear at the TeV scale. In particular, a Higgs boson, which is predicted in the Standard Model (SM), is able to be observed in various decay channels over the full range of allowed mass region, if it exists. The ATLAS Experiment can determine the Higgs mass and its couplings.

#### 1.2.1 The Standard Model

The Standard Model (SM) is a very successful description of the interactions of the components of matter at the smallest scales (<  $10^{-18}$ m) and highest energies (~ 200GeV) accessible to current experiments. It is constituted of a quantum field theory that describes the interaction of spin- $\frac{1}{2}$ , point-like fermions, whose interactions are mediated by spin-1 gauge bosons.

The fermions consist of two groups: the leptons and the quarks. The leptons interact weakly and electromagnetically (charged leptons only) and fall into three families,

$$\begin{pmatrix} e \\ \nu_e \end{pmatrix} \begin{pmatrix} \mu \\ \nu_\mu \end{pmatrix} \begin{pmatrix} \tau \\ \nu_\tau \end{pmatrix}$$

The quarks interact electromagnetically, weakly and strongly and fall into three families,

$$\begin{pmatrix} u \\ d \end{pmatrix} \begin{pmatrix} c \\ s \end{pmatrix} \begin{pmatrix} t \\ b \end{pmatrix}$$

Both the leptons and quarks have their own anti-particles. All mesons and baryons are composed of the quarks and anti-quarks.

| Forces          | Boson                      | Symbol                            | Relative Strength                         |

|-----------------|----------------------------|-----------------------------------|-------------------------------------------|

| weak            | intermediate vector bosons | $\mathrm{W}^{\pm},\mathrm{Z}^{0}$ | $\alpha_{\rm weak} = 1.02 \times 10^{-5}$ |

| electromagnetic | photon                     | $\gamma$                          | $\alpha_{\rm em} = 1/137$                 |

| strong          | gluons                     | g                                 | $\alpha_{\rm strong} \approx 0.1$         |

Table 1.3: Fundamental Forces and their Bosons.

There are three fundamental forces; the electromagnetic, weak and strong forces.<sup>1</sup> They are described by means of gauge theories and the forces are mediated by one or more boson(s). They are summarized in Table 1.3.

In order to explain the spontaneous symmetry breaking in the electroweak sector, Higgs mechanism, which provides masses to the W and Z bosons, has been introduced. The mechanism employs a spin-less particle called "the Higgs boson" in its minimal formulation. This particle can also provide the masses of all the fermions in the SM.

#### 1.2.2 Physics Potential

From an estimated non-diffractive cross-section of ~100 mb [1], an average of 23 events are expected per bunch crossing at the peak luminosity. They are mainly from QCD soft collision processes, involving small momentum transfer, with spectator quarks. The events, which are collected with the minimum-bias trigger, can be used to study the topological shapes and energy flows of the events as a test of QCD. Jet cross-sections can be also investigated over several orders of magnitude. More interesting events, such as a Higgs boson is produced, are several orders of magnitude  $(10^{-13})$  less frequent. Among the various important physics [3], the followings can be exploited in the ATLAS Experiment [1] :

• Higgs Boson:

One of the most important issues in the ATLAS Experiment is an approach to the origin of the spontaneous symmetry breaking in the electroweak sector in the SM and to understand the origin of particle masses. The LHC has a capability of the Higgs boson production for wide range of its mass (m<sub>H</sub>) from  $m_{H} \approx 80$  GeV up to  $m_{H} \approx 1$  TeV.

• Top Quark:

The LHC is a top quark factory. It produces roughly  $10^7 t\bar{t}$  pairs per year even at the moderate luminosity of  $10^{33}$  cm<sup>-2</sup>s<sup>-1</sup> (at low luminosity). The mass of the top quark can be measured with an accuracy of about  $\pm 2$ GeV at a mass of m<sub>t</sub>  $\approx 170$  GeV.

• B-Physics:

In the ATLAS Experiment, a large number of B mesons are available for the studies of the B-physics. The main purposes of the studies are precise measurements of CP violation

<sup>&</sup>lt;sup>1</sup>Gravitational force is not considered in this context.

in the b-quark system  $(B^0_d)$  and the determination of the angles of the unitary triangle derived from the unitarity of the Cabibbo-Kobayashi-Maskawa matrix. In addition, it is also possible to measure  $B_s \bar{B_s}$  mixing and to search for rare decays such as  $B \to \mu \mu$ .

• Supersymmetric particles:

Supersymmetric extensions of the SM predict a wide spectrum of new particles with masses and production rates such that at the LHC they could be discovered over a large fraction of the parameter space. Events with a high jet multiplicity and large missing energy make a search possible in the range of 1 to 4 TeV.

• Physics beyond the SM:

While the existing precision electroweak measurements are consistent with a light Higgs boson, the possibility of electroweak symmetry breaking by new strong dynamics at the TeV scale cannot be excluded. The following searches and measurements are proposed:

- Strongly interacting W's.

- Technicolor.

- Compositeness.

- New Gauge Bosons.

- Extra Dimensions.

- Anomalous Gauge-boson Couplings.

#### 1.2.3 Higgs Boson

The search for the Higgs boson is the most prominent issue for the LHC. It is used to optimize the ATLAS detector geometry and is given here as an example of the physics potential. The current limit on the Higgs mass from experiments at LEP [11] is  $m_{\rm H} > 113.5 {\rm GeV}$ .

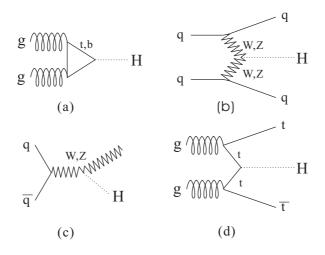

The Feynman-diagrams for Higgs boson production are shown in Figure 1.4. Over the mass range of  $80 \text{GeV} < m_H < 800 \text{GeV}$  the gluon fusion (a) is dominant. The process (b)  $qq \rightarrow qqH$  becomes dominant for higher masses up to 1 TeV.

The decay branching fraction of standard model Higgs boson is shown in Figure 1.5. The search strategy for the Higgs boson depend on its mass and several methods have to be combined to cover the full mass range:

•  $H \rightarrow b\bar{b}$ :

With a Higgs boson mass below the threshold for decays into a pair of vector bosons, this decay mode is essentially 100%. The signature used will be a lepton from one b-quark and a b-quark jet from the other, possibly used with the associated production (Figure 1.4 (c) and (d)). This channel is sensitive at  $80 \text{GeV} < m_{\text{H}} < 100 \text{GeV}$ .

Figure 1.4: Feynman-Diagrams for Higgs Boson Production.

Figure 1.5: Decay branching fraction of StandardModelHiggs.

•  $H \rightarrow \gamma \gamma$  :

This is a sensitive channel for  $90 \text{GeV} < m_H < 150 \text{GeV}$  and requires an excellent electromagnetic calorimeter and identification of photons against a huge background from jets misidentified as photons.

•  $H \to ZZ^{(*)} \to 4l^{\pm}$ :

For masses between  $130 \text{GeV} < m_H < 2m_Z$ , one of the Z bosons is virtual and the Higgs boson is rather narrow with a large background from boson pair production. For masses  $m_H > 2m_Z$ , both bosons are real and the signal is rather clean.

•  $H \to WW$ ,  $ZZ \to l^{\pm}\nu jj$ ,  $2l^{\pm}jj$ :

These signatures are important in the mass range up to  $m_H \approx 1 \text{TeV}$  and uses two jets for identification.

#### 1.3 The ATLAS Detector

ATLAS [3] is a general-purpose proton-proton collider detector, which is being constructed for LHC. It is designed to exploit the full discovery potential of the LHC. At the high luminosity, integrated luminosity amounts  $100 \text{fb}^{-1}$  per year. Detectors and front-end electronics are firmly required to be radiation tolerance for these high luminosities. <sup>2</sup> Furthermore, bunches of proton are separated by only 25 ns, then high speed operations and low dead time of response are strongly demanded on the detectors. In particular, the very first section of the ATLAS Trigger system (LVL1 Trigger) is required to have low latency and no dead-time for its operation, which will be discussed in the Chapter 2.

#### 1.3.1 Overview

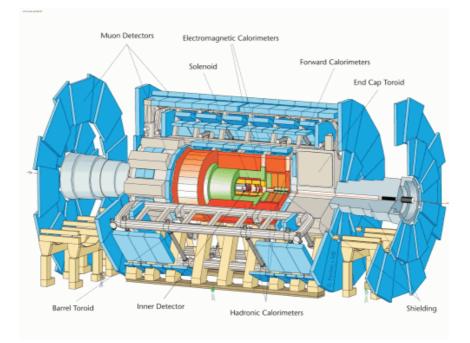

The ATLAS detector is illustrated in Figure 1.6, and it measures 22 m high, 44 m long, and weighs 7,000 tons. The characteristics of the ATLAS detector are summarized as follows:

- Precision inner tracking system (denoted as "Inner Detector") is constituted with pixel, strip of silicon, and TRT with 2 T solenoidal magnet. Good performance is expected on the *B*-tagging and the γ-conversion tagging.

- A very good electromagnetic calorimeter is mounted to identify and measure electrons and photons.

- $4\pi$ -covered hadronic calorimeter for hermetic jet measurement and missing transverse energy.

- A stand-alone muon spectrometer with toroidal magnets to identify muons and measure their momentum.

$<sup>^{2}</sup>$ This issue is discussed in the section 4.4.

Figure 1.6: The ATLAS detector overview.

#### 1.3.2 Inner Detector

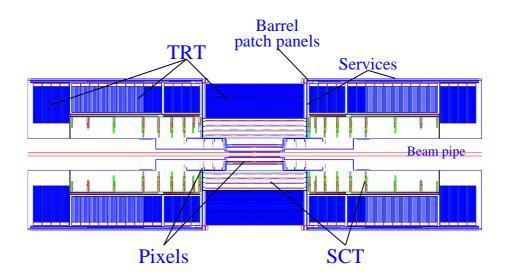

The inner detector is in an axial central field of 2 T provided by a superconducting solenoidal magnet and measures the paths of electrically charged particles. The inner detector system consists of following detectors:

- The pixel detector is based on silicon detectors which contain an array of pixel diodes. The size of pixel is 50  $\mu$ m × 400  $\mu$ m.

- The SemiConductor Tracker (SCT) uses strip detectors with fine granularity in the  $\phi$  direction. Silicon is foreseen in the barrel region and GaAs substrates in the forward region where the radiation doses are higher.

- The Transition Radiation Tracker (TRT) is based on straw tubes of 4mm diameter. The straws are interleaved with polyethylene radiators to produce and detect X-ray emission from very relativistic particles.

#### 1.3.3 Calorimetry

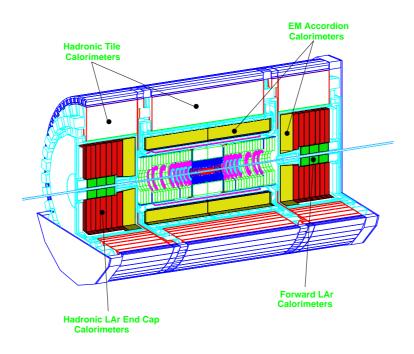

The ATLAS detector has, like most colliding-beam high-energy beam experiments, two types of calorimeters: an electromagnetic calorimeter situated directly outside of the solenoid magnet of the inner detector, and a hadronic calorimeter is surrounding the electromagnetic one. (Shown in Figure 1.8.) Accurate jet energy measurement and excellent missing energy reconstruction

Figure 1.7: Inner Detector.

requirements demand large rapidity coverage. The ATLAS calorimeters therefore extend up to  $|\eta| = 4.9.$

#### 1.3.3.1 Electromagnetic Calorimeter

The electromagnetic (EM) calorimeter is a lead-liquid argon detector with accordion-shaped Kapton electrodes and lead absorber plates over its full coverage. The accordion geometry provides complete  $\phi$  symmetry without azimuthal cracks. The lead thickness in the absorber plates has been chosen as a function of rapidity, so as to optimize the calorimeter performance in terms of energy resolution.

The total thickness of the EM calorimeter, which is shown in Figure 1.9 as a function of rapidity, is above 24 radiation length(X<sub>0</sub>) in the barrel and above 26 X<sub>0</sub> in the end-caps. The EM calorimeter is segmented into square towers of size  $\Delta \eta \times \Delta \phi = 0.025 \times 0.025$  (~ 4 × 4cm<sup>2</sup>) at  $\eta = 0$ . The electromagnetic calorimeter is designed to keep the energy resolution at the level of ~ 10%/ $\sqrt{E(GeV)}$  or below.

#### 1.3.3.2 Hadronic Calorimeter

The ATLAS hadronic calorimeter covers the range  $|\eta| < 5$  using different techniques and devices as best suited for the different requirements and radiation environment. In the range  $|\eta| < 1.6$  the iron-scintillating-tiles technique is used for the barrel and extended barrel Tile calorimeters and for partially instrumenting the crack between them with the Intermediate Tile calorimeter (ITC). This gap provides space for cables and services from the innermost detectors. In the range  $\sim 1.5 < |\eta| < 4.9$  the liquid argon calorimeter takes over: the end-cap hadronic calorimeter extends till  $|\eta| < 3.2$  while the range  $3.2 < |\eta| < 4.9$  is covered by the high-density forward calorimeter.

Figure 1.8: Layout of the Calorimeters.

Figure 1.9: Total thickness (in radiation length) Figure 1.10: Amount of material (absorption of the ATLAS EM calorimeter as a function of  $\eta$ .  $\eta$ .

The total thickness is 11 interaction lengths ( $\lambda$ ) at  $\eta = 0$ , including 1.5 $\lambda$  of the outer support, sufficient to reduce the punch-through below the irreducible level of prompt or decay muons. Figure 1.10 shows the amount material in the ATLAS calorimetry as a function of  $\eta$ (including EM calorimeter). Together with the large  $\eta$  coverage this thickness will guarantee a good  $E_{T}^{miss}$  measurement important in many physics signatures and in particular for SUSY particle searches.

The most stringent transverse granularity requirement comes from the W  $\rightarrow$  jet-jet decay at high-p<sub>T</sub> and applies for  $|\eta| < 3$  (barrel and end-cap), where a granularity  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1$ is needed. At these regions, the required energy resolution criteria are:

$$\frac{\Delta E}{E} = \frac{50\%}{\sqrt{E}} \oplus 10\%.$$

This resolution is adequate to the tasks of providing jet reconstruction and jet-jet mass reconstruction as well as missing  $p_T$  measurement for physics process of interest.

In ATLAS the forward calorimeter  $(|\eta| > 3)$  is integrated in the end-cap cryostat, with the front face at about 5 meters from the interaction point; this provides a clear benefit in terms of uniformity of coverage, reducing to the minimal possible level the effects of the crack and dead space in the transition region around  $\eta = 3.1$ , with advantages for the efficiency of forward jet tagging and for the reduction of the tails in the  $E_T^{miss}$  distribution. For this forward calorimeter, a granularity  $\Delta \eta \times \Delta \phi = 0.2 \times 0.2$  is sufficient and required energy resolution criterion is:

$$\frac{\Delta E_T}{E_T} = \frac{100\%}{\sqrt{E}} \oplus 10\%.$$

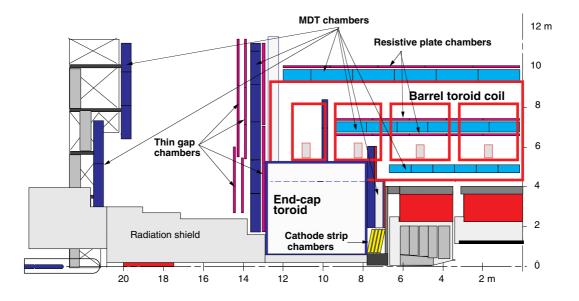

#### 1.3.4 Muon Spectrometer

The ATLAS muon spectrometer is based on a superconducting air-core toroid magnet system, producing an average magnetic field of 0.5T, which consists of a 26 m long barrel part with an inner bore of 9.4 m and an outer radius of 19.5 m and two end-caps with lengths of 5.6 m and inner bores of 1.26 m. Each toroid consists of eight flat coils symmetrically arranged around the beam axis with the end-caps rotated with respect to the barrel so that the coils interleave.

Muon chamber planes are attached to the toroids to measure the trajectories of muons. In the barrel the layout consists of three layers of chambers and in the end-caps the chambers are placed on the front and back faces of the cryostats. A third layer is fixed on the cavern wall. Two types of chambers are used for the high-precision measurements: Monitored Drift Tube chambers (MDT) and Cathode Strip Chambers (CSC).

The high-precision measurements are complemented with chambers for triggering. There are also two types used for this: Resistive Plate Chambers (RPC) and Thin Gap Chambers (TGC).

Figure 1.11: R-Z View of the ATLAS Muon Spectrometer.

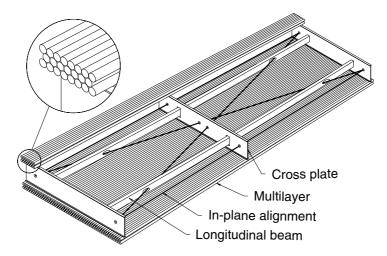

#### 1.3.4.1 Monitored Drift Tube (MDT)

The Monitored Drift Tube chamber (MDT) consists of multi-layers of drift tubes with a diameter of 30 mm as shown in Figure 1.12. The MDTs use non-flammable  $Ar(93\%)/CO_2(7\%)$  gas at 3 atm. Maximum drift time is 500 ns and position resolution is 80  $\mu$ m.

Figure 1.12: The MDT (Monitored Drift Tube).

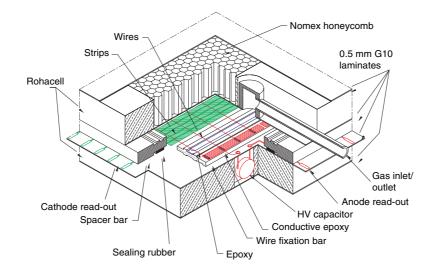

#### 1.3.4.2 Cathode Strip Chamber (CSC)

The Cathode Strip Chamber (CSC) is a multi-wire proportional chamber (MWPC) with a symmetric cell in which the anode-cathode spacing is equal to the anode wire pitch, which has been fixed at 2.54 mm. (Figure 1.13) In a CSC the precision coordinate is obtained by measuring the charge induced on the segmented cathode by the avalanche formed on the anode

wire. The CSCs can be operated in highest rate environment at large  $\eta$  using an appropriate segmentation. (cf. Figure 1.11)

Figure 1.13: The CSC (Cathode Strip Tube).

#### 1.3.4.3 Resistive Plate Chamber (PRC)

The Resistive Plate Chamber is a trigger chamber and used in the barrel region. The RPC is the gaseous parallel plate detectors with two bakelite plates coated with layers of graphite paint providing the electric field and external pick-up strips on plastic material for the signal. A set of two orthogonal strips is used to provide two-dimensional information with good spatial resolution.

Figure 1.14: The RPC (Resistive Plate Chamber).

#### 1.3.4.4 Thin Gap Chamber (TGC)

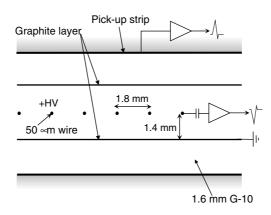

The Thin Gap Chamber (TGC) is a trigger chamber used in the end-cap region. The TGC has a structure similar to Multi-Wire Proportional Chambers (MWPCs), except that the anodeto-anode, i.e. wire-to-wire, distance is larger than the cathode-to-anode distance. Figure 1.15 shows the TGC structure. This thin gap gives shorter drift time and high time resolution. Two graphite cathodes with distance of 2.8 mm are sandwiched with 50  $\mu$ m diameter Au-coated anode wires with a pitch of 1.8 mm. The pick-up strips are formed in orthogonal direction to the wires and this gives two-dimensional information.

To match the geometric granularity to the needed momentum resolution, from 4 to 20 anode wires are grouped and these wire-groups give R coordinates. The strips are readout individually and give  $\phi$  coordinates.

With the use of a highly quenching gas mixture of  $CO_2$  and pentane  $(C_5H_{12})$ , 55% : 45%, this type of cell geometry allows operation in saturated mode. Saturated mode operation enables the operation with the hit-rate of 1 kHz/cm<sup>2</sup>, which is ten times greater than the estimated hit-rate at the ATLAS Experiment.

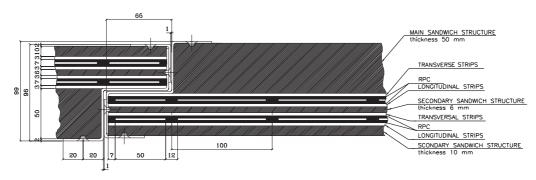

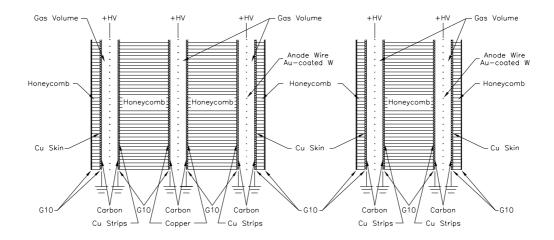

Since the TGC is too thin to satisfy the deformation requirement (maximum allowable deformation is less than 100  $\mu$ m), two or three TGCs sandwiches thick paper honeycombs. A module with two TGCs denotes doublet and three TGCs one denotes triplet.

Figure 1.16 shows the cross-sections of triplet (left) and doublet of TGCs.

Figure 1.15: TGC structure showing anode wires, graphite cathodes, G-10 layers, and read-out strip orthogonal to the wires.

Figure 1.16: Cross-section of a triplet (left) and of a doublet of TGCs (right).

### Chapter 2

# The ATLAS Trigger/Data-Acquisition (TDAQ) System

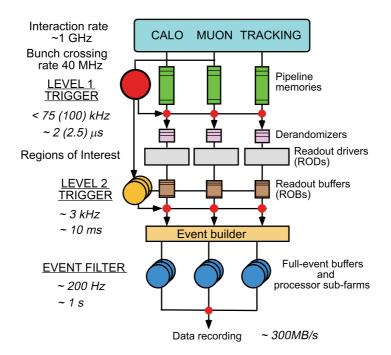

The ATLAS Trigger and Data-Acquisition (TDAQ) system is based on three levels of online event selection. Each trigger level refines the decisions made at the previous level and, where necessary, applies additional selection criteria. Starting from an initial bunch-crossing rate of 40.08 MHz (interaction rate  $\sim 10^9$  Hz at a luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>), the rate of selected events must be reduced to  $\sim 100$  Hz for permanent storage. While this requires an overall rejection factor of  $10^7$  against "minimum-bias" processes, excellent efficiency must be retained for the rare new physics, such as Higgs boson decays, that is sought in ATLAS.

Figure 2.1 shows a simplified functional view of the ATLAS TDAQ system. In the following, a brief description is given of some of key aspects of the event-selection process.

The Level-1 (LVL1) Trigger system makes an initial selection based on reduced-granularity information from the calorimeter (e,  $\gamma$ , jet,  $E_T^{\text{miss}}$ ) and muon detector( $\mu$ ). High transversemomentum (high-p<sub>T</sub>) muons are identified using only the trigger chambers [7]. The calorimeter selections are based on reduced-granularity information from all the ATLAS calorimeters (electromagnetic and hadronic; barrel, end-cap and forward) [8], [9].

The maximum rate at which the ATLAS front-end systems can accept LVL1 Trigger is limited to 75 kHz (upgradeable to 100 kHz).

An essential requirement on the LVL1 Trigger is that it should uniquely identify the bunchcrossing of interest. Given the short (25 ns) bunch-crossing interval, this is a non-trivial consideration. In the case of the muon Trigger, the physical size of the muon spectrometer implies times-of-flight comparable to the bunch-crossing period. For the calorimeter Trigger, a serious challenge is that the pulse shape of the calorimeter signals extends over many bunch crossings.

It is important to keep the latency (time taken to form and distribute the trigger decision) to a minimum. During this time period, information for all detector channels has to be retained in "pipeline" memories. These memories are generally contained in custom integrated

Figure 2.1: Schematic diagram of the ATLAS Trigger and DAQ System.

circuits, placed on or close to the detector, usually in inaccessible regions and in a high-radiation environment. The total number of detector channels, excluding the pixel detectors, exceeds  $10^7$ . For reasons of cost and reliability, it is desirable to keep the pipeline lengths as short as possible. The LVL1 latency, measured from the time of the proton-proton collision until the trigger decision is available to the front-end electronics, is required to be less than 2.5  $\mu$ s. In order to achieve this, the LVL1 Trigger is implemented as a system of purpose-built hardware processors. The target latency for the LVL1 Trigger is 2.0  $\mu$ s (leaving 500 ns contingency).

Events selected by LVL1 are read out from the front-end electronics systems of the detectors and put into readout buffers (ROBs). A large number of front-end electronics channels are multiplexed into each ROB. Intermediate buffers, labeled "derandomizer" in Figure 2.1, average out the high instantaneous data rate at the output of the pipeline memories to match the available input bandwidth of the readout drivers (RODs).

All of the data for the selected bunch crossing from all of the detectors are held in the ROBs either until the event is rejected by the Level-2 (LVL2) Trigger (in which case the data are discarded) or, in case the event is accepted by LVL2, until the data have been successfully transferred by the DAQ system to storage associated with the Event Filter (which makes the third level of event selection). The process of moving data from the ROBs to the Event Filter (EF) is called event building. Whereas before event building each event is composed of many fragments, with one fragment in each ROB, after event building the full event is stored in a single memory accessible by an EF processor.

The LVL2 Trigger makes use of "region-of-interest" (RoI) information provided by the

LVL1 Trigger. This includes information on the position ( $\eta$  and  $\phi$ ) and  $p_T$  range of candidate objects (high- $p_T$  muons, electrons/photons, hadrons/taus, jets), and energy sums (missing- $E_T$ vector and scalar  $E_T$  value, where  $E_T$  is transverse energy). The RoI data are sent by LVL1 to LVL2, for all events selected by the LVL1 Trigger, using a dedicated data path. Using the RoI information, the LVL2 Trigger selectively accesses data from the ROBs, moving only the data that are required in order to make the LVL2 decision. The LVL2 Trigger has access to all of the event data, if necessary with the full precision and granularity. Thanks to this RoI mechanism, usually only a few per cent of the full event data are required. The LVL2 Triggers are required to reduce the rate to ~3 kHz. The latency of the LVL2 Trigger is variable from event to event; it is expected to be ~10 ms.

After LVL2, the last stage of selection is performed in the EF. Here the algorithms will be based on the offline code. The EF must reduce the rate to a level suitable for permanent storage ( $\sim$ 300 MB/s), currently assumed to be  $\sim$ 200 Hz for full events of size  $\sim$ 1.5 Mbyte.

#### 2.1 Level-1 (LVL1) Trigger Overview

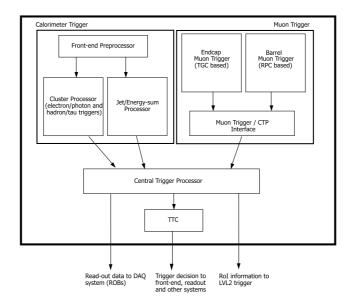

Figure 2.2: ATLAS LVL1 Trigger System.

The LVL1 Trigger is one of the most essential parts of the ATLAS Experiment for the reason that it decides whether the event is interest or not at the very early stage. As described above, the LVL2 Trigger only searches selected region by LVL1 Trigger. Therefore, if the LVL1 Trigger makes failure, there is no way to salvage significant events at any following stages.

The LVL1 Trigger system is a system of synchronous, pipelined processors running at 40.08 MHz or multiples thereof. As shown in Figure 2.2, the LVL1 Trigger system is composed of a number of building blocks: the calorimeter Trigger, the muon Trigger, the Central Trigger Processor (CTP) and the Timing, Trigger and Control (TTC) system.

In the muon Trigger, both TGC based Endcap muon Trigger subsystem and RPC based Barrel muon Trigger subsystem are operating in parallel. Each result of both muon Trigger subsystem are gathered by the Muon Trigger CTP Interface (MUCTPI) and combined data from all muon trigger chambers are sent to the CTP.

In the calorimeter Trigger, both Cluster processor and Jet/Energy processor are operating in parallel and these results are sent to CTP individually.

#### 2.1.1 Muon Trigger

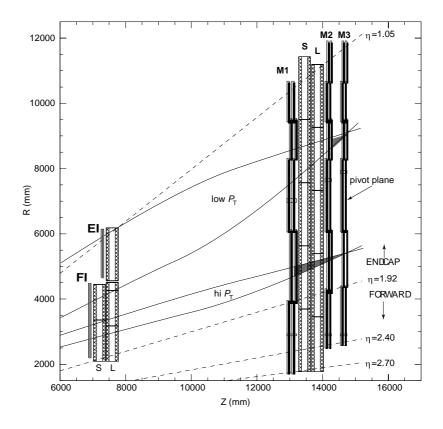

The Level-1 muon Trigger is based on dedicated, fast and finely segmented muon detectors. The layout of these trigger chambers, RPC detectors in the barrel regions and TGC detectors in the end-cap regions are shown in Figure 2.3. RPC Trigger system covers the pseudorapidity range  $|\eta| < 1.05$ , while the TGC Trigger system covers  $1.05 < |\eta| < 2.4$ . In order to prevent punch-through muons, RPC and TGC are overlapped at boundary region around  $|\eta| = 1.05$ . The double counting of muon tracks introduced by this overlap will be solved at MUCTPI.

Figure 2.3: Layout of the ATLAS Muon Trigger Chambers.

There are troidal magnets at both end-cap and barrel regions creating rotating fields in  $\phi$  direction for bending muon tracks. (These troidal magnets are shown in Figure 1.11.) These trigger chambers measure muon tracks.

As illustrated in Figure 2.3, the LVL1 muon Trigger is based on three trigger stations. Two stations are used for low- $p_T$  muon riggers (threshold range approximately 6-10 GeV), while the third station is used in addition for high- $p_T$  triggers (threshold range approximately 6-35 GeV)<sup>1</sup>. High- $p_T$  triggers are made by using the results of low- $p_T$  triggers. If high- $p_T$  trigger candidates are found, they override the corresponding low- $p_T$  trigger candidates. Each station is composed of two detector planes (with the exception of the innermost TGC station that has

<sup>&</sup>lt;sup>1</sup>For TGC, lower threshold of high-p<sub>T</sub> triggers had been extended down to 6 GeV.

three planes). Each detector plane is read out in two orthogonal projections,  $\eta$  and  $\phi$ . Both  $\eta$  and  $\phi$  trigger candidates are combined to measure the muon transverse momentum ( $p_T$ ) and two highest  $p_T$  candidates in a trigger sector are sent to MUCTPI with information of  $p_T$  value and RoI position.

#### 2.2 Timing, Trigger and Control (TTC) distribution system

The TTC system is responsible for distributing a number of signals, including the LHC clock and the LVL1 Trigger decision(LVL1 Accept (L1A)), to the front-end systems. The TTC backbone is based on the optical-broadcast system developed in the RD12 Collaboration as the LHC common system [4]. While the TTC system treat many signals, the following signals are utilized in the LVL1 Trigger system.

**BC:** The LHC clock (40.08 MHz); phase adjusted clock (denoted as "de-skewed clock") is also provided.

L1A: The LVL1 Trigger decision signal from CTP.

BCR: Bunch Counter reset signal issued by LHC machine. This signal indicates bunch-zero.

ECR: Event Counter reset signal. This signal is issued before the each run.

Test Pulse: An trigger signal to make a pseudo-hit data at each readout system.

These and other signals are encoded and transmitted optically to the front-end systems, or to intermediate points at which a change is made to detector-specific protocols for TTC distribution.

## Chapter 3

# The Endcap Muon (TGC) Trigger System

As described in Section 2.1.1, TGC provides the muon Trigger in the end-cap region. There are two sides at the ATLAS detector. All ATLAS detector layouts and connections are arranged as mirror symmetry, and there are no functional difference between both side Endcap muon Trigger electronics.

#### 3.1 Layout and its Algorithm

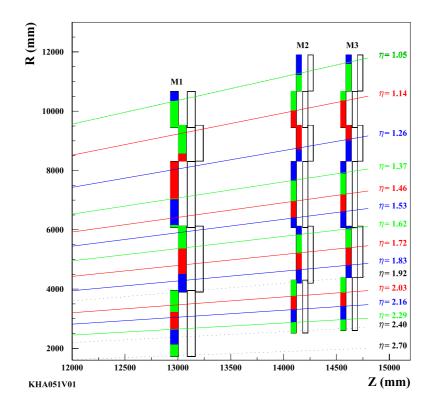

Figure 3.1: The Longitudinal view of the TGC system.

TGCs which cover end-cap region are layouted as Figure 3.1. Where EI (End-cap Inner), FI (Forward Inner), M1, M2 and M3 are the station name of TGC planes. In M1 station, triplet type TGCs are used and in M2 and M3 station, doublet type TGCs are used.(see Figure 1.16) M3 station is referred to as the pivot plane, and its chamber layout and electronics are arranged such that, to a good approximation, there are no overlaps or holes in this plane. For triggering, the TGCs cover a pseudorapidity range  $1.05 < |\eta| < 2.4$ , except for the innermost plane (EI/FI) which covers a range  $1.05 < |\eta| < 1.9$ .

Figure 3.1 also shows the LVL1 muon Trigger scheme in the end-cap region. The trigger algorithm uses pivot plane hits and extrapolates to the interaction point to construct the apparent infinite-momentum path of the track. The deviation from this path of hits found in the preceding "confirming" trigger planes is related to the track momentum. A window is constructed for each trigger region in the r and  $\phi$  directions around the infinite momentum path. A coincidence is signaled if there is a hit in the window corresponding to the hit location in the pivot plane. Independent signals are generated for R and  $\phi$ , with the wire signals determining the R-coordinate and strip signals determining  $\phi$ -coordinate. The low-p<sub>T</sub> trigger is a trigger candidate utilizes information from two doublets (M2 and M3). And the high-p<sub>T</sub> trigger is a trigger efficiency and an efficient background reduction, a 3-out-of-4 coincidence is required for the doublet pair planes of M2 and M3, for both wires and strips, a 2-out-of-3 coincidence for the triplet wire planes, and a 1-out-of-2 coincidence for the triplet strip planes is required.

Then the trigger windows are formed in  $R - \phi$  space. Using these information, muon tracks are classified into six levels of their transverse momentum ( $p_T$ ). The applied  $p_T$  threshold is determined by the size of the two-dimensional (R and  $\phi$ ) window, and for any single threshold this window is optimized to provide 90% efficiency. Tracks are flagged according to the highest threshold they cross. The final trigger decision in the end-cap system is done by merging the results of the  $R - \phi$  coincidence and the information from EI/FI chambers in order to reject tracks coming from other than the interaction point. [13]

#### **3.2** Implementation on the Electronics System

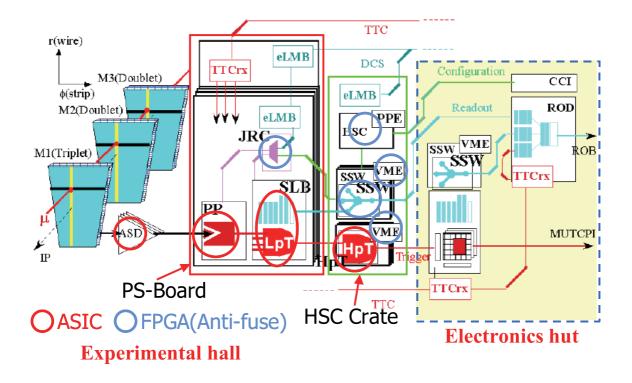

In this section, a detail description and its implementation of the Endcap muon Trigger system along with the trigger path are given. Then, overview of readout system and DCS (Detector Control System) issues are given in brief.

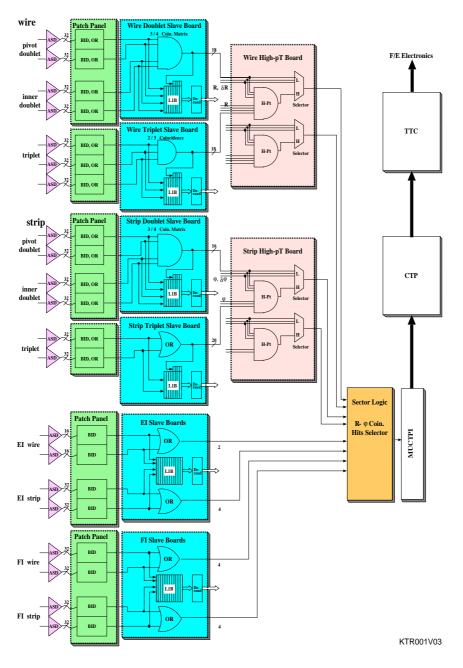

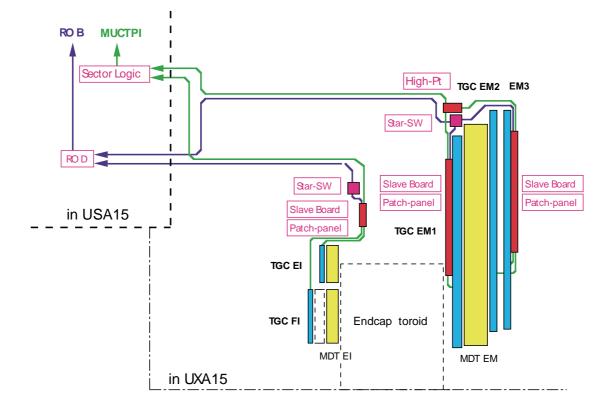

Figure 3.2 shows an overview of the TGC LVL1 Trigger electronics scheme and Figure 3.3 shows the placement of these electronics relative to the trigger chambers. The wire and strip signals emerging from the TGC are fed into a two-stage amplifier in an Amplifier Shaper Discriminator (ASD) circuit [23] [24]. Four ASD circuits are built into a single ASD chip and four ASD chips are incorporated into an ASD Board; hence each ASD Board handles 16

channels of signals. The ASD Board is physically attached to the edge of a TGC and enclosed inside the TGC electrical shielding.

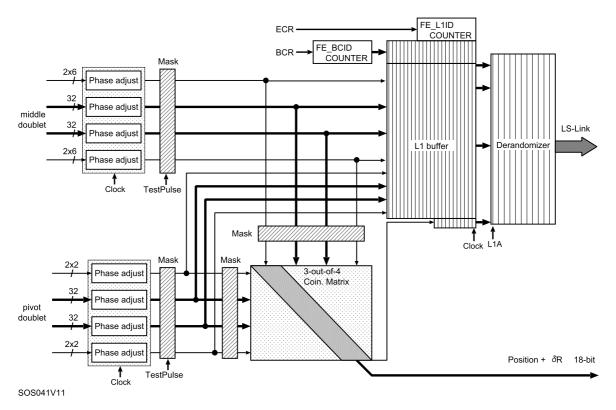

Figure 3.2: Overview of the TGC LVL1 Trigger electronics system.

Signals from the ASD Boards are sent to a PS-Board where Patch-Panel (PP) ASICs and Slave Board (SLB) ASICs are implemented. PS-Boards are placed on the accessible outer surfaces of the TGC wheels except for EI/FI PS-Boards. Thus, electronics for the two doublets are mounted on the outside of the outer doublet wheel and those for the triplets on the inner surface of the triplet wheel. The PP ASIC has 32 channels of Bunch-Crossing Identification (BCID) circuits. Outputs from PP are fed to the on-board logic to take care of physical overlap in the TGCs and fan-outs.

The processed signals are sent to corresponding SLB ASICs where the coincidence and read-out circuits are placed. There are five different types of SLB; wire and strip boards for each of the triplet and doublets and a board for the EI/FI chamber. They differ in their number of inputs, the kind of coincidence made and the maximum window width.

Information from the SLBs for the triplet and doublets is encoded to produce more compact signals and the encoded coincidence information is passed to a High- $p_T$  coincidence Board located near the outer rim of the triplet wheel. Signals from the doublet and triplet SLBs are combined here to find high- $p_T$  track candidates. Wire (R-coordinate) and strip ( $\phi$ -coordinate) information is treated separately.