PDF issue: 2024-05-28

# A Study on Memory and Digital Architectures for Low-Power Signal Processing

## Noguchi, Hiroki

```

(Degree)

博士 (工学)

(Date of Degree)

2011-03-25

(Date of Publication)

2012-01-11

(Resource Type)

doctoral thesis

(Report Number)

甲5251

(URL)

https://hdl.handle.net/20.500.14094/D1005251

```

※ 当コンテンツは神戸大学の学術成果です。無断複製・不正使用等を禁じます。著作権法で認められている範囲内で、適切にご利用ください。

#### **Doctoral Dissertation**

# A Study on Memory and Digital Architectures for Low-Power Signal Processing

(低消費電力信号処理のためのメモリと デジタルアーキテクチャに関する研究)

January 2011

Graduate School of Engineering

Kobe University

Hiroki Noguchi

#### **Abstract**

In this dissertation, low-power techniques of memory and digital architecture are presented for wearable and ubiquitous signal-processing applications. First, the background of this research area and objective of this study are described. In the second part, critical issues related to hardware implementation for low-power signal processing system are explained in the second part. The main issues of an advanced architecture and memory designs can be regarded as four limitations of memory bandwidth, power dissipation, standby electricity, and low-voltage operation. An explanation of each limitation is provided to enhance comprehension of the study objective.

In the third part, the low-power two-port SRAM design technique against process variation is discussed for low-power CMOS technology. The signal-processing demand for memory IP blocks as not only single-port SRAM but also dual-port SRAM to perform parallel operations. Multi-port SRAM is effective to reduce the total cycle times because of its parallel access mechanism. A conventional 8T SRAM comprises a precharge circuit and keeper circuit, and these circuits restrict low-voltage operation and operation frequency. To reduce the active power of the SRAM bitline, the non-precharge structure and novel cell topology are proposed. Two pMOS transistors are added to the conventional 8T memory cell, which creates the combination of the conventional 6T memory cell, an inverter, and a transmission gate. It is not necessary to prepare a precharge circuit because the inverter can independently charge and discharge the local read bitline. In the proposed SRAM, the precharge power on bitlines is eliminated and readout power is consumed only when the readout datum is changed. Measurement results verified that, at an operating frequency of 120 MHz, the proposed 64-kb video memory in a 90-nm process operates properly at 0.77 V, whereas the conventional SRAM does not function below 0.85 V. Those results demonstrate that the proposed SRAM achieves an 85% power saving on the read bitline, when regarded as an H.264 reconstructed image memory. We also examine dual-port SRAM design in terms of its area, speed, and readout power in a 45-nm process technology. Although the 8T SRAM has the lowest transistor count, and although it is the most area-efficient, the readout power consumption is high and the cycle time is notably increased because of peripheral circuits. The 10T differential-port SRAM would operate fastest if the differential

voltage were set to 50 mV. The 10T SRAM with a single-end read port consumes the least power.

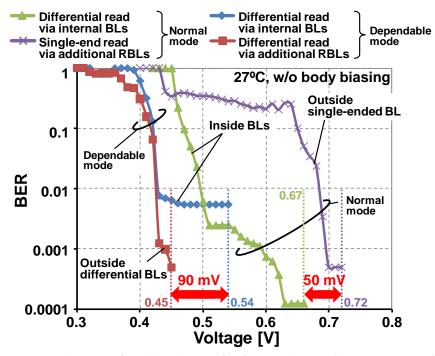

The fourth part of this paper introduces low-voltage-operatable two-port SRAM design for dynamic voltage and frequency scaling (DVFS) techniques. The 7T/14T SRAM has been proposed to enhance SRAM dependability: two pMOS transistors are added between internal nodes in a pair of the conventional 6T bitcells. In this chapter, by adding a dedicated read port, we propose a 9T/18T dual-port SRAM that is presented. The additional read port is disturb-free. It can therefore operate at a lower voltage than the 7T/14T SRAM can. Moreover, the proposed SRAM has a 9T normal mode and 18T dependable mode. To achieve the 9T/18T SRAM architecture, an interleaved bitline scheme is incorporated for the dedicated read port. The 9T/18T dual-port SRAM can scale its speed, operating voltage, and power dynamically by combining two bitcells for one-bit information. We designed and fabricated the proposed SRAM using a 65-nm process. The measurement results show that the 18T dependable read mode can reduce the operation voltage to 0.45 V at a frequency of 1 MHz because of the disturb-free read port, although the dependable 14T SRAM demands 0.54 V at the same frequency.

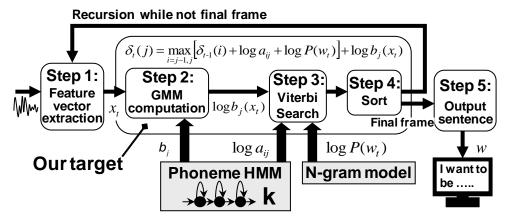

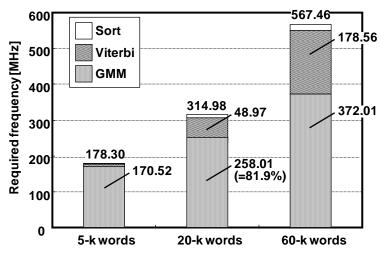

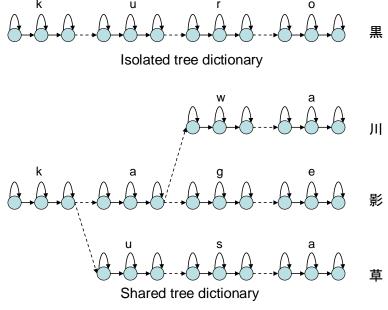

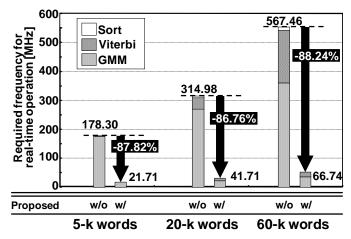

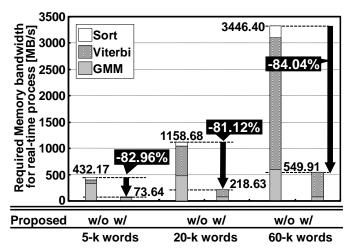

The fifth part of this paper describes one low-power wearable digital signal processing architecture, memory-bandwidth reduction techniques for large-vocabulary real-time continuous speech recognition (LVRCS), which are critically dependent upon the bus frequency on VLSI. In the conventional speech recognition architecture, the memory bandwidth is an important issue for increasing the vocabulary. In the proposed architecture, parallel computing using speech signal correlation contributes to reduction of the memory bandwidth on a Gaussian Mixture Model setup. Two-stage language model search and specialized cache were also introduced for Viterbi processing to reduce the memory bandwidth. The two-stage language model search also reduces the computing amounts. The pipelining architecture is demonstrated for reducing the required frequency for real-time operations. An evaluation result obtained using hardware description language (HDL) and a verilog simulator shows the effectively reduced memory bandwidth and required frequency obtained when using the proposed techniques. For 60-k-word speech recognition, the required frequency can be reduced to 66.74 MHz. The required memory bandwidth can be reduced to 549.91 MB/s for real-time recognition, although the speech-recognition accuracy is maintained at 86.42%.

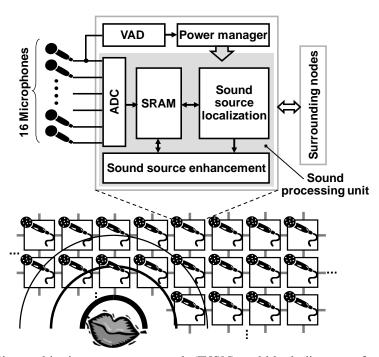

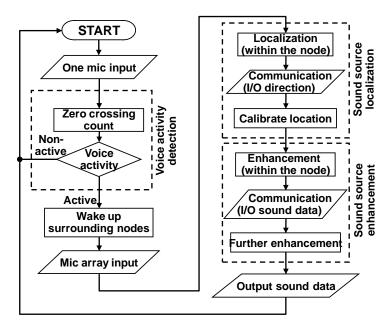

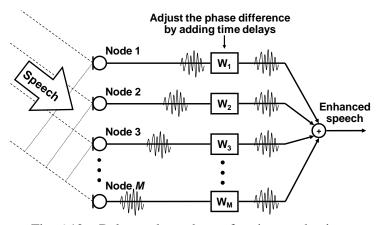

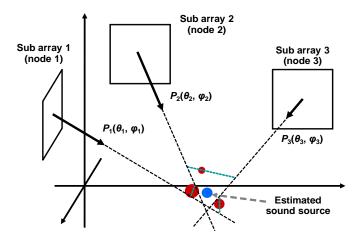

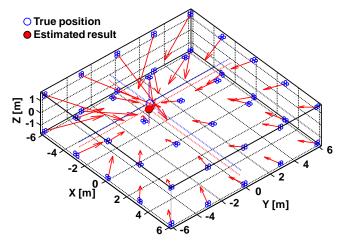

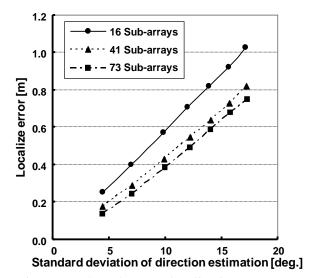

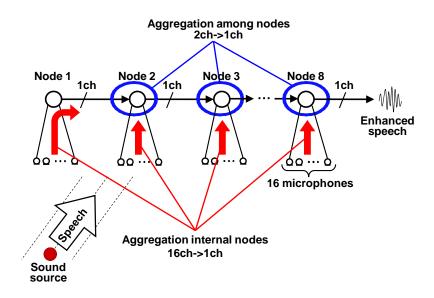

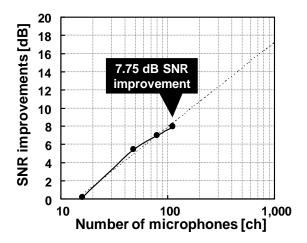

In the sixth part, the decentralized sound acquisition system is reported for a low-power ubiquitous digital signal processing system. The system uses a microphone-array-based sensor node network for sound acquisition. The sensor node has a voice activity detector (VAD), a sound-source localization module, and a sound-source enhancement module. Introducing a VAD circuit and power manager reduces the stand-by power. The VAD circuit outputs whether an input signal includes speech data or not. When the VAD module detects a speech signal, a main application module and signal-processing module are connected to a power source. When a speech signal is not detected, these circuits are blocked off. According to the speech-signal emergence ratio, such power management can save energy. To increase this saving factor, an extremely low-powered VAD was designed. The proposed VAD hardware achieves  $3.49~\mu W$  at a frequency of 100~kHz. The sound acquisition performance of the proposed system is also presented in this part.

Finally, the conclusion of this study is presented. It is hoped that this research will help many designers to develop advanced digital signal processing architecture in the deep submicron era using low-power SoC as well as 32-nm or 22-nm devices.

Keywords: VLSI, SRAM, Low power, Low voltage, Speech recognition, Human interface, HMM, GMM, Viterbi, Sound source localization, Sound source separation

# **Table of Contents**

| Abstr  | act                                              | i    |

|--------|--------------------------------------------------|------|

| Table  | of Contents                                      | v    |

| List o | f Figures                                        | viii |

| List o | f Tables                                         | xiii |

| Chapt  | ter 1 Introduction                               | 1    |

| 1.1    | Background of this Research Area                 | 1    |

| 1.2    | Objective of this Study                          | 3    |

| 1.3    | Overview of this Thesis                          | 3    |

| Chapt  | ter 2 Issues of Low-Power Signal Processing VLSI | 7    |

| 2.1    | Introduction                                     | 7    |

| 2.2    | Issue on SRAM Power Consumption                  | 8    |

| 2.3    | Issue of Minimum Operating Voltage of SRAM       | 11   |

| 2.4    | Issue of Memory Bandwidth                        | 11   |

| 2.5    | Issue of Sound Acquisition Standby-Power         | 14   |

| 2.6    | Summary                                          | 15   |

| Chapt  | ter 3 Low-Power Two-Port SRAM Design             | 17   |

| 3.1    | Introduction                                     | 17   |

| 3.2    | 8T SRAM                                          | 18   |

| 3.3    | 10T Single-End SRAM (10T-S SRAM)                 | 20   |

| 3.4    | 10T Differential SRAM (10T-D SRAM)               | 23   |

| 3.5    | Reducing the Number of Charge/Discharge Times    | 24   |

| 3.     | 5.1 Application to Video Images                  | 24   |

| 3.     | 5.2 Block Size Optimization                      | 25   |

| 3.6    | Design in 90-nm Process Technology               | 27   |

| 3.0    | 6.1 Cell and Macro Layouts                       | 27   |

| 3.0    | 6.2 Delay Model of Read-Bitline RC Trees         | 30   |

| 3.0    | 3.3 Chip Overview                                | 33   |

| 3.0   | 6.4                 | Operating Frequency and Supply Voltage    | 35         |

|-------|---------------------|-------------------------------------------|------------|

| 3.0   | 6.5                 | Power                                     | 36         |

| 3.7   | De                  | sign in 45-nm Process Technology          | 38         |

| 3.    | 7.1                 | Cell and Macro Layouts                    | 38         |

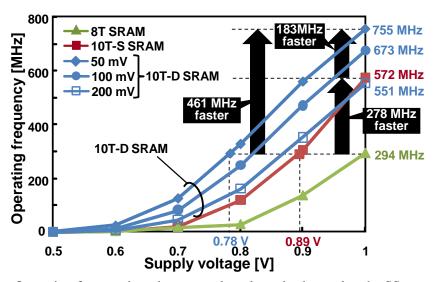

| 3.    | 7.2                 | Operating Frequency versus Supply Voltage | 41         |

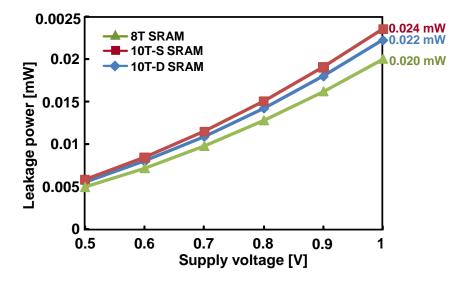

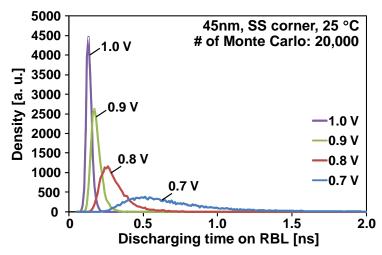

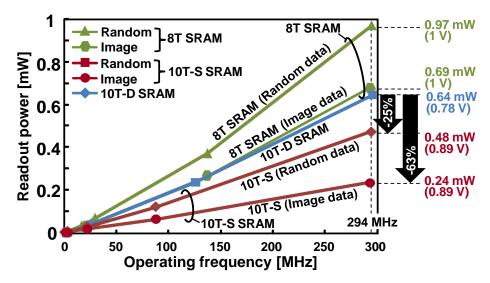

| 3.    | 7.3                 | Power                                     | 44         |

| 3.8   | Su                  | mmary                                     | 46         |

| Chapt | ter 4               | Two-Port SRAM Design for DVFS             | 49         |

| 4.1   | Int                 | roduction                                 | 49         |

| 4.2   | De                  | pendable SRAM: overview                   | 50         |

| 4.3   | 7T                  | /14T SRAM                                 | 51         |

| 4.4   | 9T                  | /18T SRAM                                 | <b>5</b> 3 |

| 4.5   | Ch                  | ip Implementation and Measurement Results | 56         |

| 4.6   | Su                  | mmary                                     | 59         |

| Chapt | ter 5               | Memory-Bandwidth Reduction for LVRCS      | 61         |

| 5.1   | Int                 | troduction                                | 61         |

| 5.2   | $\operatorname{Sp}$ | eech Recognition Overview                 | 61         |

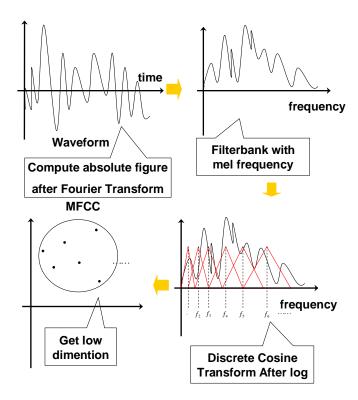

| 5.2   | 2.1                 | MFCC Feature Extraction                   | 62         |

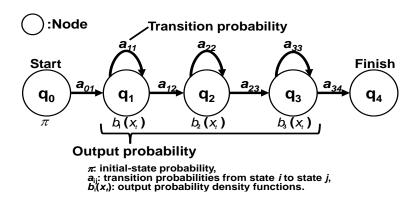

| 5.2   | 2.2                 | GMM Computation                           | 62         |

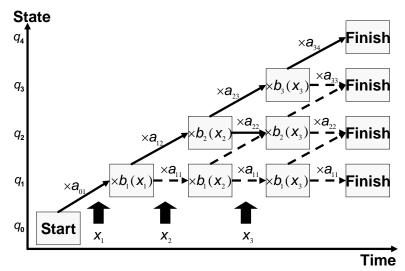

| 5.2   | 2.3                 | Time-Synchronous Viterbi Beam Search      | 65         |

| 5.2   | 2.4                 | N-gram Language Model Search              | 66         |

| 5.3   | Re                  | ferential Hardware Design                 | 67         |

| 5.3   | 3.1                 | Computation Amounts and Memory Bandwidth  | 67         |

| 5.4   | Pro                 | oposed Schemes                            | 68         |

| 5.4   | 4.1                 | Burst GMM Calculation                     | 68         |

| 5.4   | 4.2                 | Modified Unigram Language Model           | 69         |

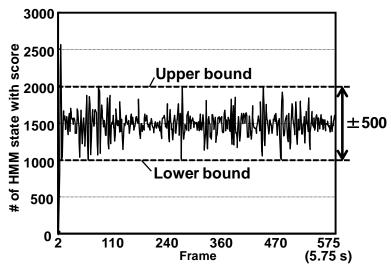

| 5.4   | 4.3                 | Threshold-Cutting Scheme                  | 70         |

| 5.4   | 4.4                 | Two-stage Language Model Search           | 71         |

| 5.5   | VL                  | SI Architecture                           | 72         |

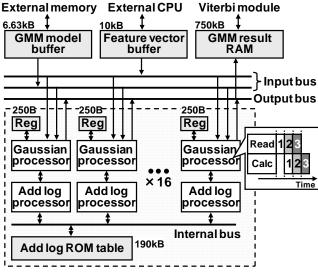

| 5.    | 5.1                 | Implementation of GMM Computation         | 74         |

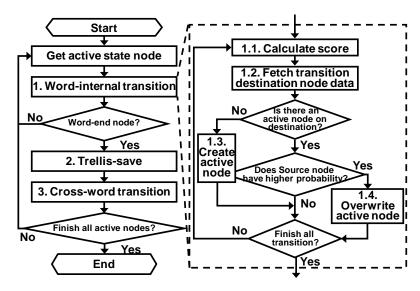

| 5.    | 5.2                 | Viterbi and N-gram Architecture           | 76         |

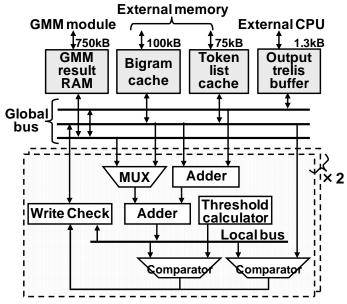

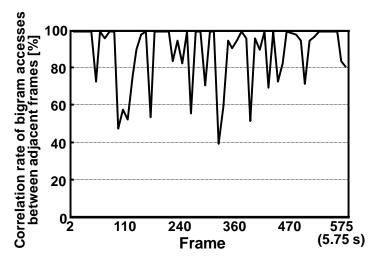

| 5.    | 5.3                 | Bigram Cache                              | 78         |

| 5.5     | 5.4   | Token List Cache.                                   | 80  |

|---------|-------|-----------------------------------------------------|-----|

| 5.6     | Im    | plementation Results                                | 80  |

| 5.6     | 3.1   | Required Frequency and Memory Bandwidth             | 81  |

| 5.6     | 3.2   | Comparison with other Architectures                 | 81  |

| 5.7     | Sui   | mmary                                               | 83  |

| Chapt   | er 6  | Low-Standby-Power Decentralized Sound Acquisition . | 85  |

| 6.1     | Int   | roduction                                           | 85  |

| 6.2     | Int   | elligent Ubiquitous Sensor Network and Its Node     | 86  |

| 6.3     | Voi   | ce Activity Detection                               | 88  |

| 6.3     | 3.1   | VAD Algorithms                                      | 89  |

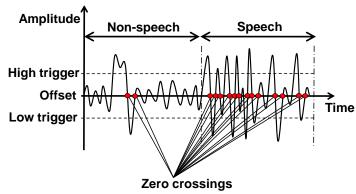

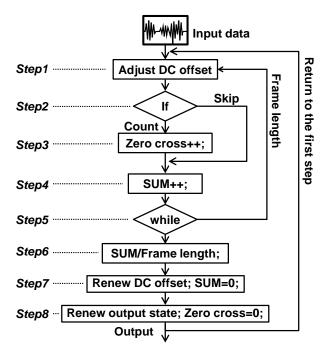

| 6.3     | 3.2   | Zero-Crossing VAD Algorithm                         | 89  |

| 6.3     | 3.3   | Modification the Zero-Crossing Algorithm            | 90  |

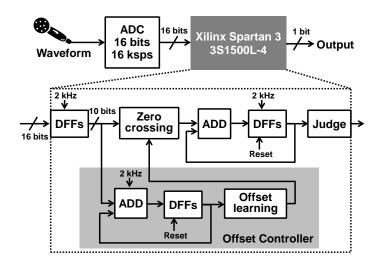

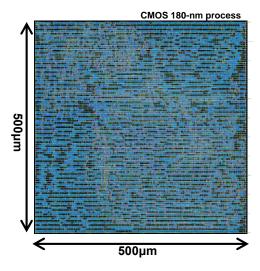

| 6.3     | 3.4   | Hardware Implementation of VAD                      | 92  |

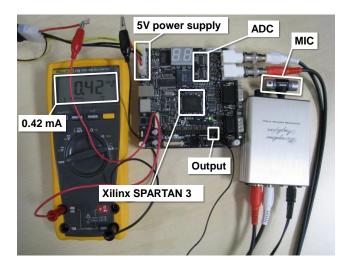

| 6.3     | 3.5   | Experimental Results                                | 94  |

| 6.4     | Pro   | posed Sound Acquisition Scheme                      | 95  |

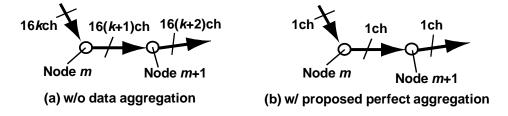

| 6.4     | 1.1   | Proposed Data Aggregation Scheme                    | 96  |

| 6.4     | 1.2   | Sound Source Localization Algorithm                 | 97  |

| 6.4     | 4.3   | Three-Dimensional Sound Source Localization         | 98  |

| 6.4     | 1.4   | Simulation Results.                                 | 100 |

| 6.5     | Im    | plementation of the Microphone Array System         | 100 |

| 6.5     | 5.1   | Implementation                                      | 100 |

| 6.6     | Fu    | ture Work                                           | 103 |

| 6.7     | Sui   | mmary                                               | 104 |

| Chapt   | er 7  | Conclusion                                          | 105 |

| Refere  | ence  | s                                                   | 109 |

| List of | f Pul | olications and Presentations                        | 117 |

| Publ    | icati | ons in journals and transactions                    | 117 |

| Pres    | enta  | tions in international conferences                  | 118 |

| Pres    | enta  | tions in domestic conferences                       | 120 |

| Ackno   | wlea  | dgments                                             | 125 |

# **List of Figures**

| Fig. | 1.1   | Various applications of speech recognition                                  |

|------|-------|-----------------------------------------------------------------------------|

| Fig. | 1.2   | Front end and back end of a speech recognition system 3                     |

| Fig. | 1.3   | Outline of this thesis                                                      |

| Fig. | 2.1   | Trend of the memory area in future SoCs                                     |

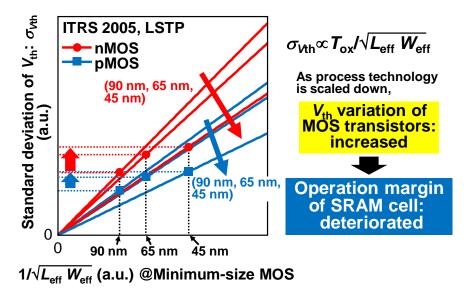

| Fig. | 2.2   | Pelgrom plots of different processes. The standard deviation of $V_{ m th}$ |

|      | incre | eases as process technology is scaled down                                  |

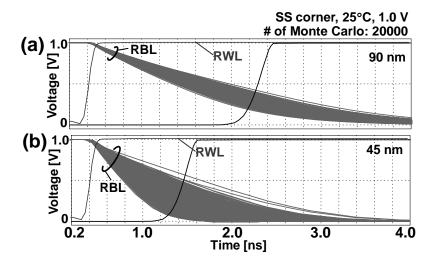

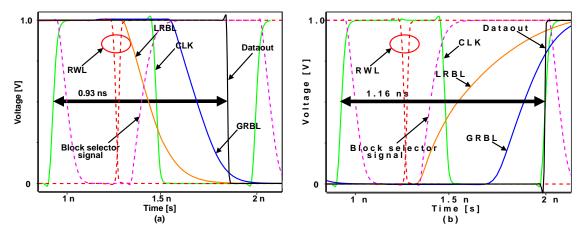

| Fig. | 2.3   | RBL operation waveforms of (a) 90-nm and (b) 45-nm technologies at          |

|      | the S | SS corner (25°C)                                                            |

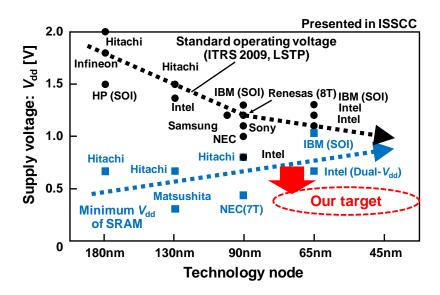

| Fig. | 2.4   | Trend of nominal operating voltage and minimum voltage of SRAM11 $$         |

| Fig. | 2.5   | Conventional processor used for LVRCS                                       |

| Fig. | 2.6   | Vocabulary cover rate on various media, as examined by the National         |

|      | Insti | tute for Japanese Language and Linguistics                                  |

| Fig. | 2.7   | Conventional architectures for real-time speech recognition and our         |

|      | targe | et performance                                                              |

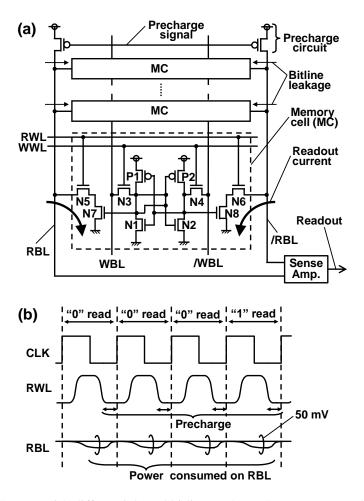

| Fig. | 3.1   | 8T dual-port SRAM: (a) a schematic and (b) waveforms in a read              |

|      | oper  | ation                                                                       |

| Fig. | 3.2   | 10T SRAM with a single-end read bitline (10T-S SRAM): (a) a                 |

|      | sche  | matic and (b) waveforms in read operation                                   |

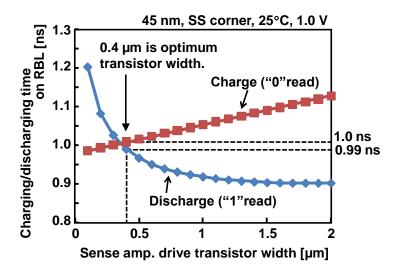

| Fig. | 3.3   | Charging-discharging times on an RBL in a 10T-S SRAM when a sense           |

|      | amp   | lifier drive transistor width is changed at the SS corner (25°C)22          |

| Fig. | 3.4   | 10T SRAM with differential read bitlines (10T-D SRAM): (a) a                |

|      | sche  | matic and (b) waveforms in read operation                                   |

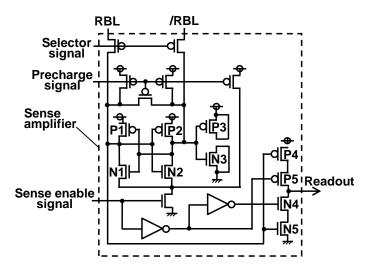

| Fig. | 3.5   | Circuit schematic of a sense amplifier in the 10T-D SRAM                    |

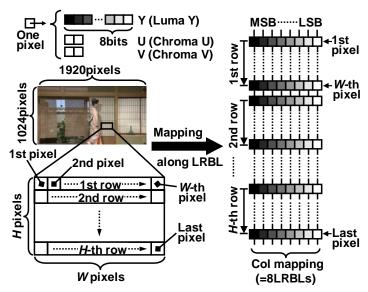

| Fig. | 3.6   | Example of H.264 image data and its mapping onto eight LRBLs 25             |

| Fig. | 3.7   | HD video sequences. Each sequence comprises 100 frames and 1920 $\times$    |

|      | 1024  | l pixels                                                                    |

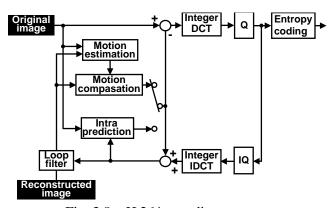

| Fig. | 3.8   | H.264 encoding process. 26                                                  |

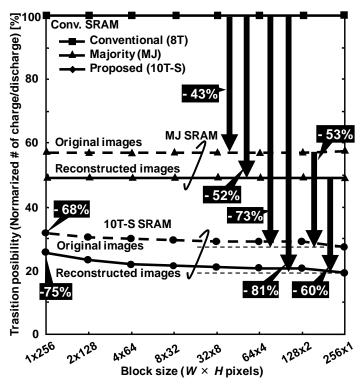

| Fig. | 3.9   | Transition possibilities (the normalized quantities of charge-discharge     |

|      | time  | s) on an LRBL between the conventional 8T, MJ, and proposed 10T-S           |

|      | SRA   | Ms when a block size is changed                                             |

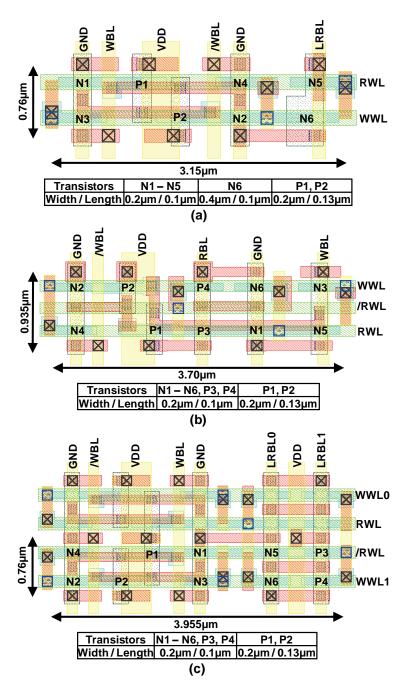

| Fig. | 3.10   | Layouts of (a) the conventional MC, (b) the proposed MC without             |

|------|--------|-----------------------------------------------------------------------------|

|      | shared | WL structure, and (c) the proposed MC with a shared WL structure 28         |

| Fig. | 3.11   | Shared WL structure                                                         |

| Fig. | 3.12   | A $\pi$ -type RC model of the SRAM read port                                |

| Fig. | 3.13   | Elmore delays by numeric calculation using ASPLA 90-nm process              |

|      | param  | eters. (a) Conventional 8T SRAM and (b) proposed 10T-S SRAM with            |

|      | the sh | ared WL structure                                                           |

| Fig. | 3.14   | Block diagram of a memory cell block in the proposed $10T\text{-}S$ SRAM.33 |

| Fig. | 3.15   | Chip micrograph of the proposed 10T-S SRAM and the conventional             |

|      | 8T SF  | RAM in a 90-nm process technology. The total memory size of each            |

|      | SRAN   | Л is 64 kb                                                                  |

| Fig. | 3.16   | Operation waveforms of the proposed 10T-S SRAM when (a) "0" and             |

|      | (b) "1 | " are read out in a 90-nm process technology (CC corner, 25°C) 34           |

| Fig. | 3.17   | Area comparison of 64-kb SRAMs in a 90-nm process technology $35$           |

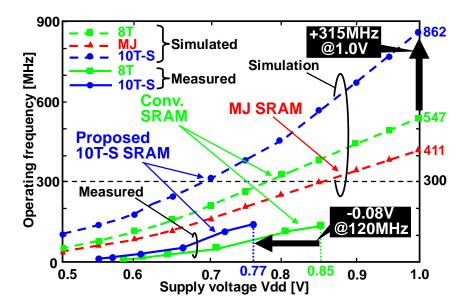

| Fig. | 3.18   | Operating frequencies versus supply voltage with 90-nm process              |

|      | techno | ology. Dotted lines show simulation results, and solid lines show the       |

|      | measu  | rement results in this frequency comparison with conventional               |

|      | archit | ecture36                                                                    |

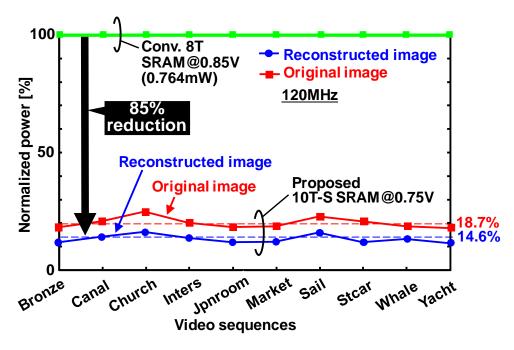

| Fig. |        | Measured readout power at 120 MHz when reading the original images          |

|      | and re | constructed images                                                          |

| Fig. | 3.20   | (a) Readout power versus operating frequencies in a 90-nm process           |

|      | techno | ology. (b) Magnified view                                                   |

| Fig. | 3.21   | Cell layouts of (a) 8T, (b) 10T-S, and (c) 10T-D SRAMs, in a 45-nm          |

|      | proces | ss technology                                                               |

| Fig. | 3.22   | Macro layouts of (a) 8T, (b) 10T-S, and (c) 10T-D SRAMs, in a 45-nm         |

|      | proces | ss technology. The total memory capacity of each macro is 64 kb 40          |

| Fig. | 3.23   | Operation waveforms of (a) 8T, (b) 10T-S, and (c) 10T-D SRAMs at the        |

|      | SS co  | rner (25°C)                                                                 |

| Fig. | 3.24   | Operating frequencies when a supply voltage is changed at the SS            |

|      | corner | (25°C)                                                                      |

| Fig. | 3.25   | Leakage power comparison of 8T, 10T-S, and 10T-D SRAMs at the CC            |

|      | corne  | : (25°C)                                                                    |

| Fig. 3.26 Density function of discharging time on RBL variation of 10T-D           |

|------------------------------------------------------------------------------------|

| SRAMs44                                                                            |

| Fig. 3.27 Readout power versus operating frequencies in a 45-nm process            |

| technology at the CC corner (25°C)                                                 |

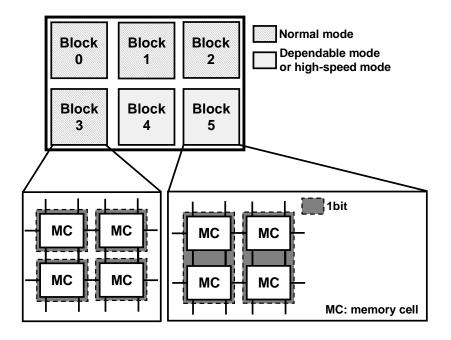

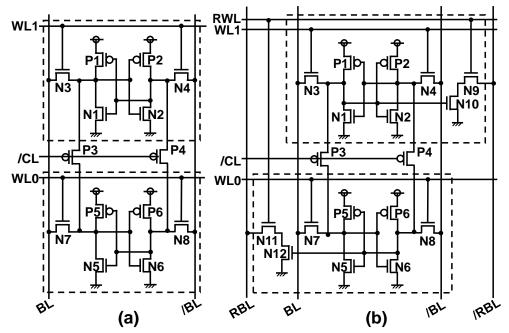

| Fig. 4.1 Dependable SRAM                                                           |

| Fig. 4.2 Schematics of (a) a conventional 7T/14T bitcell pair and (b) the          |

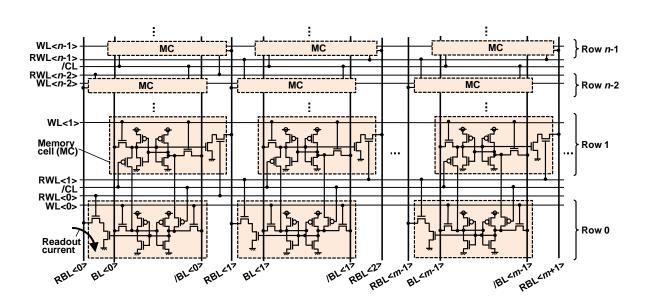

| proposed 9T/18T bitcell pair53                                                     |

| Fig. 4.3 Interleaved BL structure for read port in proposed 9T/18T SRAM. An        |

| RBL is shared by an upper left and lower right (or upper right and lower left)     |

| bitcells. An RWL is also shared but it is connected to every other bitcell 54      |

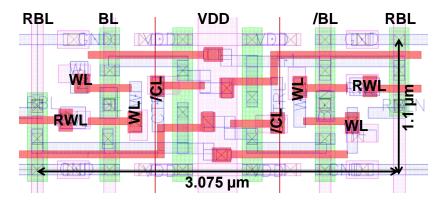

| Fig. 4.4 Layout of 9T/18T bitcell pair in a 65-nm process                          |

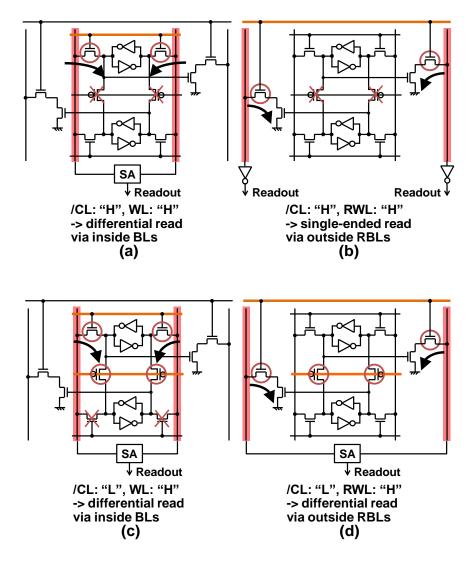

| Fig. 4.5 Readouts of four kinds: (a) normal-mode differential read via inside BLs, |

| (b) normal-mode single-ended read via outside read port, (c)                       |

| dependable-mode differential read via inside BLs, and (d) dependable-mode          |

| differential read via outside read port. Here, SA denotes a sense amplifier 55     |

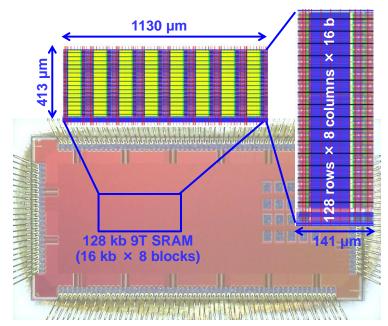

| Fig. 4.6 Chip micrograph and SRAM macro layout                                     |

| Fig. 4.7 Measured BERs of 9T/18T SRAM for four read operations. Frequency is       |

| 1 MHz57                                                                            |

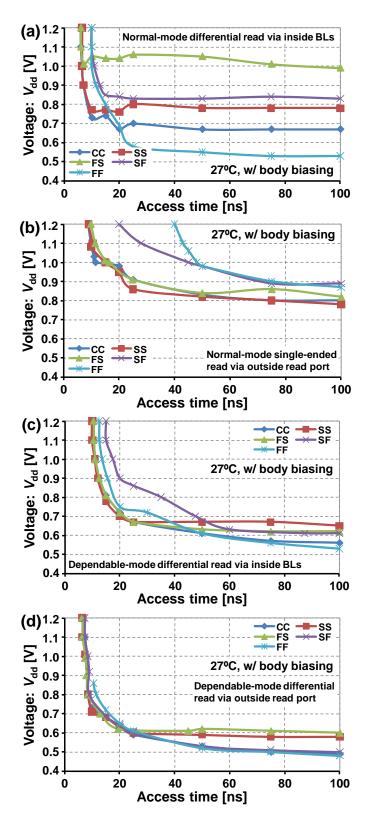

| Fig. 4.8 Measured characteristics in access time versus supply voltage: (a)        |

| normal-mode differential readout, (b) normal-mode single-ended readout, (c)        |

| dependable-mode inside differential readout, and (d) dependable-mode               |

| outside differential readout                                                       |

| Fig. 5.1 Speech recognition flow with the HMM algorithm                            |

| Fig. 5.2 Calculation flow to obtain MFCC from the waveform data                    |

| Fig. 5.3 Left-right HMM                                                            |

| Fig. 5.4 Left–right HMM calculation flow                                           |

| Fig. 5.5 Viterbi computation                                                       |

| Fig. 5.6 Required frequency in a real-time process with the referential hardware   |

| [48, 49]68                                                                         |

| Fig. 5.7 Required memory bandwidth in a real-time process with the referential     |

| hardware [48, 49]68                                                                |

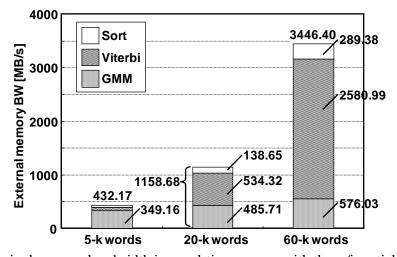

| Fig. 5.8 Tree dictionary for Viterbi search                                        |

| Fig. | 5.9   | Beam width variation with the threshold-cut scheme                    | 71  |

|------|-------|-----------------------------------------------------------------------|-----|

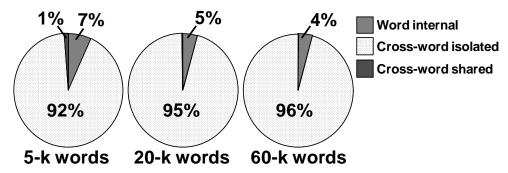

| Fig. | 5.10  | Appearance ratios of three transition types in Viterbi search in Juli | us  |

|      | 4.0.  |                                                                       | 72  |

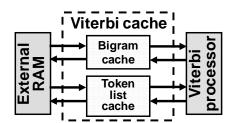

| Fig. | 5.11  | Cache architecture concept in Viterbi search processing.              | 73  |

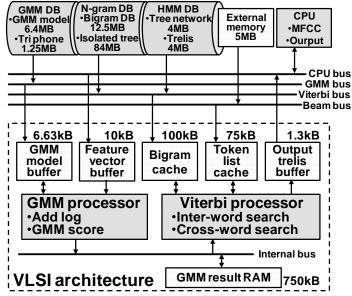

| Fig. | 5.12  | Block diagram of proposed processor architecture for a 60-k wo        | rc  |

|      | spee  | ch recognition system.                                                | 74  |

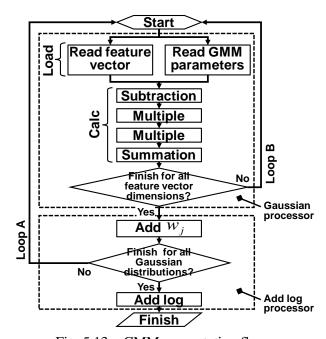

| Fig. | 5.13  | GMM computation flow.                                                 | 75  |

| Fig. | 5.14  | GMM processor data path.                                              | 76  |

| Fig. | 5.15  | Viterbi computation flow.                                             | 77  |

| Fig. | 5.16  | Proposed Viterbi architecture.                                        | 77  |

| Fig. | 5.17  | Correlation rate of bigram accesses between adjacent frames profile   | ec  |

|      | using | g Julius 4.0.                                                         | 78  |

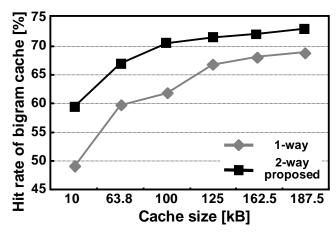

| Fig. | 5.18  | Bigram cache hit rate profiled using Julius 4.0.                      | 79  |

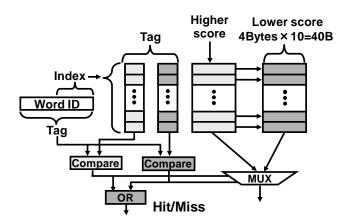

| Fig. | 5.19  | Proposed two-way cache.                                               | 79  |

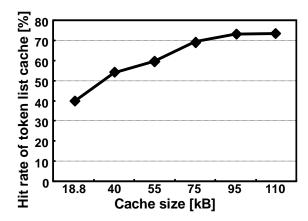

| Fig. | 5.20  | Token list cache hit rate.                                            | 80  |

| Fig. | 5.21  | Required frequency comparison with conventional architecture          | 82  |

| Fig. | 5.22  | Required memory bandwidth using the real-time process.                | 82  |

| Fig. | 6.1   | Intelligent ubiquitous sensor network (IUSN) and block diagram of     | ·   |

|      | sub-  | array node                                                            | 87  |

| Fig. | 6.2   | Flow chart of intelligent ubiquitous sensor nodes.                    | 88  |

| Fig. | 6.3   | Zero-crossing point example. The offset line shows the direct curre   | n   |

|      | (DC   | component.                                                            | 9(  |

| Fig. | 6.4   | Zero-crossing VAD algorithm flow.                                     | 91  |

| Fig. | 6.5   | Block diagrams of the integrated devices. The D flip-flop (DFF) circu | its |

|      | keep  | up each input data asynchronously.                                    | 92  |

| Fig. | 6.6   | FPGA board with a microphone and a current tester.                    | 93  |

| Fig. | 6.7   | Layout plot of the zero-crossing algorithm integrated using CMC       | )S  |

|      | 0.18  | -μm process technology.                                               | 93  |

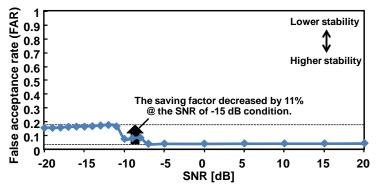

| Fig. | 6.8   | The false acceptance rate (FAR) in VAD outputs using the number       | of  |

|      | non-  | speech frames of the recorded condition as normalized criteria        | 94  |

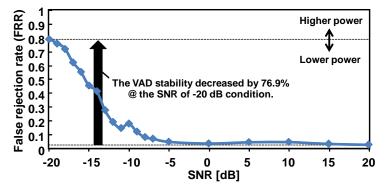

| Fig. | 6.9   | The false rejection rate (FRR) in VAD outputs using the speech fram   | es  |

|      | of th | e recorded condition as normalized criteria.                          | 94  |

#### xii List of Figures

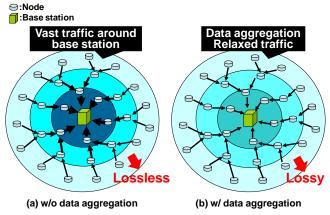

| Fig. 6.10 | Network traffic with (a) lossless and (b) lossy multi-hop networks 95 |

|-----------|-----------------------------------------------------------------------|

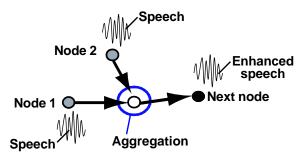

| Fig. 6.11 | Example of perfect aggregation among neighboring nodes96              |

| Fig. 6.12 | Delay-and-sum beam-forming mechanism. 96                              |

| Fig. 6.13 | Three-dimensional sound-source localization                           |

| Fig. 6.14 | Sound-source localization experiment                                  |

| Fig. 6.15 | Sound-source localization accuracy                                    |

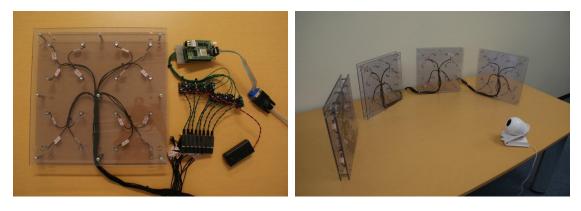

| Fig. 6.1  | 6 System photographs: intelligent ubiquitous sensor node and a        |

| mic       | cophone array comprising sub-arrays                                   |

| Fig. 6.17 | Experiment diagrams. 101                                              |

| Fig. 6.18 | SNR improvements vs. the number of microphones                        |

| Fig. 6.19 | Examples of traffic data sizes: (a) without and (b) with the proposed |

| perf      | ect data aggregations                                                 |

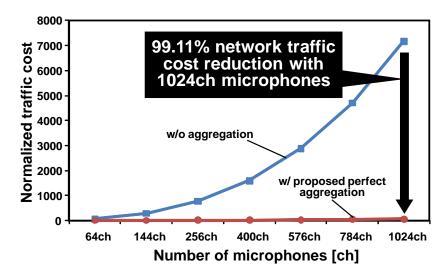

| Fig. 6.20 | Normalized traffic cost vs. the number of microphones                 |

# **List of Tables**

| Table 3.1 | Simulation conditions in the H.264 encoder.                     | 26    |

|-----------|-----------------------------------------------------------------|-------|

| Table 3.2 | Values of M, CL, CG, RL, RG, RMC, and RD, as obtained usin      | g the |

| ASPL      | A 90-nm process parameters.                                     | 31    |

| Table 4.1 | Three modes in 7T memory cells.                                 | 52    |

| Table 4.2 | Body bias settings: $\Delta V_{ m tn}$ and $\Delta  V_{ m tp} $ | 57    |

| Table 5.1 | Memory bandwidth in 20-k word Viterbi search                    | 72    |

| Table 5.2 | Comparison with other hardware-based systems.                   | 83    |

| Table 6.1 | Device utilization summary.                                     | 92    |

# **Chapter 1 Introduction**

## 1.1 Background of this Research Area

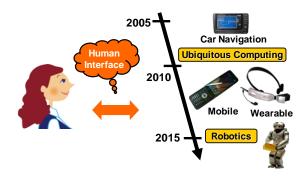

The remarkable progress of digital signal processing technology attained in recent years has allowed for practical application of multimedia applications using voice and images. These applications now span widely various fields such as car navigation equipment, portable appliances, robots, automatic writing at conferences, indexing for retrieval of images and voices, and so on. Of those, mobile equipment, wearable equipment, and intelligent robots have shown remarkable progress up to the present. Consequently, human interfaces have been attracting the attention of the people who are tasked with maintaining good natural communications between human beings and artificial systems that exist in various environments. Especially, speech recognition is remarkable as a human interface between a man and systems, allowing natural communications by anyone (presented in Fig. 1.1). Modern speech recognition systems are usually based on Hidden Markov Models (HMM). These are statistical models which output a sequence of symbols or quantities according to a probability function. Actually, HMMs are used in speech recognition because a speech signal can be treated as a piecewise stationary signal or as a short-time stationary signal, which is represented as triphones. Hierarchically, words are broken up into triphones and triphones are broken up into states. Speech recognition based on HMMs employs a large-scale trained dictionary, which consists of within-triphone (state-to-state) transitions and within-word (triphone-to-triphone) transitions. Large-vocabulary (more than 5,000 words) real-time continuous speech (LVRCS) recognition is necessary to achieve such a human interface. Actually, LVRCS supports completely hands-free interfaces because speech is the fundamental mode of human communication; moreover, speech interfaces offer a much broader range of application. In order for the speech recognition system to develop functions fully as a human interface, a continuous speech recognition system with extensive vocabulary and real-time features must be produced. At the same time, for implementation of a human interface for use in wearable equipment and robots, requirements for low power consumption and low cost are necessary. Although some software-based LVRCS exist, these solutions necessitate the use of a high-performance

processor, which consumes much power. For this reason, it is difficult to implement LVRCS on a mobile device, on wearable equipment, or in robots. Consequently, an application-specific processor for use in an LVRCS recognition system, a processor that can achieve high speed and low power consumption, is requested. A hardware approach such as those of VLSI or FPGA, can achieve more compact, more low-powered and more battery-friendly speech recognition because of their advantages for processing speed and power consumption: a high-speed but low-power speech-recognition processor is a necessity for mobile applications. For such a processor, the innovative low-power memory and digital architecture are necessary.

Fig. 1.1 Various applications of speech recognition.

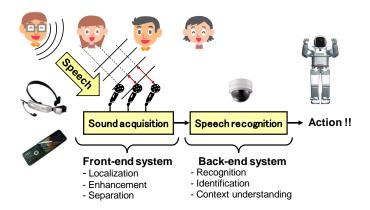

In this dissertation, the research targets include both a back-end speech recognition system and a front-end speech acquisition system. Figure 1.2 presents some front-end and back-end system examples. A front-end system incorporates sound-acquisition functions such as sound-source localization, sound enhancement, and sound source separation. A back-end includes speech signal processing functions such as speech recognition, speaker identification, and context understanding. In the near future, an era of ubiquitous computing is coming, with numerous cameras and microphones located on walls and roofs of living spaces. They will obtain speech data and visual information automatically and support absolutely hands-free systems. The front-end of a speech recognition system usually involves multiple signal processing using a multi-channel interface such as a microphone array. A microphone array can localize sound sources and separate multiple sources using spatial information that can be collected along with the acquired sounds. The computational effort of these operations increases exponentially with the number of microphones, but the operating performance is known to increase as well. To reduce the increased power of a microphone array and to satisfy

recent demands for ubiquitous sound acquisition, it is necessary to realize a large sound processing system that uses little power. For such a system, the innovative low-voltage operable memory and digital architecture are necessary to reduce the stand-by power at the system level.

Fig. 1.2 Front end and back end of a speech recognition system.

### 1.2 Objective of this Study

In this research, hardware approaches are introduced to realize a wearable or ubiquitous speech recognition system that uses little power, as described above. Particularly, memory and digital architecture techniques are presented. Hardware approaches such as those using very large scale integrated (VLSI) circuits or a field programmable gate array (FPGA), can achieve more compact and more battery-friendly speech recognition using less power because of its advantages of high processing speed and low power consumption. The proposed architecture overcomes various issues related to speech signal processing and VLSI circuits, such as memory bandwidth, parallel computing, reduced operation voltage, low-power operation, power management, and so on. The main objective of these hardware techniques is to expand the dictionary size of speech recognition and the number of microphone arrays of the front-end sound acquisition with low power. Thereby, the system can assist human beings effectively.

#### 1.3 Overview of this Thesis

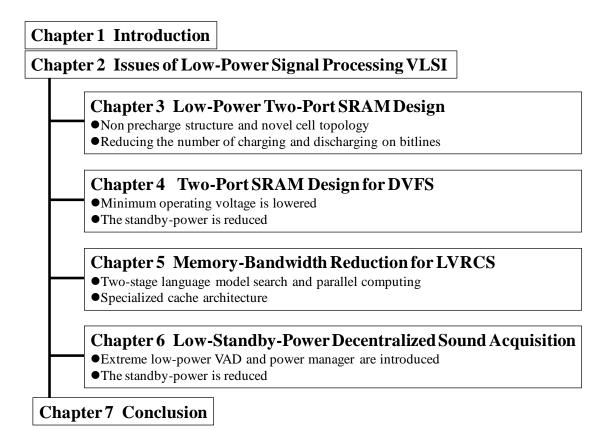

In this dissertation, low-power techniques of memory and digital architecture are presented for wearable and ubiquitous signal processing applications. Figure 1.3 shows

#### 4 Chapter 1 Introduction

that the outline of this thesis can be visualized with remarkable lucidity for this ambitious exposition. First, the background and objective of this study are described. For LVRCS and ubiquitous sound acquisition systems, critical issues related to hardware implementation are pointed out in Chapter 2. The main issues of an advanced architecture and memory designs are summarized as four limitations: memory bandwidth, power dissipation, standby electricity, and low-voltage operation. An explanation for each limitation is provided to enhance understanding of the study objective.

In the next four parts of this thesis, practical hardware design techniques against each limitation are demonstrated. In Chapter 3, the low-power two-port SRAM design technique against process variation is discussed for low-power CMOS technology. The speech signal processing demands memory IP blocks as not only single-port SRAM but also as dual-port SRAM to perform parallel operations. To reduce the active power of the SRAM bitline, a non-precharge structure and novel cell topology are proposed. The new SRAM has an advantage in terms of the number of charge and discharge times. In this part. Results show that the adequate compensate SRAM topologies are performed against the variation of threshold voltage of transistors and temperature. It is designed and fabricated using 90-nm and 45-nm advanced CMOS technology. Test results show that the active power is lowered by this circuitry.

Chapter 4 introduces a two-port SRAM design for a dynamic voltage and frequency scaling (DVFS) environment considering the proposed sound acquisition system described in chapter 5. The SRAM expands the operable-voltage width for reduced low-standby-power. The new SRAM presents advantages in terms of improvement of the minimum operating voltage lowering. The SRAM designed and fabricated using 65-nm CMOS technology and test results show that the minimum operating voltage is lower.

In Chapter 5, the memory-bandwidth reduction techniques for LVRCS, which are critically dependent on the VLSI bus frequency, are discussed first. It is presented that parallel computing using speech signal correlation contributes to reduction of the memory bandwidth on Gaussian Mixture Model setting up. The two-stage language model search and specialized cache were also introduced for Viterbi processing to reduce memory bandwidth. The two-stage language model search reduces the

computing amounts as well. The pipelining architecture is demonstrated for reducing the required frequency for real-time operation. An evaluation result obtained using hardware description language (HDL) and a verilog simulator shows the reduction of the memory bandwidth and required frequency using the proposed techniques.

In Chapter 6, the decentralized sound acquisition system is reported. The stand-by power is reduced by introducing a VAD circuit and power manager. The VAD circuit outputs whether an input signal includes speech data or not. When the VAD module detects a speech signal, a main application module and signal-processing module are connected to a power source. When a speech signal is not detected, these circuits are blocked off. According to the speech signal emergence ratio, the power management described above can save energy. To increase this saving factor, an extremely low-powered VAD is presented. The sound acquisition performance of the proposed system is also shown in this part.

The conclusion of this study is described in Chapter 7. The overall contribution is summarized briefly.

Fig. 1.3 Outline of this thesis.

# **Chapter 2** Issues of Low-Power Signal **Processing VLSI**

#### 2.1 Introduction

Miniaturization of semiconductors has been a driving impetus for improvement of computer performance and the eventual progress of information technology. At International Electron Devices Meeting (IEDM) 2010, Taiwan Semiconductor Manufacturing Company Ltd., a major semiconductor foundry, disclosed logic CMOS technology for the 22 nm/ 20 nm generation [1]. In addition a research team with members from Intel Corp. and Micron Technology announced 64 Gb NAND flash memory of MLC type, which uses 25-nm manufacturing technology [2].

At present, when practical application of 22 nm generation is at hand, as described above, the International Technology Roadmap for Semiconductor (ITRS) predicts that miniaturization of channel length of 4.5 nm will be realized steadily in 2022. When miniaturization technology advances, the number of transistor devices which can be integrated increases. Given the same number of devices, the chip area is less, the number of chips obtainable from one sheet of wafer increases, production costs decrease, power consumption decreases because of reduction in operating voltage, and the operation clock is improved.

In recent years, however, problems have arisen despite the clear benefits obtained through miniaturization. When insulating film is thinned to obtain sufficient electric field effect with reduced operating voltage, tunnel effects arise, by which electrons pass through the insulating film that is thinned to its extremity. As a result, leakage current and scattering of the threshold voltage became remarkable. The leakage current increases the semiconductor power consumption and simultaneously creates difficulties in increasing the operation clock.

When problems such as leakage current and scattering of the threshold voltage are resolved as research and development of the process advance, operations of logic LSI of gigahertz-order will be realized in fine processes in the future. Even if such is not the case, it is anticipated that as the technology to improve performance becomes independent of the increase in the operation clock, then the use of micro-architecture to improve IPC and of multi-core structures will be promoted, thereby drastically improving the VLSI computing performance. Particularly from the perspectives of multimedia applications, benefits from miniaturization are improvement of computing performance and large-capacity memory. Along with these two points, a system that has not been attained to date will be realized for use with image-processing and voice-processing systems in the near future. It is also considered that research and development of VLSI for image and speech processing will be promoted in two directions of exclusive use and general-purpose use, with encouragement by further development of VLSI miniaturization technology.

Although VLSI for general-purpose use has already been realized in the form of GPGPU and DSP, general-purpose VLSI remains absolutely necessary because image-processing and speech-processing uses diverse algorithms. It is expected that general-purpose use VLSI can provide higher computing performance with low power consumption because of miniaturization. Actually, VLSI for dedicated use is advantageous to VLSI for general-purpose use in terms of real-time performances and ultra-low power consumption. It is necessary in such a case in which interactive and real-time performances that can not be attained by VLSI for general-purpose use are required. Applications which show the benefits of miniaturization most are image processing and speech processing, which demand real-time performance in applications with limited use of batteries such as portable appliances.

For high-performance signal-processing systems, the use of digital-architecture and embedded SRAMs is confronting a crisis of increasing power dissipation. The number of accesses to the external memory increases according to the data size of signal processing. Total computation is also increasing according to the development of the application. These demands induce a system bottleneck. In this chapter, the fundamental principles of the VLSI signal-processing system and scaling trends of SRAM are described briefly.

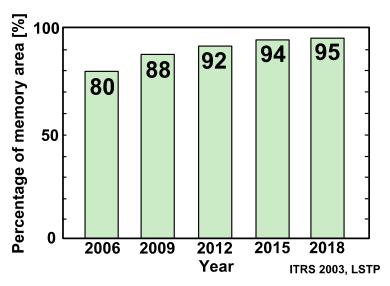

## 2.2 Issue on SRAM Power Consumption

As the ITRS Roadmap predicts, the memory area is becoming larger (presented in Fig. 2.1). That area is expected to occupy 90% of the system on a chip by 2013 [3]. For example, an H.264 encoder used for a high-definition television requires at least a

500-kb memory as a search-window buffer, which consumes 40% of its total power [4]. As multimedia applications have become more complex and memory-demanding, large-capacity SRAMs will be adopted as frame buffers and/or restructured-image memory on video chips. The large-capacity SRAM potentially dissipates a larger share of its total power, and dominates the circuit speed. Therefore, low-power and high-speed dual-port SRAMs are strongly demanded for signal processing. Particularly, the power and operating frequency in a read operation are crucial because the readout takes place more frequently than write-in in a video codec. For instance in motion estimation, once picture data are written in memory, full-search algorithms or other motion compensation algorithms read out the data many times.

Fig. 2.1 Trend of the memory area in future SoCs

In fact, as process technology is scaled down, the threshold-voltage ( $V_{th}$ ) variation of MOS transistors is increased (presented in Fig. 2.2) [3] because the channel area ( $L_{eff} \times W_{eff}$ ) is shrunk as manufacturing processes advance. The readout current on the read bitline (RBL) is sensitive to the  $V_{th}$  variation. Figure 2.3 presents the readout operation waveforms of the single-end SRAM of 90-nm and 45-nm technologies. The SS corner, which denotes slow nMOS and slow pMOS, is one process corner, representing the extremes of fabrication-parameter variations within which a circuit that has been etched onto the wafer must function correctly. Designers examine the expected process range using 'worst case' analyses to verify that circuits will operate correctly under the  $V_{th}$  variation. The classic worst-case situation is the asymmetrical assignment of the  $V_{th}$

variation to nMOS and pMOS, which worsens the charge speed or discharge speed. However, such a worst case involves an impossible situation in terms of probability. Monte Carlo simulation with a statistical die average model yields much more realistic results of how the circuits and especially how an SRAM will operate over the expected die average process variations. During the deep submicron era, it will be increasingly important to design the SRAM read-port while remaining cognizant of the  $V_{\rm th}$  variation tolerance [5]. Monte Carlo simulation reveals the readout-timing variation and sense-timing difficulties and these lead to power dissipation in read operation.

Fig. 2.2 Pelgrom plots of different processes. The standard deviation of  $V_{\rm th}$  increases as process technology is scaled down.

Fig. 2.3 RBL operation waveforms of (a) 90-nm and (b) 45-nm technologies at the SS corner  $(25^{\circ}C)$ .

#### 2.3 Issue of Minimum Operating Voltage of SRAM

In order to save a power of an SoC, dynamic voltage and frequency scaling (DVFS) techniques that adaptively controls an operating frequency and supply voltage ( $V_{\rm dd}$ ) has been implemented in a mobile system [6]. However, a minimum operation voltage ( $V_{\rm min}$ ) is becoming higher as a fabrication technology is scaled down, since operation margins of memory cells in an embedded SRAM are degraded under both read and write conditions due to threshold-voltage ( $V_{\rm th}$ ) variation of MOSFETs. Figure 2.4 presents the nominal operating voltage and minimum voltage of SRAM as the fabrication technology is scaled down, as presented at International Solid-State Circuits Conference (ISSCC). Because the technology is advanced, the  $V_{\rm th}$  variations of MOS transistors become readily apparent. Because of the  $V_{\rm th}$  variation, operation margins of memory cells cannot be sustained in the conventional memory cells. A degradation of operation margins limits a lower bound of a supply voltage. Producing a low-voltage operating SRAM under the DVS environment is a key issue.

Fig. 2.4 Trend of nominal operating voltage and minimum voltage of SRAM.

## 2.4 Issue of Memory Bandwidth

Speech recognition technology has been used recently in various applications such as cellular telephones, car-navigation systems, PDAs, wearable computers, and robotics. Nevertheless, large vocabulary—more than 60-k words—real-time continuous speech recognition (LVRCSR) with an accurate model is too resource-hungry and

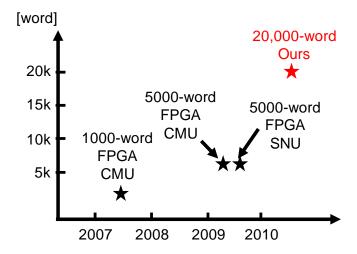

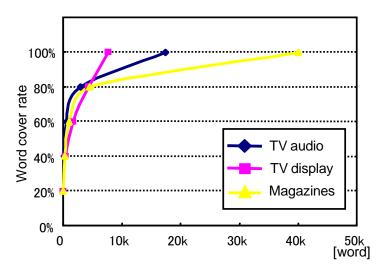

power-sensitive for use in software applications [7]. Figure 2.5 shows conventional hardware processors for LVRCS versus the vocabulary size. In terms of a hardware approach, the vocabulary size has remained around 5-k word recognition. Figure 2.6 presents the vocabulary cover rate in three situations: TV audio, TV display, and magazines. To process human daily conversation properly, more than 10-k word recognition is necessary considering general TV audio. Furthermore, more than 20-k word recognition is necessary to meet the need to process more natural conversation.

Fig. 2.5 Conventional processor used for LVRCS.

Fig. 2.6 Vocabulary cover rate on various media, as examined by the National Institute for Japanese Language and Linguistics.

A hardware approach, with implementation by VLSI or an FPGA, can achieve more compact and more battery-friendly speech recognition because of its advantageous processing speed and power consumption. To enhance the speech-recognition performance of different systems, some studies have applied hardware approaches. Lin *et al.* investigated FPGA implementations for 5-k word continuous speech recognition [8, 9], but the applications did not run in real time. Choi *et al.* investigated FPGA implementations for 20-k word speech recognition [10, 11], but both consumed slightly greater memory bandwidth (BW) and power. Ma *et al.* reported memory-bandwidth reduction of Gaussian Mixture Models (GMM) processing for real-time 20-k word speech recognition [12], but that method did not treat Viterbi processing. Therefore, memory bandwidth reduction on a Viterbi processor remains as an important task because it requires high memory bandwidth.

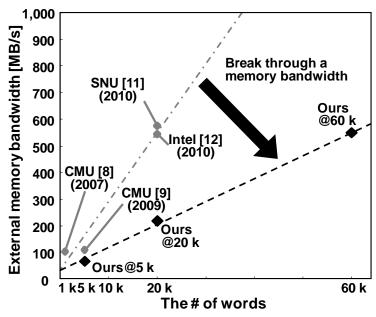

A comparison of external memory bandwidth among recently described hardware-based speech recognizers is presented in Fig. 2.7. To date, the hardware approach has never achieved real-time operation with a 60-k word language model because numerous computations and external memory bandwidth degrade as the vocabulary is increased. In the ubiquitous-computing era that is expected to prevail in the future, with further development of robotics technology, speech recognition systems are expected to become the main technique used for human interface devices for mobile, wearable, and intelligent robots. Actually, LVRCSR is anticipated as a key technology for such applications.

Fig. 2.7 Conventional architectures for real-time speech recognition and our target performance.

### 2.5 Issue of Sound Acquisition Standby-Power

Recent improvements in information processing technologies have produced real-time sound processing systems using microphone arrays [13]. One application is a meeting system with a 128-ch square microphone array [14], which captures speech data from every microphone. The microphone array processes signal recording and noise reduction, sound-source separation, speech recognition, speaker identification, and other tasks.

A microphone array can localize sound sources and separate multiple sources using spatial information of the acquired sounds. Huge microphone arrays have been widely investigated: arrays have been built at Tokyo University of Science (128 ch) [14], the University of Electro-Communication (156 ch) [15], Brown University and Rutgers University (512 ch) [16], and the Massachusetts Institute of Technology (1,020 ch) [17]. However, the problems of increasing computation, power consumption, and network costs render their practical use difficult, particularly in terms of sound-data acquisition. The main problem of conventional microphone array systems is that all microphones are connected to a single base station (high-performance sound server) with large-scale multi-channel sound recording devices. In conventional systems, the concentrative connection of a huge number of microphones engenders heavy network traffic. The computational effort increases polynomially as the number of microphones increases. If more than 1,000 microphones are used to collect data, then the signal-noise ratio (SNR) can be improved remarkably [17], but the network traffic and computational requirements would explode. To reduce the increased network traffic and computational power of a microphone array system and to satisfy recent demands for ubiquitous sound acquisition, it is necessary to realize a large sound-processing system covering wide-ranging human environments at low power.

## 2.6 Summary

For future low-power but high-performance signal processing systems, the key issues can be summarized as the following four items.

- active power consumption, especially on Dual-Port SRAM

- minimum SRAM operating voltage for a dynamic voltage and frequency scaling (DVFS) power controllable sensor node,

- memory bandwidth considering the large vocabulary language model, and

- standby-power of sound acquisition system including network traffic

The following four chapters explain solutions for the issues listed above.

# **Chapter 3** Low-Power Two-Port SRAM **Design**

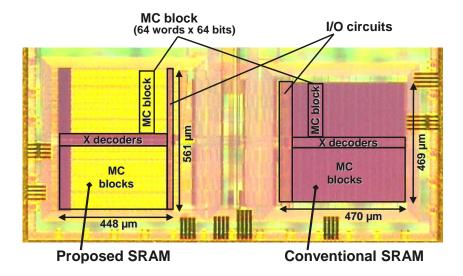

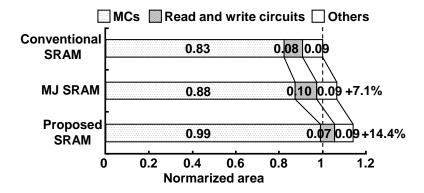

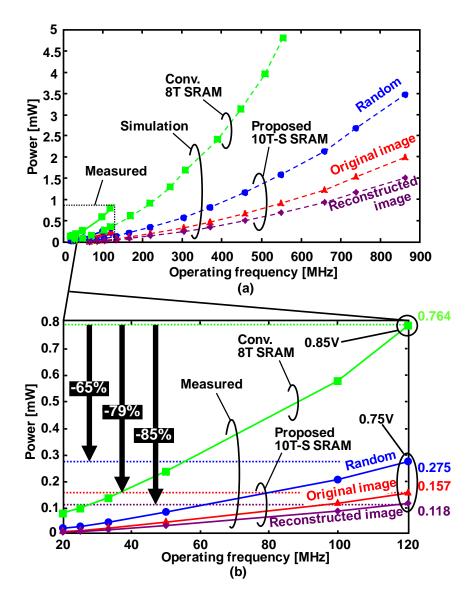

As process technology is scaled down, large-capacity SRAMs will be used. Their power requirements must be lowered. In this chapter, we propose a two-port non-precharge SRAM comprising 10 transistors that is suitable for use in processing a real-time video image that has statistical similarity. The simulation reveals that the proposed SRAM can operate at a 65% higher frequency than a conventional 8T SRAM because it has no precharge period. The area overhead is 14.4% in a 90-nm process technology. Measurements demonstrats that the proposed SRAM saves 85% of the readout power when used as an H.264 reconstructed-image memory.

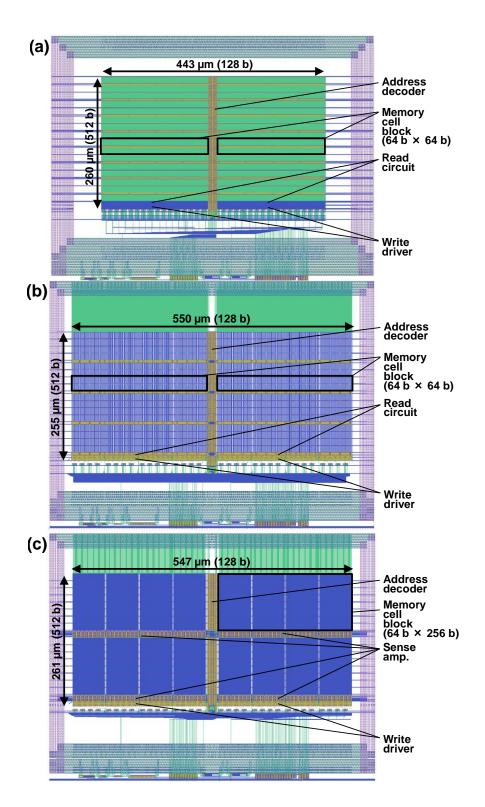

We also examine dual-port SRAM design in terms of its area, speed, and readout power in a 45-nm process technology. Although the 8T SRAM has the lowest transistor count, and although it is the most area-efficient, the readout power consumption is high and the cycle time is notably increased because of peripheral circuits. The 10T differential-port SRAM would operate fastest if the differential voltage were set to 50 mV. The 10T SRAM with a single-end read port consumes the least power.

#### 3.1 Introduction

As the ITRS Roadmap predicts, the memory area used on a chip is becoming larger. It will occupy 90% of an SoC's area by 2013 [3]. Even on a real-time video SoC, this trend is progressing. An H.264 encoder for a high-definition television requires at least a 500-kb memory as a search-window buffer, which consumes 40% of its total power [4]. As process technology is scaled down, a large-capacity SRAM will be adopted as a frame buffer and a restructured-image memory on a video chip, and might dissipate a larger share of its power. To save power in a real-time video application, this chapter describes a low-power two-port SRAM.

Furthermore, this chapter presents a comparison of dual-port SRAMs of three kinds in a 45-nm process technology. A dual-port SRAM is extremely useful for real-time video processing because it can make one read and one write access simultaneously in a clock cycle [4, 18–20]. We handle the three kinds of dual-port SRAMs: the 8T SRAM,

10T SRAM with a single-end read port (hereinafter, '10T-S SRAM'), and 10T SRAM with differential read ports (hereinafter, '10T-D SRAM').

#### **3.2 8T SRAM**

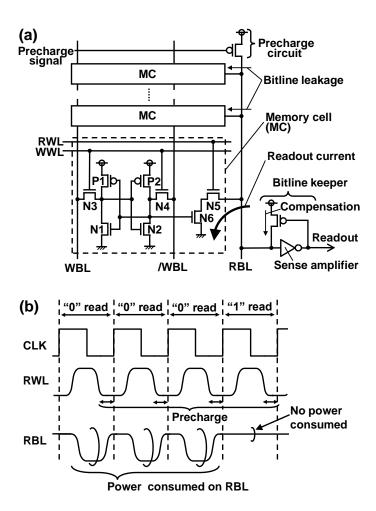

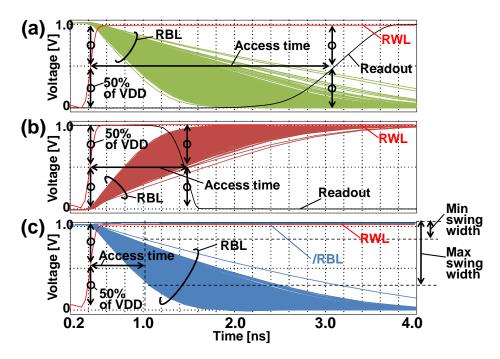

In the conventional eight-transistor (8T) two-port memory cell (MC) depicted in Fig. 3.1(a), two nMOS transistors (N5 and N6) for a read wordline (RWL) and a local read bitline (RBL) are added to a single-port 6T MC, which frees a static noise margin (SNM) in a read operation because it has a separate read port [21]. A precharge circuit must be implemented on the RBL so that the two nMOS transistors can sink a bitline charge to the ground and a certain power is dissipated by precharging (see Fig. 3.1(b)). Furthermore, the readout time becomes greater as the supply voltage ( $V_{\rm dd}$ ) decreases because of the bitline keeper on the RBL [22]. In addition to the precharge circuit, it is necessary to prepare a bitline keeper on the RBL in the conventional two-port SRAM. Many MCs connecting to the RBL draw bitline leakage even if they are not selected as a readout bit. Even when a selected MC does not discharge the RBL ("1" readout), the RBL voltage would be decreased by the bitline leakage in such the case if no bitline keeper existed. The bitline keeper compensates this bitline leakage and maintains the voltage level on the RBL during a "1" readout [22]. Otherwise, we cannot distinguish a readout current from the bitline leakage, which is a readout malfunction.

In the 8T SRAM, an inverter circuit is used as a sense amplifier connecting to an RBL. When a datum "1" is read out, the sense amplifier inverter need not pay a delay overhead. In contrast, when a datum "0" is read out, the sense amplifier inverter takes a certain access time by discharging the readout node. The access time in the read operation is therefore determined by the "0" readout. In other words, the logical threshold voltage of the sense amplifier inverter should be adjusted higher to minimize the discharge time.

As process technology has advanced, the supply voltage and threshold voltage of transistors have decreased. Because the low threshold voltage increases the bitline leakage, we must increase the bitline keeper; then pay area overhead. The large bitline keeper imparts a negative influence on the readout time as well. To make matters worse, the delay overhead increases as the supply voltage decreases.

8T dual-port SRAM: (a) a schematic and (b) waveforms in a read operation.

Figure 3.1(b) simplified operation waveforms in read cycles in the conventional 8T precharge-type SRAM. A precharge scheme is adopted and an RBL must be precharged to a supply voltage by the start time of a clock cycle. Therefore, a charge-discharge power is consumed on the RBL when "0" is read out. In contrast, no power is consumed when "1" is read out because the RBL keeps the supply voltage level and we need not precharge the RBL.

In an earlier study, which examined saving the charge-discharge power on a read bitline, a majority logic circuit and data-bit reordering were accommodated to write as many "1"s as possible [23] (the prior SRAM is designated as 'MJ SRAM' in this chapter). The MC structure in the MJ SRAM is the same as the conventional 8T SRAM although the read and write circuits differ. Input data comprising eight pixels are digit (from the most-significant-bit reordered into groups group least-significant-bit group); then a flag bit is appended to each group. The "0" data are inverted to "1"s by the majority logic circuit if the number of "0"s in a group is more than that of "1"s. Thereby, we can maximize the number of "1"s in the input data. The inversion information ("1" signifies inversion) is stored in the additional flag bit. In a read cycle, the group data are inverted if a flag bit is true. Then they are put back in the original order so that it is possible to read out the original data. This mechanism reduces the power of the read bitline because we can statistically increase the probability that "1" is read where no power is dissipated.

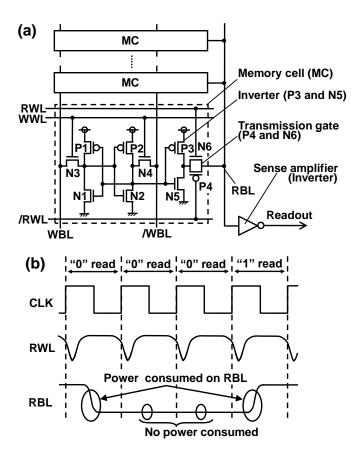

For further power reduction, we propose a novel non-precharge-type SRAM (10T-S SRAM) in this chapter [24]. The 10T-S SRAM reduces the bitline power in both cases in which consecutive "0"s are read out and consecutive "1"s are read out because no precharge circuit exists on bitlines. The charge—discharge power is consumed only when a readout datum is changed. In contrast, in a conventional 8T SRAM, a consecutive-"0" readout requires large amounts of bitline power. In addition to the power reduction with the consecutive readout, the 10T-S SRAM operates in a shorter cycle time because a precharge period is not required. Furthermore, this structure obviates the bitline keeper, which improves operation in the low-voltage region. In comparison to the MJ SRAM, the 10T-S SRAM eliminates the flag bit that causes the power overhead.

# 3.3 10T Single-End SRAM (10T-S SRAM)

To improve the 8T SRAM, we have proposed a 10T non-precharge SRAM with a single-end read bitline [24–26], as depicted in Fig. 3.2(a) (10T-S SRAM). Two pMOS transistors are appended to the 8T SRAM cell, which engenders the combination of the conventional 6T single-port MC, an inverter, and a transmission gate. The additional signal (/RWL) is an inversion signal of a read wordline (RWL); it controls the additional pMOS transistor (P4) at the transmission gate. The additional pMOS transistor (P4) increases a RBL capacitance compared to the conventional 8T SRAM. Although the RWL and /RWL are asserted and the transmission gate is on, a stored node is connected to an RBL through the inverter. It is not necessary to prepare a precharge circuit because the inverter can charge—discharge the LRBL independently. No precharge circuit exists on either differential write bitline (WBL and /WBL) because they are dedicated for a write port.

Fig. 3.2 10T SRAM with a single-end read bitline (10T-S SRAM): (a) a schematic and (b) waveforms in read operation.

Figure 3.2(b) depicts operation waveforms in the 10T-S SRAM in read cycles. A charge–discharge power on the RBL is consumed only when the RBL is changed. Consequently, no power is dissipated on the RBL if an upcoming datum is the same as the previous state. The 10T-S SRAM is suitable for a real-time video image that has statistical similarity [24–26].

The 10T-S SRAM theoretically reduces the power on the RBL to half that of a conventional 8T SRAM in a read operation if the readout data are random and the bitline capacitance is equal. The transient probability in a sequence of random data is 50% in the 10T-S SRAM; in the 8T SRAM, the number of charge—discharge times becomes one as an expected value. In the 8T SRAM, a charge and discharge pair takes place when "0" is read out. The RBL power is thereby reduced to about 50% in the read operation used for the 10T-S SRAM.

Charging-discharging times on an RBL in a 10T-S SRAM when a sense amplifier drive transistor width is changed at the SS corner (25°C).

In the 10T-S SRAM, an inverter is connected to an RBL as a sense amplifier, just as with the 8T SRAM. The logical threshold voltage of the sense amplifier inverter should be adjusted in the middle, considering the charge-discharge on an RBL and maintaining their balance. Figure 3.3 shows the charging-discharging times on the RBL in the 10T-S SRAM when the drive transistor (nMOS) width in the sense amplifier inverter is changed. In the figure, the load transistor (pMOS) width in the sense amplifier is set to the minimum size—0.1 µm for the middle logical threshold voltage—because in the 10T-S SRAM, the drive power of the nMOS transistor N5 (see Fig. 3.2(a)) is stronger than that of the pMOS transistor P3 (see Fig. 3.2(a)) when the transistor sizes are the same. Therefore, the charging time is longer than the discharging one on the RBL. When the drive transistor width in the sense amplifier inverter is 0.4 µm, the propagation delay of the sense amplifier inverter becomes the shortest. Consequently, Fig. 3.3 indicates that the optimum ratio of the transistor widths between nMOS and pMOS in the sense amplifier inverter is four. In this chapter, we used 0.4-µm nMOS and 0.1-µm pMOS for the sense amplifier inverter of 10T-S SRAM. For large-capacity SRAM, in terms of reducing the threshold-voltage  $(V_{th})$  variation, the minimum size transistor should be avoided for use as a sense amplifier because the deterioration on a sense amplifier affects the access time for all memory cells connected to it.

## 3.4 10T Differential SRAM (10T-D SRAM)

Figure 3.4(a) presents a schematic of a 10T SRAM with differential read bitlines (RBL and /RBL) [27] (10T-D SRAM). Two nMOS transistors (N5 and N7) for the RBL and the other additional nMOS transistors (N6 and N8) for /RBL are appended to the traditional 6T SRAM. As is true also for the 8T SRAM, precharge circuits must be implemented on the RBL and /RBL.

Figure 3.4(b) depicts operation waveforms in the 10T-D SRAM in read cycles. The differential bitlines must be precharged to VDD by the start time of a clock cycle. To sense a difference voltage between the RBL and /RBL correctly, the difference voltage must be, at least, more than 50 mV [28–30].

Fig. 3.4 10T SRAM with differential read bitlines (10T-D SRAM): (a) a schematic and (b) waveforms in read operation.

Figure 3.5 presents an illustration of a sense amplifier circuit for the 10T-D SRAM.

This is a commonly used latch type sense amplifier. The use of low-threshold-voltage transistors (P3-P5 and N3-N5) enables sensing of the differential voltage faster, although the precise control of the sense enable signal is needed [31] because timing generator circuits are easily affected by the  $V_{\rm th}$  variation. Consequently, the differential voltage when the sense enabled signal is enabled is varied, which varies the readout power as well.

Fig. 3.5 Circuit schematic of a sense amplifier in the 10T-D SRAM.

# 3.5 Reducing the Number of Charge/Discharge Times

### 3.5.1 Application to Video Images

In the 10T-S SRAM, the charge-discharge power consumed on the LRBLs is proportional to the number of times that a datum flips (i.e., the number of transitions: "0" to "1" and "1" to "0") along the time axis. Therefore, we can exploit the 10T-S SRAM for video processing as well as the MJ SRAM because adjacent pixels have strong correlation with one another in a video image.

In the H.264 codec, the YUV format is adopted as a pixel datum. An example is presented in Fig. 3.6. One pixel comprises an 8-bit luma (Y signal) and 4-bit chroma (U and V signals). In this chapter, only luma data are considered. The most significant bits (MSBs) in consecutive data tend to be lopsided to either "0" or "1" with high probability, while in the least significant bits (LSBs), the values of the bits are random. In other words, the correlation becomes stronger in a more significant bit, which is well exploited in the MJ SRAM.

Fig. 3.6 Example of H.264 image data and its mapping onto eight LRBLs.

As described in Section 3.3, the power reduction on the LRBLs is theoretically expected because of the non-precharge scheme, even if input data are random. Furthermore, additional power reduction is promising because image data are lopsided to "0"s or "1"s with higher probability in a more significant digit. We exploit these characteristics in the 10T-S SRAM to reduce the LRBL power as well as the MJ SRAM.

### 3.5.2 Block Size Optimization

In this subsection, we discuss the optimum data mapping that uses the spatial correlation in an image. In a video image, the correlations among local pixels are presumed to be different in the vertical and lateral directions. It is important to determine the block size mapped onto an LRBL because a scan path affects the effective use of the spatial correlation and power. Assuming an H.264 encoder, we made a simulation under the condition shown in Table 3.1 to fix the block size. In the simulation, statistic analyses were conducted with the original images and reconstructed images, extracted from ten high-definition test sequences shown in Fig. 3.7: 'Bronze with Credit', 'Building along the Canal', 'Church', 'Intersections', 'Japanese Room', 'European Market', 'Yachting', 'Street Car', 'Whale Show', and 'Yacht Harbor'. The original image is encoded. Then its reconstructed image is generated in a local decoding loop. It is then used for motion estimation and motion compensation. The encoding process is depicted in Fig. 3.8.

| Profile      | Main profile             |

|--------------|--------------------------|

| Frame rate   | 30 fps                   |

| Bit rate     | 7.5 Mbps                 |

| Search range | $\pm 128 \times \pm 128$ |

| Symbol mode  | CABAC                    |

| JM version   | 9.8                      |

Table 3.1 Simulation conditions in the H.264 encoder.

Fig. 3.7 HD video sequences. Each sequence comprises 100 frames and  $1920 \times 1024$  pixels.

Figure 3.6 portrays an example of the block size and its scan path. We set the number of pixels in a block to 256 because the search range is  $\pm 128 \times \pm 128$  in the H.264 encoder and a burst access over 256 pixels is possible if a full-search algorithm is considered. Therefore, in the simulation, a pixel block ( $W \times H$  pixels) has 256 pixels. The scan path from the first pixel to the W-th pixel is mapped onto eight LRBLs.

Fig. 3.8 H.264 encoding process.

Figure 3.9 presents a comparison of the transition possibilities (the normalized quantities of charge—discharge times) on an LRBL between the conventional 8T SRAM, MJ SRAM, and proposed 10T-S SRAM when the block size is changed. The values are the averages of 10 sequences. For both the original image and reconstructed image, the

block size of  $256 \times 1$  pixels is optimum in terms of power reduction. The graph indicates that the 10T-S SRAM saves 73% of a dynamic power on an LRBL compared to the conventional 8T SRAM when the original image is read out.

Fig. 3.9 Transition possibilities (the normalized quantities of charge–discharge times) on an LRBL between the conventional 8T, MJ, and proposed 10T-S SRAMs when a block size is changed.

The maximum power saving is achieved when a reconstructed image that has a stronger correlation than the original image is considered. The saving factor is extended to 81% compared to the conventional 8T SRAM, which indicates that the statistical characteristic of the reconstructed image is well exploited. It can be said that the proposed 10T-S SRAM is suitable for a real-time video codec such as MPEG2, MPEG4, and H.264 that require a large-capacity reconstructed-image memory.

# 3.6 Design in 90-nm Process Technology

#### 3.6.1 Cell and Macro Layouts

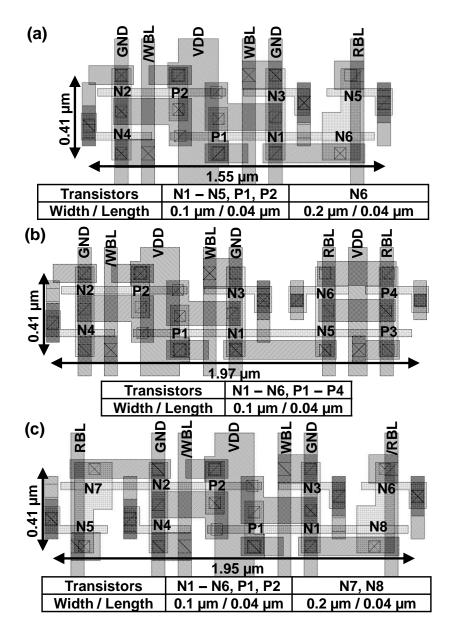

Figure 3.10 depicts the layout patterns of conventional and proposed MCs in a 90-nm process technology. In addition, the transistor sizes are shown in this same figure.

Figure 3.10(a) portrays the conventional 8T MC layout. The schematic is portrayed in Fig. 3.1(a). The cell area is  $3.15 \times 0.76~\mu m^2$ , which is the smallest of the three. Because this memory cell frees an SNM, the driver transistors' (N1, N2) width can be minimized; then the load transistors' (P1, P2) length can be enlarged to extend the write margin. Therefore, the operation margin is sufficient at the nominal supply voltage of 1.0~V.

Fig. 3.10 Layouts of (a) the conventional MC, (b) the proposed MC without shared WL structure, and (c) the proposed MC with a shared WL structure.

Fig. 3.11 Shared WL structure.

Figure 3.10(b) shows the proposed 10T-S MC layout. The schematic is portrayed in Fig. 3.2(a). The cell area is  $3.70 \times 0.935~\mu m^2$ . This MC, at 0.935  $\mu m$ , is higher than the conventional one (0.76  $\mu m$ ) because the 10T-S MC requires three wordlines: WWL, RWL, and /RWL. The minimum metal pitch to align these three wordlines is larger than a transistor pitch. Therefore, the height of this 10T-S MC is restricted by the metal lines. The coupling noise between the wordlines would be larger than that in the conventional one because the metal pitch must be minimized for a small MC area.

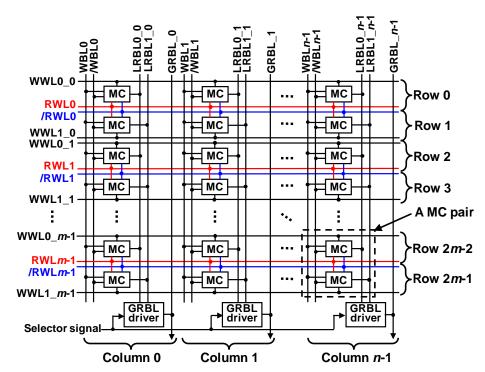

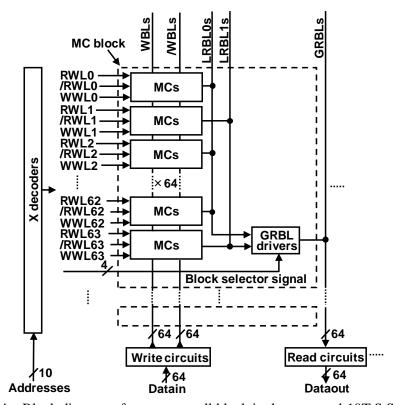

We propose a shared WL structure to shrink the area of the proposed MC. Figure 3.11 presents the shared WL structure. A pair of a top and bottom MCs shares an RWL and its complementary signal: /RWL. Instead, two LRBLs must be interconnected in each column, as the figure shows. For instance, when RWL0 and /RWL0 are asserted, the MCs in Row 0 and Row 1 become active. The data stored in Row 0 are read out to the LRBL0 group (LRBL0\_0, ..., LRBL0\_n-1), and the data stored in Row 1 are read out to the LRBL1 group (LRBL1\_0, ..., LRBL1\_n-1). Consequently, the additional drivers are prepared to choose which data are read out to the global read bitlines (GRBLs); the GRBL driver selects either LRBL0 group or the LRBL1 group using the selector signal.

Figure 3.10(c) shows the layout of an MC pair with the shared WL structure. The cell area is  $3.955 \times 0.76 \,\mu\text{m}^2$ . By introducing the shared WL structure, the 10T-S MC can be

designed to be the same height as the conventional 8T MC because the RWL and the /RWL are shared by each MC pair. Therefore, the quantities of RWLs and /RWLs are reduced to a half that of the WWLs, which reduces the MC area overhead of the proposed 10T-S SRAM. Although, Fig. 3.10(b) shows that the MC height is restricted by the metal wordlines, the MC height with the shared wordline structure is restricted by the transistor pitch as depicted in Fig. 3.10(c). Therefore, the metal pitch of the wordlines in Fig. 3.10(c) is relaxed. The coupling noise between the wordlines can be reduced [32].

In the 10T-S MC, all transistors are aligned on two lines, so this MC layout improves lithographic quality and is better in terms of manufacturability than the MC without the shared wordline structure. Furthermore, no bent polysilicon pattern was found in the proposed 10T-S MC, which might reduce variations in transistors' finished dimensions. In the 10T-S MC pair, because each bitline is shielded by a VDD line or GND line, it is tolerant of coupling noise [32].

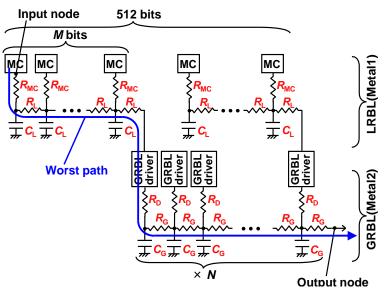

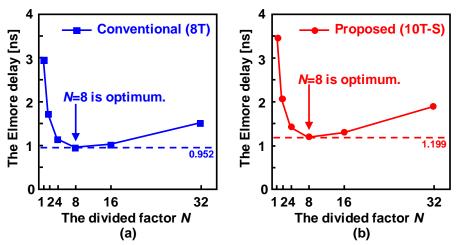

### 3.6.2 Delay Model of Read-Bitline RC Trees

In our proposed 10T-S SRAM, because of the additional pMOS transistor, MCs can fully charge—discharge each LRBL. However, the MC transistors are too small to charge—discharge each long RBL quickly. Therefore, in our design, we adjust the length of the RBLs which are charged—discharged by MCs in the hierarchical read-bitline structure (double-bitline structure: The LRBLs and GRBLs). The hierarchical read-bitline structure is effective to avoid a speed overhead of a single-bitline scheme, which is applicable to the 10T-S SRAM [21]. In our proposed shared WL structure, when an address is asserted, the quantities of the active MCs differ in write and read operations because, only in the read operation, the wordlines are shared. The hierarchical read-bitline structure also solves this addressing problem.

We model the BL structure to minimize a propagation delay from the LRBLs to the GRBLs. Elmore delays are obtainable node-by-node on the bitline: all resistances and all capacitances from the input node to the output node. Figure 3.12 shows a  $\pi$ -type RC model of the SRAM read port when the total number of bits on each GRBL is set to 512 and when each GRBL is divided into LRBLs by a factor N (N is a natural number) [33]. The respective widths of the LRBL and GRBL using the metal-1 and metal-2 lines are

set to 0.14 µm.

Fig. 3.12 A  $\pi$ -type RC model of the SRAM read port.

In Fig. 3.12, M,  $C_L$ ,  $C_G$ ,  $R_L$ ,  $R_G$ ,  $R_{MC}$ , and  $R_D$  respectively represent the number of bits on each LRBL, the capacitance of the LRBL per bit, the capacitance of the GRBL per 512/N bits, the resistance of the LRBL per bit, the resistance of the GRBL per 512/N bits, the output resistance of each MC to the LRBL, and the output resistance of each GRBL driver.

Table 3.2 Values of M, CL, CG, RL, RG, RMC, and RD, as obtained using the ASPLA 90-nm process parameters.

|                               | Conventional 8T       | Proposed 10T SRAM        |

|-------------------------------|-----------------------|--------------------------|

|                               | SRAM                  | with shared WL structure |

| M [bits]                      | 512 / N               | 256 / N                  |

| $C_{ m L}  [{ m fF}]$         | 0.408                 | 0.748                    |

| $C_{\mathrm{G}}$ [fF]         | $0.0546 \times M + 2$ | $0.1248 \times M + 2$    |

| $R_{ m L}\left[\Omega ight]$  | 0.0789                | 0.1580                   |

| $R_{ m G}\left[\Omega ight]$  | $0.0789 \times M$     | $0.1580 \times M$        |

| $R_{ m MC}\left[\Omega ight]$ | $1.2 \times 104$      | $1.5 \times 104$         |

| $R_{ m D}\left[\Omega ight]$  | $2.5 \times 103$      | $2.5 \times 103$         |

Table 3.2 presents the values of M,  $C_L$ ,  $C_G$ ,  $R_L$ ,  $R_G$ ,  $R_{MC}$ , and  $R_D$ , obtained using the ASPLA 90-nm process parameters. The parameter of  $C_L$  presents the sum of a wiring capacitance and a drain capacity in an MC. The drain capacitance depends on a MC topology. When considered the conventional 8T MC in Fig. 3.1(a), the drain capacitance corresponds to the drain capacity of N6 only. Similarly, when considering the proposed

10T-S MC in Fig. 3.2(a), the drain capacitance is the sum of N6 and P4, so the  $C_L$  in the proposed MC is larger than that in the conventional 8T MC. The  $C_G$  parameter presents a sum of the wiring capacitance of the GRBLs and the drain capacitance of the GRBL driver. In this model, the drain capacity of the GRBL driver circuits equals 2 fF. The  $R_{\rm MC}$  and  $R_{\rm D}$  are obtained respectively by analyzing the transistors characteristic that connected to the LRBL and GRBL.

When the total number of bits on each GRBL and each LRBL is set to 512 and M, respectively, and when each GRBL is divided into LRBLs by a factor, N, the Elmore delay  $\tau_{\text{Elmore}}(M, N)$  is expressed as shown below [34].

$$\tau_{\text{Elmore}}(M,N) = R_{\text{MC}}(M \cdot C_{\text{L}} + N \cdot C_{\text{G}}) + R_{\text{L}} \sum_{k=0}^{M-1} \{k \cdot C_{\text{L}} + N \cdot C_{\text{G}}\}

+ R_{\text{D}} \cdot N \cdot C_{\text{G}} + R_{\text{G}} C_{\text{G}} \sum_{k=0}^{N-1} k

= R_{\text{MC}}(M \cdot C_{\text{L}} + N \cdot C_{\text{G}}) + R_{\text{L}} \left\{ \frac{M(M-1)}{2} \cdot C_{\text{L}} + M \cdot N \cdot C_{\text{G}} \right\}

+ R_{\text{D}} \cdot N \cdot C_{\text{G}} + R_{\text{G}} \cdot \frac{N(N-1)}{2} \cdot C_{\text{G}}

= \frac{1}{2} R_{\text{L}} C_{\text{L}} \cdot M^{2} + \left( R_{\text{MC}} C_{\text{L}} - \frac{1}{2} R_{\text{L}} C_{\text{L}} \right) \cdot M + \frac{1}{2} R_{\text{G}} C_{\text{G}} \cdot N^{2}

+ \left( R_{\text{MC}} C_{\text{G}} + R_{\text{D}} C_{\text{G}} - \frac{1}{2} R_{\text{G}} C_{\text{G}} \right) \cdot N + R_{\text{L}} C_{\text{G}} \cdot M \cdot N$$

(3.1)