PDF issue: 2024-08-31

# A Performance Study on ATLAS Level1 Endcap Muon Trigger using 7TeV/c collision data

#### 早川,俊

```

(Degree)

博士 (理学)

(Date of Degree)

2012-03-25

(Date of Publication)

2012-04-16

(Resource Type)

doctoral thesis

(Report Number)

甲5577

(URL)

https://hdl.handle.net/20.500.14094/D1005577

```

※ 当コンテンツは神戸大学の学術成果です。無断複製・不正使用等を禁じます。著作権法で認められている範囲内で、適切にご利用ください。

### 博士論文

A Performance Study on ATLAS Level1 Endcap Muon Trigger using 7TeV/c collision data

ATLAS 実験初段エンドキャップミューオントリガーの、

7TeV/c における陽子衝突実験の結果に基づく

性能に関する研究

神戸大学大学院理学研究科 早川 俊

平成 24 年 1月

# **Contents**

| 1 | Intr | oductio | n                                     | 3  |

|---|------|---------|---------------------------------------|----|

| 2 | The  | LHC     |                                       | 5  |

|   | 2.1  | The Ll  | HC Accelerator                        | 5  |

|   | 2.2  | Lumin   | osity                                 | 7  |

|   | 2.3  | Particl | e Production Rates                    | 7  |

| 3 | Phys | sics Mo | tivation at the ATLAS Experiment      | 9  |

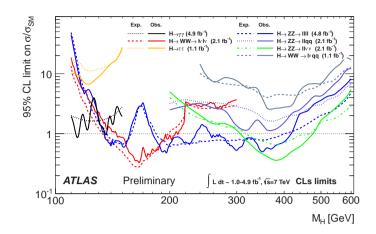

|   | 3.1  | Standa  | ard Model Higgs                       | 10 |

|   |      | 3.1.1   | Higgs Mechanism                       | 10 |

|   |      | 3.1.2   | Experimental Constraint of Higgs Mass | 13 |

|   |      |         | 3.1.2.1 Higgs Boson Production        | 13 |

|   |      | 3.1.3   | Higgs Boson Decay and Search at ATLAS | 14 |

| 4 | The  | ATLAS   | S                                     | 19 |

|   | 4.1  | Defini  | tion of Coordinates                   | 20 |

|   | 4.2  | DAQ S   | System                                | 21 |

|   |      | 4.2.1   | Overview of the Trigger System        | 21 |

|   | 4.3  | Inner l | Detector                              | 24 |

|   |      | 4.3.1   | Silicon pixel vertex detector (PIXEL) | 24 |

|   |      | 4.3.2   | Semi Conductor Tracker (SCT)          | 25 |

|   |      | 4.3.3   | Transition Radiation Tracker (TRT)    | 26 |

|   | 4.4  | Calori  | meters                                | 26 |

|   | 4.5  | Muon    | Spectrometer                          | 27 |

| 5 | Mud | on Spect         | trometer                                             | 29 |

|---|-----|------------------|------------------------------------------------------|----|

|   |     | 5.0.1            | Measurement Method of Muon                           | 30 |

|   | 5.1 | Precisi          | on Chamber                                           | 31 |

|   |     | 5.1.1            | Monitored Drift Tube                                 | 31 |

|   |     | 5.1.2            | Cathode Strip Chamber                                | 33 |

|   | 5.2 | Trigge           | r Chamber                                            | 34 |

|   |     | 5.2.1            | Resistive Plate Chamber                              | 34 |

|   |     | 5.2.2            | Thin Gap Chamber                                     | 35 |

|   | 5.3 | Toroid           | al Magnet                                            | 38 |

|   | 5.4 | LVL1             | Muon Trigger                                         | 38 |

|   |     | 5.4.1            | Requirements of LVL1 Muon Trigger                    | 40 |

|   |     | 5.4.2            | Muon to Central Trigger Processor Interface (MuCTPI) | 40 |

| 6 | End | cap Mu           | on Trigger                                           | 41 |

|   | 6.1 | Overvi           | iew of LVL1 Endcap Muon Trigger                      | 41 |

|   |     | 6.1.1            | Big Wheel                                            | 42 |

|   |     | 6.1.2            | Small Wheel                                          | 44 |

|   | 6.2 | Impler           | mentation on the TGC Electronics System              | 47 |

|   |     | 6.2.1            | ASD                                                  | 47 |

|   |     | 6.2.2            | Patch Panel                                          | 49 |

|   |     | 6.2.3            | Slave Board (SLB) and 2 station coincidence          | 50 |

|   |     | 6.2.4            | High-Pt board (HPT) and 3 station coincidence        | 54 |

|   |     | 6.2.5            | Sector Logic , R- $\phi$ coincidence                 | 54 |

|   |     | 6.2.6            | SSW                                                  | 57 |

|   |     | 6.2.7            | TTC                                                  | 57 |

| 7 | The | Sector 1         | Logic                                                | 58 |

|   | 7.1 | Requir           | ments                                                | 58 |

|   | 7.2 | 7.2 Board Design |                                                      |    |

|   |     | 7.2.1            | Main FPGA                                            | 60 |

|   |     | 7.2.2            | G-Link input                                         | 61 |

|   |     | 723              | Glink Monitor FPGA                                   | 62 |

|     |         | 7.2.3.1 Recovering Procedure             | 62 |

|-----|---------|------------------------------------------|----|

|     | 7.2.4   | LVDS Output                              | 62 |

|     | 7.2.5   | SLB and Cat6 LVDS in/out                 | 63 |

|     | 7.2.6   | VME Controller CPLD                      | 63 |

|     | 7.2.7   | TTC input                                | 64 |

|     | 7.2.8   | NIM output                               | 65 |

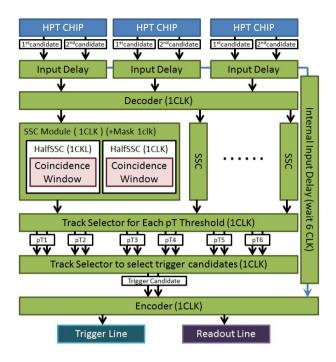

| 7.3 | Algori  | thm of Main Trigger Process              | 65 |

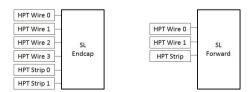

|     | 7.3.1   | HPT Input Information                    | 66 |

|     | 7.3.2   | Input Delay                              | 67 |

|     | 7.3.3   | Decoder                                  | 67 |

|     |         | 7.3.3.1 Endcap HPT strip bug             | 67 |

|     | 7.3.4   | Sub Sector Cluster (SSC)                 | 68 |

|     |         | 7.3.4.1 Half-SSC                         | 68 |

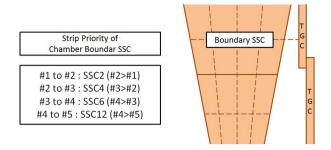

|     |         | 7.3.4.2 Handling about Chamber Boundary  | 68 |

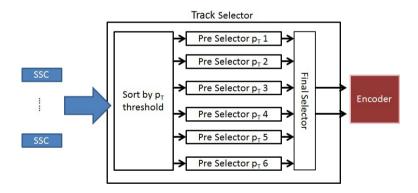

|     | 7.3.5   | Track Selector                           | 69 |

|     |         | 7.3.5.1 Pre-Selector                     | 69 |

|     |         | 7.3.5.2 Final-Selector                   | 70 |

|     | 7.3.6   | Encoder                                  | 70 |

|     |         | 7.3.6.1 BCID                             | 70 |

|     | 7.3.7   | Internal Input Delay                     | 70 |

| 7.4 | Impler  | nentation                                | 71 |

|     | 7.4.1   | Verilog HDL                              | 71 |

|     | 7.4.2   | LUT                                      | 71 |

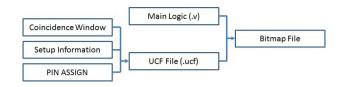

|     | 7.4.3   | Implementation of the Coincidence Window | 72 |

|     |         | 7.4.3.1 Database File                    | 72 |

|     | 7.4.4   | DBtoUCFconverter                         | 73 |

|     | 7.4.5   | BitfileMaker                             | 73 |

| 7.5 | Other 1 | Functionalities in Main Process FPGA     | 74 |

|     | 7.5.1   | LUT Version Reader                       | 74 |

|     | 7.5.2   | Input Checker                            | 75 |

|     | 753     | Scaler                                   | 75 |

|   |      | 7.5.4   | Mask                                    | 76        |

|---|------|---------|-----------------------------------------|-----------|

|   | 7.6  | Valida  | tion of Sector Logic                    | 76        |

|   |      | 7.6.1   | Validation of Sector Logic to Front End | 77        |

|   |      | 7.6.2   | Validation of Front End to Sector Logic | 78        |

| 8 | Perf | ormano  | ee Studies                              | <b>79</b> |

|   | 8.1  | Coinci  | dence Window                            | 79        |

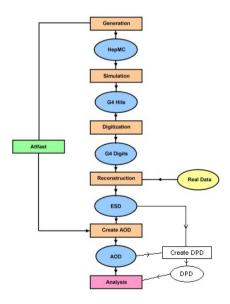

|   |      | 8.1.1   | ATLAS Simulation Scheme                 | 79        |

|   |      | 8.1.2   | Production of Coincidence Window        | 81        |

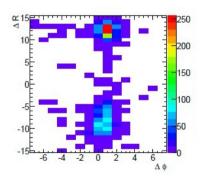

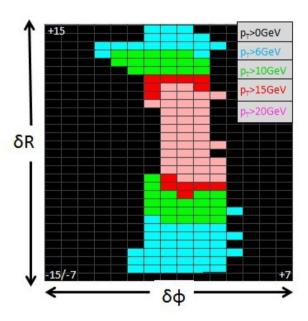

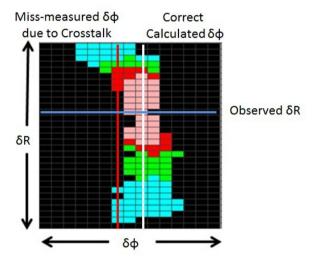

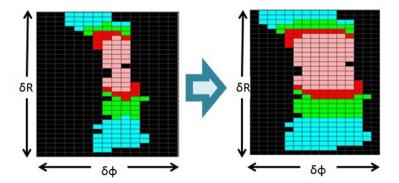

|   | 8.2  | Effects | s of TGC crosstalk                      | 82        |

|   |      | 8.2.1   | Origin of Cross Talk                    | 83        |

|   |      | 8.2.2   | Declustering Rule                       | 84        |

|   | 8.3  | Effect  | of Dead Chambers                        | 84        |

|   | 8.4  | Measu   | rement of Efficiencies                  | 85        |

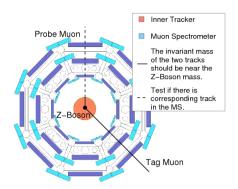

|   |      | 8.4.1   | Combined Muon                           | 85        |

|   |      | 8.4.2   | Tag and Probe Method                    | 86        |

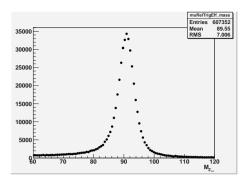

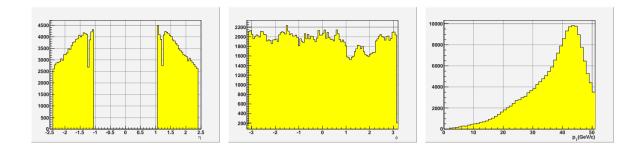

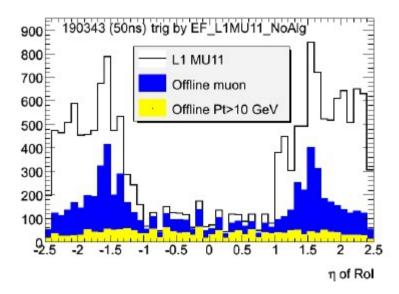

|   |      |         | 8.4.2.1 Distributions of Probe Muons    | 89        |

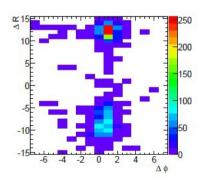

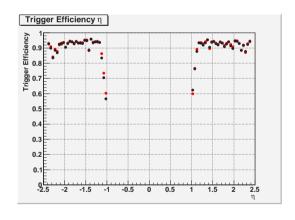

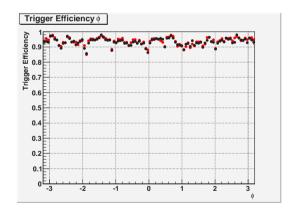

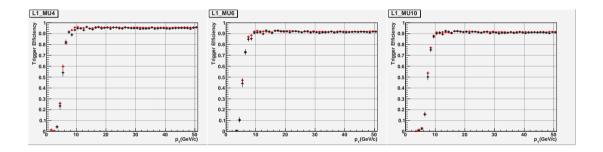

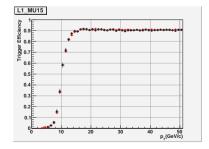

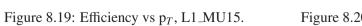

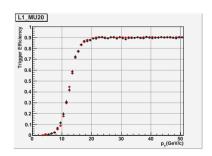

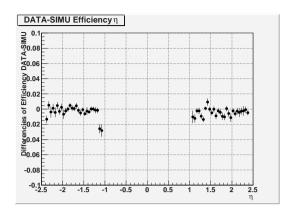

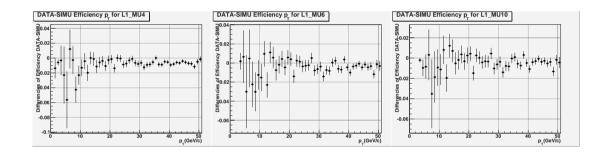

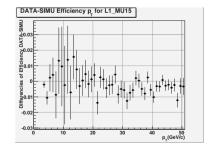

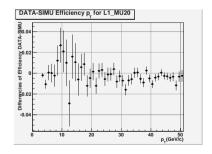

|   |      |         | 8.4.2.2 Trigeger Efficiency             | 91        |

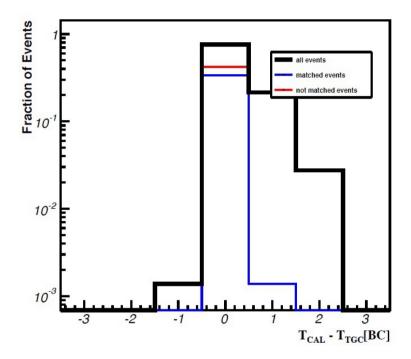

|   |      | 8.4.3   | Trigeger Timing                         | 94        |

|   | 8.5  | Fake tı | rigger                                  | 94        |

| 9 | Sum  | ımary   |                                         | 97        |

### Chapter 1

### Introduction

The LHC (Large Hadron Collider)[5] is the largest proton-proton collider overall the world. With 27km circumference of the LHC, this collider can accelerate proton beams upto 7TeV with a designed feature (14TeV collision at Center of Mass system). Experiments at the LHC have started from 2009 with 450 GeV beam energy, and now the beam energy reaches 3.5TeV. ATLAS (A Toroidal Lhc Apparatus)[9], whose detector is installed in one of collision points, is one of experimental project at the LHC. The main purpose of ATLAS is to explore undiscovered particles and new physics phenomena. One of the most important goal is to find the Higgs boson. Standard Model[2][3] predicts the existence of Higgs which has not found yet, in spite of extensive searches by many experiments. In the Standard Model, Higgs takes a role of giving mass to all particles, quarks, leptons and gauge bosons. Higgs is predicted to decay into known particles. Some decay channels contain the high transverse momentum muons in the final state. Muon is a lepton and muon identification is easier than other signals. Measurement system of muon is one of important ingredients of the Higgs search at the LHC.

In the LHC, the rate of proton-proton interaction is estimated to be 1GHz at the design luminosity. On the other hand, the rate of Higgs production is estimated to be about  $10^{-1}$ Hz. We should pick up interesting phenomena which are buried in large number of backgrounds. The trigger system is equipped with ATLAS data taking scheme to pick up interesting events. Three staged processing is adopted for the trigger system, to reduce recording rate to about 200Hz. The first stage of trigger system is named Level 1 (LVL1) Trigger. The LVL1 Trigger is performed by customized electronics for deadtime-less processing within 2.5 us of latency. The LVL1 Trigger consists of calorimeter trigger and muon trigger. An important role of LVL1 Muon Trigger is to find the high transverse momentum

muons. Muon trigger consists of the barrel and endcap parts. Kobe university have been contributed in the development of ATLAS LVL1 Endcap Muon Trigger System; construction of detectors, design of the trigger scheme and electronics, and development of software.

This thesis will present the performance study of LVL1 Endcap Muon Trigger at the center of mass 7TeV. At first, a brief descripton on LHC and ATLAS experiment will be described. Next, the LVL1 Endcap Muon Trigger will be explained. Especially the details of electronics to determine the trigger candidate will be presented. After that, an study of the performance of LVL1 Endcap Muon Trigger is described. Adjustments of the trigger logic, trigger efficiency, and timing studies will be presented. At the end of this thesis, a summary will be presented, and the contributions of LVL1 Endacp Muon Trigger in ATLAS will be demonstrated.

# Chapter 2

# The LHC

This chapter describes about the Large Hadron Collider (LHC) and introduces their main experiments. LHC is designed for a proton-proton collisions with 14 TeV of center of mass system (CM) energy, which is the highest energy all over the world. Its design luminosity is  $10^{34} cm^{-2} sec^{-1}$ . Bunch crossing rate is 25 ns and total rate of proton-proton interaction is up to  $10^9$  per second. Then, LHC can reach at unexplored energy region for new physics studies.

#### 2.1 The LHC Accelerator

The LHC is a synchrotron with 26.7 km circumference, and each bunch of protons is accelerated to 7 TeV/c. Super Proton Synchrotron (SPS) is the injector for the LHC and accelerates 2 GeV/c protons from Proton Synchrotron (PS) to 450 GeV/c. The beamline of the LHC is composed mainly of super-conducting NbTi bending magnets [5] and quadruples for the beam optics, and accelerating cavities. These super-condicting dipole magnets are placed along two separated beamlines and produce magnetic fields of 8.4 T in vertical direction. There are four collision points at the LHC, where the following detectors are placed.

- ATLAS (A Toroidal LHC ApparatusS)

- CMS (Compact Muon Solenoid) [6]

- LHCb [8]

- ALICE (A Large Ion Collider Experiment) [7]

| Main Ring Circumference | 26658.87m                   |

|-------------------------|-----------------------------|

| Proton Energy           | 7.0 TeV                     |

| Injection Energy        | 450 GeV/c                   |

| Bunch Length            | 77mm                        |

| Beam Radius             | 15.9 μm                     |

| Luminosity Lifetime     | 10 hours                    |

| Number of Protons       | $1.1 \times 10^{11}$ /bunch |

| Bunch Interval          | 24.95 ns                    |

| Beam Crossing Angle     | $300\mu \mathrm{rad}$       |

Table 2.1: The Design Parameters of LHC

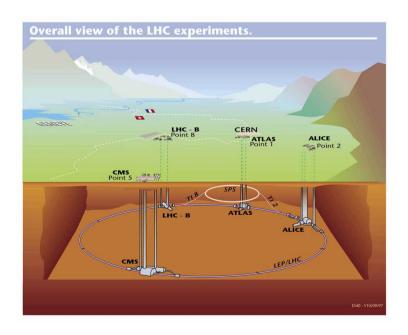

ATLAS and CMS are general purpose detectors, LHCb is specialized for b-physics and ALICE is for heavy ion collision (1PeV Pb-Pb collision at the maximum energy). Locations of these detectors with respect to the proton rings are shown in Fig 2.1. The design parameters of LHC is listed on Table 2.1.

Figure 2.1: Schematic view of the LHC accelerator complex

#### 2.2 Luminosity

One of the important parameters of a collider is the luminosity L. For a physical process with cross-section  $\sigma$ , the event rate  $\frac{dN}{dt}$  is given by

$$\frac{dN}{dt} = \sigma \times L \tag{2-2-1}$$

In the case of a proton collider like the LHC, the luminosity is given by;

$$L = \frac{N_{p1}N_{p2}f_{cross}}{4\pi\sigma_{\chi}^*\sigma_{\chi}^*} \tag{2-2-2}$$

where  $N_{p1}$  and  $N_{p2}$  are the number of protons of colliding bunches and  $f_{cross}$  is the bunch crossing frequency.  $\sigma_x^*$  and  $\sigma_y^*$  are transverse beam size of horizontal(x) and vertical(y) direction at the interaction point respectively and  $\sigma_x^*\sigma_y^*$  gives cross section of the beam. It is clear that increase of  $N_{p1}$ ,  $N_{p2}$ , and  $f_{cross}$ , and decrease of  $\sigma_x^*$ ,  $\sigma_y^*$  result in high luminosity.

At the end of 2011, the peak luminosity have achieved  $6 \times 10^{33} cm^{-2} sec^{-1}$ .

#### 2.3 Particle Production Rates

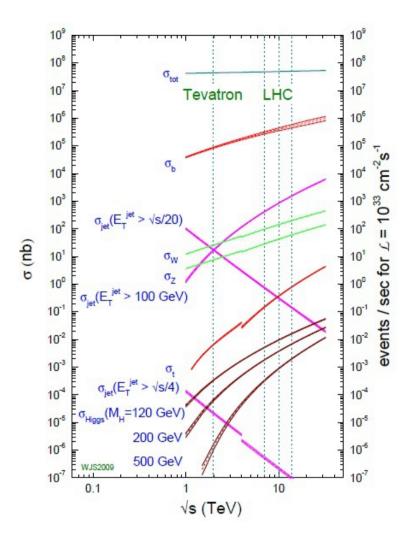

As the proton is a composite particle, 14 TeV of CM energy is distributed to partons inside, quarks and gluons. Not only valence quarks but also the gluons holding them together can interact, and additionally, a whole sea of quark-antiquark pairs are allowed a fleeting existence under the law of quantum mechanics as well. Therefore, mass states up to a few TeV can be created. Figure 2.2 shows the prediction of particle-production cross section for the processes at the LHC and Tevatron together with production rate at the  $10^{33} cm^{-2} sec^{-1}$ . It can be seen that the total cross section is more than ten order of magnitude larger than that of the Higgs production. Therefore, detectors must have capability to handle such an enormous total event rate and distinguish the signals of interest from the other events such as proton-proton inelastic events and minimum bias events (QCD), or backgrounds such as beam halo events and beam gas events.

Figure 2.2: Predicted cross section of proton-proton interaction as CM energy. Vertical axis on left side shows production cross section, right side vertical axis shows event rate. The energy at the Tevatron, Fermilab as well as ones at the LHC are indicated.

### **Chapter 3**

# Physics Motivation at the ATLAS

# **Experiment**

Particle physics deals with the elementary building blocks of matter and their mutual interactions. During the 20th century a theory emerged that successfully describes all known elementary particles and their interactions. The Standard Model incorporates the Glashow-Weinberg-Salam theory [4] of electro week processes and quantum chromodynamics (QCD). Only the gravitational interactions are not included. The Standard Model is a quantum field theory that describes the interactions of spin  $\frac{1}{2}$ point like fermions, whose interactions are mediated by spin 1 gauge bosons. The fermions one, the leptons, and a category of particles that are subjected to the strong interactions, the quarks. Further, they are ordered in three generations of increasing mass, as shown Table 3.1. Each generation consists of two leptons and two quarks, each set with a difference of unit electric charge. The first generation consists of the electron (e), the electron neutrino  $(v_e)$ , the up quark (u), and the down quark (d). All these fermions are stable and are the building blocks of ordinary matter. The up and down quarks form protons and neutrons, which together with the electrons build up the atom and subsequently all form of matters surrounded us. The second generation consists of the muon  $(\mu)$  and muon neutrino  $(\nu_{\mu})$ , the charm quark (c), and the strange quark (s). These have the same propaties as the first generation particles, except that they have larger masses and are not stable. The particles of the third generation, consisting of tau  $(\tau)$ , the tau neutrino  $(\nu_{\tau})$ , the top quark (t) and bottom quark (b), are again heavier. The neutrinos are neutral particles, all other particles are charged. Mass and charges for each particles are also summarized in Table 3.1.

In a simple gauge theory, interactions between fermions occur via the exchange of gauge bosons.

|           | 1st generation                | 2nd generation                  | 3rd generation                      | charge         |

|-----------|-------------------------------|---------------------------------|-------------------------------------|----------------|

| Leptons   | e (0.511 MeV/ $c^2$ )         | $\mu  (106  {\rm MeV}/c^2)$     | $\tau (1.78 \text{GeV}/c^2)$        | -1             |

| Neutrinos | $v_e$                         | $ u_{\mu}$                      | $ u_{	au}$                          | 0              |

| Quarks    | u (1.5-3.3 MeV/ $c^2$ )       | c $(1.16-1.34 \text{ GeV}/c^2)$ | t (169.1-173.3 GeV/c <sup>2</sup> ) | $+\frac{2}{3}$ |

|           | d $(3.5-6.0 \text{ MeV}/c^2)$ | s (70-130 MeV/ $c^2$ )          | b (4.13-4.37 GeV/c <sup>2</sup> )   | $-\frac{1}{3}$ |

Table 3.1: Matter particles of the Standard Model. Values in brackets indicate their masses.

The electromagnetic force is mediated by the photon  $(\gamma)$ . The weak force is mediated via the exchange of either the charged W<sup>+</sup> or W<sup>-</sup> boson or the neutral Z boson. The strong force is mediated by the gluon (g). The photon and the gluon are massless, the mass of W<sup>±</sup> is 80.4 GeV/ $c^2$  and the mass of the Z boson is 91.2 GeV/ $c^2$  [38]. They have been observed in experiments.

While the Standard Model well describes the interactions of the components of matter at the smallest scales ( $10^{-18}$ m) and highest energies (about 200 GeV/ $c^2$ ) accessible to past experiments, there are some problems which have not been solved yet and there need to be theories beyond the Standard Model. In this chapter, especially the Standard Model Higgs [10] is mentioned.

#### 3.1 Standard Model Higgs

In the Standard Model, all gauge bosons are necessarily massless in order to preserve the local gauge invariance of the theory. However,  $W^{\pm}$  and Z bosons have masses. The Higgs mechanism [11][12] provides a possible explanation of the origin of the masses through the spontaneous symmetry breaking of the gauge invariance.

#### 3.1.1 Higgs Mechanism

The Higgs mechanism is an extension of the Goldstone Theorem which states that if a Lagrangian has a global symmetry which is not a symmetry of the vacuum. Then, there must exist one massless boson, scalar or pseudo-scalar, associated to each generator which does not annihilate the vacuum. In the Higgs mechanism, a weak isospin doublet of complex scaler fields  $\phi^0(x)$  and  $\phi^+(x)$  is introduced as;

$$\phi(x) = \begin{pmatrix} \phi^{+}(x) \\ \phi^{0}(x) \end{pmatrix} = \frac{1}{\sqrt{2}} \begin{pmatrix} \phi_{1}(x) + i\phi_{2}(x) \\ \phi_{3}(x) + i\phi_{4}(x) \end{pmatrix}$$

(3-1-1)

It belongs to the  $SU(2)_L \otimes U(1)_Y$  multiplets and along with the scalar potential  $V(\phi)$  represented as;

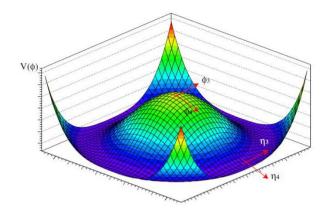

$$V(\phi) = \mu^2 \phi^{\dagger} \phi + \lambda (\phi^{\dagger} \phi)^2, \lambda > 0 \tag{3-1-2}$$

This gives a contribution to the electroweak Lagrangian L as;

$$L_{Higgs} = (D_{\mu}\phi)^{\dagger}(D_{\mu}\phi) - V(\phi), D^{\mu} = \delta^{\mu} - i\frac{g\sigma}{2}\dot{W}^{\mu} - i\frac{g'YB}{2}$$

(3-1-3)

whre  $D_{\mu}$  is the covariant derivative.

The minimum of V corresponding to the ground state of the system (i.e. vacuum) is at  $|\phi|=0$  for the case  $\mu^2 > 0$ , while, for the case  $\mu^2 < 0$ , the minimum shifts to

$$|\phi^2| = \phi\phi^{\dagger} = \frac{1}{2}(\phi_1^2 + \phi_2^2 + \phi_3^2 + \phi_4^2) = -\frac{\mu^2}{2\lambda} = \frac{v^2}{2}$$

(3-1-4)

where v is the vacuum expectation value. This leads to the definition of new field variables,  $\eta_1 = \phi_1$ ,  $\eta_2 = \phi_2$ ,  $\eta_3 = \phi_3$ -v and  $\eta_4 = \phi_4$ , and the potential takes the form as shown in Figure 3.1. They have their origin at an arbitrarily minimum chosen as;

$$|<0|\phi|0>|=rac{1}{\sqrt{2}}\begin{pmatrix} 0\\ v \end{pmatrix}$$

(3-1-5)

The symmetry of the Lagrangian becomes hidden by the choice of a particular minimum. The Lagrangian expressed in the new fields reveals a massive scaler particle  $\eta_2$  of mass  $\sqrt{2\lambda v^2}$ , the Higgs boson H and three massless Goldstone bosons,  $\phi_1$ ,  $\phi_2$ , and  $\eta_3$ . These Goldstone bosons can be removed by applying a unitary gauge transformation to  $\phi(x)$  such that only the real Higgs field remains like;

$$\phi(x) = U\phi(x) = \frac{1}{\sqrt{2}} \begin{pmatrix} 0 \\ v + H(x) \end{pmatrix}$$

(3-1-6)

In this way, the degree of freedom corresponding to the three disappeared Goldstone boson are eaten by the  $W^{\pm}$  and Z fields which acquire mass and a third, longitudinal polarization state. Then,

Figure 3.1: Higgs Potential

the gauge boson masses are generated as;

$$M_W = \frac{gv}{2} \tag{3-1-7}$$

$$M_W = \frac{gv}{2}$$

$$M_Z = \frac{1}{2} \sqrt{g^2 + g'^2}$$

(3-1-7)

(3-1-8)

$$M_{\gamma} = 0 \tag{3-1-9}$$

This massive physical field  $Z_{\mu}$  and the massless one  $A_{\mu}$  are represented using their mixing angle  $\theta_W$  (called the Weinberg angle) as;

$$A_{\mu} = \cos\theta_W B_{\mu} + \sin W_{\mu}^3 \tag{3-1-10}$$

$$Z_{\mu} = -\sin\theta_W B_{\mu} + \cos W_{\mu}^3 \tag{3-1-11}$$

(3-1-12)

where the value  $\theta_W$  satisfies the following equation;

$$\frac{g'}{g} = \tan \theta_W \tag{3-1-13}$$

In addition, the Higgs field couples to the fermion matter fields to generate their masses. The coupling of the Higgs field to a fermion pair is parameterized by an arbitary Yukawa coupling constant  $\lambda_f = \frac{m_f \sqrt{2}}{v}$ , which is different for each fermion and proportional to its mass  $m_f$ . Lepton number conservation is assumed within the SM, giving a diagonal lepton mass matrix. The lack of quark generating number conservation in electroweak interactions means that observed physical mass eigenstates of quarks are not eigenstates of weak isospin. The level of quark mixing is parameterized in terms of the Cabibbo-Kobayashi-Masukawa mixing matrix.

#### 3.1.2 Experimental Constraint of Higgs Mass

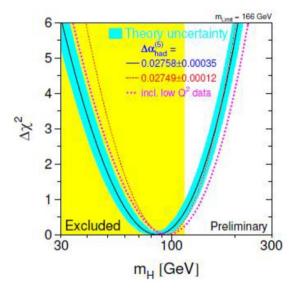

The mas of the Higgs boson remains the only unknown parameter in the Standard Model, and several constraints on its mass have been obtained from past experimental measurements. The most precise bound on the Higgs mass come from the LEP experiments [20]. A Higgs with its mass smaller than 114.4 GeV/ $c^2$  is excluded with a confidence level of 95% by direct searches at LEP. Furthermore an upper limit on its mass can be obtained from a fit to the electroweak results from LEP and SLD. The result of the fit is shown in Figure 3.2. It shows the  $\Delta\chi^2(m_H) = \chi^2_{min}(m_H) - \chi^2_{min}$  as a function of the Higgs mass. The mass region that is excluded by direct searches is indicated by the shaded area. The associated band represents the estimate of the theoretical uncertainty due to higher-order corrections. After a renormalization of the probability content of the region  $m_H > 114 \text{ GeV}/c^2$  to 100%, using the assumption that the prior probability density for  $m_H$  is flag in  $m_H$ , an upper limit of 199GeV/ $c^2$  is obtained with a confidence level of 95%.

Figure 3.2:  $\Delta \chi^2(m_H) = \chi^2_{min}(m_H) - \chi^2_{min}$  as a function of the Higgs mass [13]

#### 3.1.2.1 Higgs Boson Production

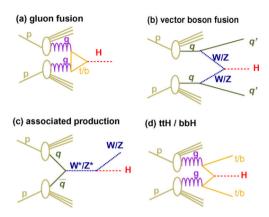

Figure 3.3 shows typical Feynman diagrams of Higgs boson production process for the ATLAS experiment. Details for each process are mentioned below.

•  $gg \rightarrow H$

The gluon fusion processes (Figure 3.3-(a)) proceed primarily through a top quark triangle loop, and is the dominant neutral Higgs boson production mechanism at LHC, with crossections of toughly 200 - 0.1 pb for  $M_{Higgs} = 100 - 1000$  GeV/ $c^2$ . The dependence of the gluon fusion cross section on different parton densities yields roughly an additional 15 % uncertainty in the theoretical prediction.

•

$$gg \rightarrow ggV^*V^* \rightarrow qqH$$

The vector boson fusion (VBF, Figure 3.3-(b)) is a shorthand notation for the full  $qq \rightarrow qqH$  process, where both quarks radiate virtual vector bosons which then annihirate to produce the Higgs boson. The resulting Standard Model cross section are in the range 5 - 0.001 pb for  $M_{Higgs} = 100 - 10000 \, \text{GeV}/c^2$ .

•  $q\bar{q} \rightarrow V^* \rightarrow VH$

The cross section for  $q\bar{q} \to W^\pm H$  (Figure 3.3-(c), summed over both W charge states) reaches values of 2 - 0.001 pb for  $M_{Higgs} = 100$  - 1000 GeV/ $c^2$ . The corresponding  $q\bar{q} \to ZH$  cross section is roughly a factor of two lower over the same Higgs boson mass range. The theoritical uncertainty is estimated to be about 15% from the remaining scale dependence. The dependence on different sets of parton densities is rather weak and also leads to a variation of the production cross sections by about 15%. The signature of Higgs boson production in the VH channel are governed by the corresponding decays of the Higgs boson and vector boson.

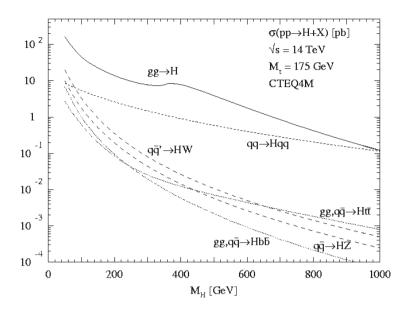

gg, qq → tt̄H Also the process gg, qq → tt̄H (Figure 3.3-(d)) is relevant only for small Higgs

masses. The analytical expression for the parton cross section, even at lowest order, is quite

involved, so that just the final result for the LHC cross section are shown in Figure 3.4.

#### 3.1.3 Higgs Boson Decay and Search at ATLAS

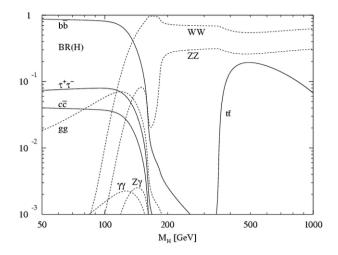

For each Higgs mass, the Standard Model precisely predicts the decay channels of the Higgs and their brunching ratio, which allows a precise assessment of the Higgs boson properties. The decay width of the Higgs boson as a function of Higgs mass is shown in Figure 3.5. Here, Higgs decay process for each Higgs mass  $M_H$  are detailed.

Figure 3.3: Higgs Production

• Low-Mass Higgs Boson ( $M_H < 120 GeV/c^2$ ):

Below the WW or ZZ threshold ( $M_H < 2 M_Z$ ), the dominant decay into the heaviest accessible pair of quarks

$$H \to b\bar{b}$$

(3-1-14)

is swamped by the QCD background (the direct  $b\bar{b}$  crosssection is very high, see Figure 3.5). The decay channel

$$H \to \gamma \gamma$$

(3-1-15)

suffers an enormous background from  $qp \to \gamma\gamma$ ,  $gg \to \gamma\gamma$ ,  $gg \to q\gamma\gamma$ , and  $Z \to e^+e^-$  processes, where the jets or  $e^\pm$  fake a  $\gamma$ . These backgrounds can be reduced if the detector is equiped with excellent photon resolution and excellent  $\gamma/jet$  and  $\gamma/e^\pm$  separation. Hence an electromagnetic calorimetry with excellent performance is required.

#### • Search for VBF H $\rightarrow \gamma \gamma$ mode:

When the mass of Higgs is relatively small (115  $< m_{Higgs} < 140 GeV/c^2$ ), a vector boson fusion process with

$$H \to \tau^+ \tau^- \tag{3-1-16}$$

Figure 3.4: Production Crosssection of Higgs [14]

plays a important role for this discovery. In this channel,  $\gamma\gamma \to \text{leptonic decay} + \text{hadronic decay}$  (lepton-hadron mode) is as important as leptonic decay + leptonic decay (lepton-lepton mode) because a branching ratio of hadronic tau decay is larger than that of leptonic tau decay by a factor of about 2. It leads this channel to the first discovery of Higgs.

Since W and Z bosons are heavy, the outgoing quarks have larger transverse momenta than the QCD background process. They will be observed in a forward region with high- $p_T$ . Tagging these forward jets help us to suppress the background processes. Furthermore, there is no color exchange between two outgoing quarks, the Higgs boson will be observed in large rapidity gap, where activities of QCD jets are small.

$H \to \tau\tau$  provides high-p<sub>T</sub> lepton from a leptonic tau decay and it can be used as a trigger of  $E_T$  information.

Dominant background process is Drell-Yan with two high- $p_T$  jets and the invariant mass distribution makes a peak at  $Z_0$  mass.

• Intermediate Mass Higgs Boson ( $120GeV/c^2 < M_H < 800GeV/c^2$ ): In this mass region the decay

Figure 3.5: Decay width of the Higgs boson as a function of the Higgs mass [14]

$$H \to ZZ^{(*)} \to l^+ l^- l^+ l^-$$

(3-1-17)

provides a very clean signature of the Higgs boson. For the range  $M_H < 2M_Z$  one of the two Z boson is virtual (off-shell). For a Higgs mass of 150 GeV/ $c^2$  one expects about 550 such events per year in a summing which luminosity. The four leptons have a high transverse momentum ( $5GeV/c < p_T < 50GeV/c$ ). The background is mainly coming from prompt muons, decay muons, hadronic punch-through, neutrons and muon induced electromagnetic secondaries. To achieve a good acceptance for such kind of events, the geometrical and kinematic acceptance for leptons has to be maximized. The significance of the signal will depend on the four lepton mass resolution. Hense a good lepton energy and momentum resolution at the level of 1% is necessary. For large Higgs boson masses the Higgs width increases rapidly and the signal will be rate limited, hence the accelerator luminosity becomes more important than the detector performance.

• Heavy Mass Higgs Boson ( $M_H > 800 GeV/c^2$ ): For a heavy Higgs boson the channel

$$H \to ZZ^{(*)} \to l^+ l^- \nu \tilde{\nu} \tag{3-1-18}$$

becomes six times more frequent than  $H \to ZZ^{(*)} \to l^+l^-l^+l^-$  and can be detected with the measurements of two high-p<sub>T</sub> leptons and a high missing  $E_T$  due to the escaping neutrinos.

Also the channels

$$H \rightarrow WW, ZZ \rightarrow l^{\pm} + \nu + 2jets, 2l^{\pm} + 2jets$$

(3-1-19)

provide promising signatures for a heavy Higgs boson.

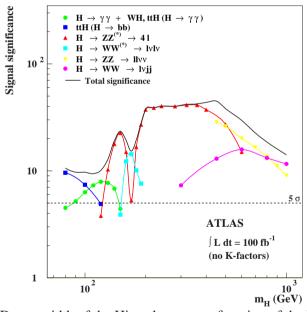

If these expectations are combined with a simulation of the detector response of the ATLAS experiment, it becomes possible to estimate how well the experiment will be able to find the Higgs boson. Figure 3.6 shows the sensitivity for the discovery of the Standard Model Higgs boson for several Higgs decay channels for the ATLAS experiment. The result shown here assumes an integrated luminosity decay channels for the ATLAS experiment. The result shown here assume an integrated luminosity of  $100 \ fb^{-1}$ . The figure shows that if the Higgs boson exists, the ATLAS experiment will be able to observe it with a  $5\sigma$  statistical significance over the full mass range from  $100 \ GeV/c^2$  up to  $1 \ TeV/c^2$ .

Figure 3.6: Decay width of the Higgs boson as a function of the Higgs mass

# **Chapter 4**

# The ATLAS

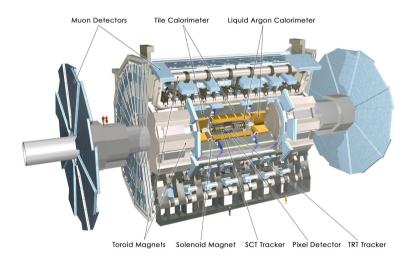

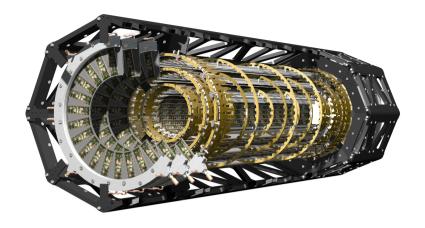

The ATLAS [9] is multi purpose detector installed in a LHC collision point. The ATLAS is characterized by its magnet configuration; a superconducting solenoid is installed around the Inner Detector and large superconducting air-core toroids consisting of independent coil is arranged with an eight fold symmetry outside the calorimeters. ATLAS is 22m in height and 44m in length and its weight is about 7,000 tons. Figure 4.1 shows a 3D view of the whole ATLAS detector.

Figure 4.1: ATLAS Detector

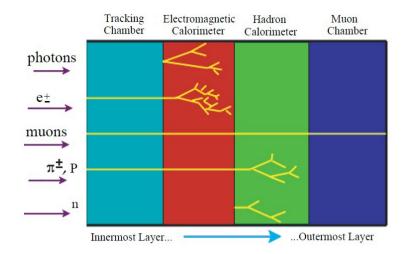

For physics studies at the LHC, we need to know what kinds of particles are produced, by using combinations of various detectors. Behavior of particles in each detector is instructed in Figure 4.2. The produced particles can be distinguished by their differences of interaction with matters. For example, charged particles can be detected by a tracking detector and, by generating a magnetic

field and detecting their trajectories there, their momenta can be measured. Particles with electric charge and photons can be detected by an electromagnetic calorimeter and electrons and photons can be identified there. Strongly interacting particles such as mesons and nucleons can be detected by a hadron calorimeter. Since muons deposit little energy in the calorimeters and have a long life time, they reach outside of the calorimeters and are detected by the muon spectrometer. Details of each detector are explained later.

For not only particle identification but also event selection, combined information from the detectors is utilized. For example, b quarks and c quarks can be detected by following way. While t quarks immediately decay after its production, b hadrons and c hadrons have comparatively long life time and fly for a moment. Then they decay enough far away from the primary vertex and made the secondary vertices. Therefore, b and c hadrons can be detected by finding the secondary vertices.

To exploit the full physics potential of the LHC, the ATLAS detector was designed to fulfill the following requirements;

- large acceptance and max  $\eta$  coverage for hermetic jet and missing  $E_T$  calorimetry.

- very good electoromagnetic calorimetry for electron and photon measurement.

- very good tracking efficiency for lepton momentum measurements, secondary vertex findings,

and enhancement of the accuracy of electron and photon identification. Here tracking in jets

have to be done;

- standalone muon momentum measurement at high luminosity.

- very low-p<sub>T</sub> trigger and reconstruction capability at low luminosity.

#### **4.1 Definition of Coordinates**

The coordinates in the ATLAS detector are defined as following. The beam line is defined as z-axis whose positive direction points in the direction of the LHC-b experiment. The plane transverse to the z-axis is defined as x-y plane. The positive x-axis is pointing from the interaction point to the center of the LHC ring and the positive y-axis is pointing to upwards.

While the Cartesian coordinate system is defined, basically cylindrical coordinates are used because of the detectors being cylindrically symmetric. In this case, the z-axis is the same as for the

Figure 4.2: Behavior of PArticles in each Detector

Cartesian coordinate system. The azimuthal angle  $\phi$  is defined as the angle from positive x-axis in x-y plane with the  $-\pi$  to  $+\pi$  range. The polar angle  $\theta$  is also defined as the angle from the positive z-axis, and the psudorapidity as  $\eta = -ln(tan\frac{\theta}{2})$ . For hadron collider,  $\eta$  is often used because the particle distribution in pseudorapidity  $\frac{\delta N}{\delta \eta}$  is basically flat.

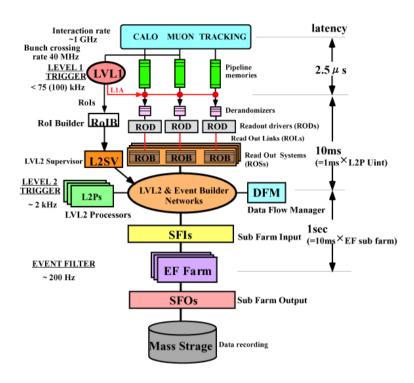

#### 4.2 DAQ System

The ATLAS trigger and data acquisition (DAQ) system is based on three levels of online event selection. Each trigger level refines the decisions made at the previous level and, where necessary, applies additional selection criteria. Starting from initial bunch crossing rate of 40.08 MHz (interaction rate of about 10<sup>9</sup> Hz at a luminosity of 10<sup>34</sup>), the rate of selected events must be reduced to about 200 Hz for permanent storage. While this requires an overall rejection factor of 10<sup>7</sup> against so called minimum bias events, very good efficiencies must be retained for the rare new physics processes, such as Higgs boson decays.

#### 4.2.1 Overview of the Trigger System

Figure 4.3 shows a simplified functional view of the Trigger and DAQ system. In the following, a brief description is given for some of the key aspects in the event selection process.

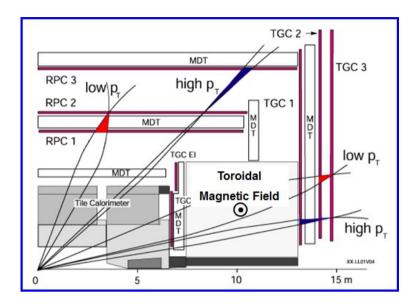

The first step of trigger system is named level-1(LVL1) trigger [21] which makes an initial se-

Figure 4.3: Block Diagram of the Trigger and DAQ for ATLAS

lection based on reduced granularity information from a subset of detectors. It consists of the muon trigger and the calorimeter trigger. In the muon trigger, high transverse momentum ( $p_T$ ) muons are indentified using only the trigger chambers, RPCs (Resistive Plate Chambers) in the barrel and TGCs (Thin Gap Chambers) [23] in the endcap regions. Detailed description of the LVL1 muon trigger is in the next chapter of these trigger chambers and Muon Spectrometer. The calorimeter selections are based on reduced granularity information from all the calorimeters (EM and hadronic; barrel, endcap, and forward). Objects searched for by the calorimeter trigger are high- $p_T$  electrons, photons, jets, and  $\tau$  leptons decaying into hadrons, as well as large missing and total transverse energies. In the case of the electron/photon and hadron/ $\tau$  triggers, energy isolation cuts can be applied. Trigger information is provided for a number of sets of  $p_T$  thresholds. The missing and total scaler transverse energies used in the LVL1 trigger are calculated by summing over the trigger towers. In addition, a trigger on the scaler sum of jet transverse energies is also available.

The LVL1 trigger decision is based on combinations of objects required in coinsidence or veto. Most of the physics requirements of ATLAS can be met by using, at the LVL1 trigger level, fairly simple selection criteria of a rather inclusive nature. However, the trigger implementation is flexible and it can be programmed to select events using more complicated signatures. The maximum rate

at which the ATLAS Front End system accepts the LVL1 trigger is limited to 75kHz in total. The rates are expected to be less than this limit but, in case, rates could be significantly reduced without major consequences for the physics programs, for example by increasing the thresholds on some of the inclusive (single object) triggers when operating at the highest luminosities and by relying more heavily on multi object triggers.

An essential requirement on the LVL1 trigger is that it should uniquely identify the bunch crossing of interest. Given the short bunch crossing interval(25ns), this is a non trivial consideration. It is important to keep the LVL1 latency (time taken to form and distribute the LVL1 trigger decision) to a minimum. During this time, information for all detector channels has to be conserved in "pipeline" memories. These memories are generally contained in custom integrated circuits, placed on or nearby the detectors. The LVL1 latency is required to be less than  $2.5 \mu s$ .

All the detector data for the bunch crossing selected by the LVL1 trigger are held in the readout buffers, either until the event is rejected by the LVL2 trigger [22], in which case the data are discarded, or, in case the event is accepted by LVL2, until the data have been successfully transferred by the DAQ system to storage associated with the Event Filter [22], which makes the third level of event selection.

The LVL2 trigger makes use of Region of Interest(ROI) information provided by the LVL1 trigger. This includes information on the position  $\eta$ ,  $\phi$ , and  $p_T$  of candidate objects, and energy sums. The ROI data are sent from LVL1 to LVL2 for all events selected by the LVL1 trigger. Using the ROI information, the LVL2 trigger selectively access data from the readout buffers, moving only the data required to make the LVL2 decision. It is expected that LVL2 will reduce the rate less than 3.5kHz and latency of the LVL2 trigger is variable from event to event and is expected to be 40ms on average.

After LVL2, the last stage of the online selection is performed by the Event Filter. It employs offline algorithms and methods, adapted to the online environment, and use the most up to data calibration alignment information and the magnetic field map. The Event Filter will make the final selection of physics events written to mass storage for subsequent full offline analysis. The output rate from LVL2 should then be reduced by an order of magnitude, giving less than 200Hz, corresponding to an output data rate less than 300MB/s if the full event data are to be recorded.

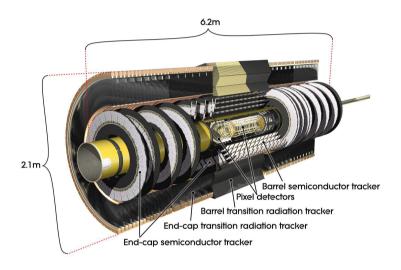

#### 4.3 Inner Detector

ATLAS Inner Detector is contained within a cylinder of length of 7m and a radius of 1.15m, in a solenoidal magnetic field of 2T. Momentum and vertex measurements are achieved with a combination of discrete high-resolution semiconductor pixel and strip detectors in the inner part of the tracking volume. Electron identification is performed by continuous straw tube tracking detectors with transition radiation capability in the outer part. Overall inner detector lay out is shown in Figure 4.4 and details for each detectors are mentioned below.

Figure 4.4: 3D overall inner detector layout

#### 4.3.1 Silicon pixel vertex detector (PIXEL)

ATLAS Pixel detector provides a very high granularity and high precision set of measurements as close to the interaction point as possible. A Pixel sensor is a  $16.4 \times 60.8$  mm wafer of silicon with 46,080 pixels,  $50 \times 400\mu$ m each. Each sensor is readout by 16 chips, each serving an array of 18 by 160 pixels. The 80 million pixels cover an area of 1.7 m<sup>2</sup>. The system consists of three barrels at average radii of about 5, 9 and 12 cm (1456 modules) respectivly, and three discs on each side between radii of 9 and 15 cm (288 modules), as shown in Figure 4.5. The modules are overlapped on the support structure to give hermetic coverage. The thickness of each layer is expected to be about 2.5% of a radiation length at normal incidence. Typically three pixel layers are crossed by each track.

Figure 4.5: Pixel Detectors

#### 4.3.2 Semi Conductor Tracker (SCT)

The SCT system is designed to provide four precision measurements per track in the intermediate radial range, contributing to the measurement of momentum, impact parameter and vertex position, as well as providing good pattern recognition by the use of high granularity. The system is an order of magnitude larger in surface area than previous generations of silicon microstrip detectors, and in addition, must face radiation levels which will alter the fundamental characteristics of the silicon wares themselves.

Figure 4.6 shows 3D view of the SCT system, which covers  $|\eta|$  <2.5. The barrel SCT uses four layers of silicon microstrip detectors to provide precision points in the r- $\phi$  and z coordinates. Each silicon detector is  $6.36 \times 6.40 cm^2$  with 768 readout strips each with 80  $\mu$ m pitch. Each modul consists of four detectors. On each side of the module, two detectors are wire bounded togetger to form 12.8 cm long strips. Two such detector pairs are then glued together back to back at a 40mrad angle, separated by a heat transport plate, and the electronics is mounted above the detectors on a so-called hybrid. The readout chain consists of a front end amplifier and discriminator, followed by a binary pipeline which stores the hits above threshold until the arrival of the first level trigger decision. The forward modules are very similar in construction but use tapered strips, with one set aligned radially. Forward modules are made with either about 12 or 7 cm lengths. The detector contains 61 cm<sup>2</sup> of silicon detectors with 6.2 million readout channels. The spatial resolution is  $16 \,\mu$ m in r- $\phi$  and  $580 \,\mu$ m in z. Tracks can be distinguished if separated by more than about 200  $\mu$ m.

Figure 4.6: SCT

#### **4.3.3** Transition Radiation Tracker (TRT)

TRT is based on the use of straw detectors, or tubes, which can operate at the expected high rates due to their small diameter and the isolation of the sensitive wires within individual gas volumes. Electron identification capability is added by employing Xenon gas to detect transition radiation photons created in a radiator between the straws. The nonflammable gas mixture is  $Xe:CO_2:O_2 = 70:27:3$  with a total volume. The barrel section is built of individual modules covering the radial range from 56 cm to 107 cm. Each endcap consists of 18 wheels. Each channel provides a drift time measurement that gives a spatial resolution of 170  $\mu$ m per straw.

#### 4.4 Calorimeters

In contrast to the inner detectors, such as magnetic spectrometers, intrinsic resolution of calorimeters[19] improves with energy, which makes themselves very suitable detectors at high-energy machines.

The task of the calorimeters at hadron colliders are the followings;

- Accurate measurement of the energy and position of electrons and photons.

- Measurement of the energy and direction of jets and measurement of the missing transverse energy  $(E_T)$  of the event.

- Particle identification, for instance separation of electrons and photons from hadrons and jets,

and tau hadronic decay from jets.

• Event selection at the trigger level.

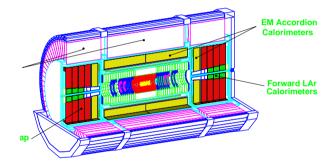

The overall detector layout is shown in Figure 4.7. Highly granular Liquid Argon (LAr) electromagnetic sampling calorimeter [18], with an emphasis on energy and position resolution, covers the pseudorapidity range  $|\eta|$  <3.2. At large rapidities, higher radiation resistance is needed and the intrinsically hard LAr technology is used. In the endcap, the LAr technology is also used for the hadronic calorimeters. There are special LAr forward calorimeters which extend the pseudorapidity coverage to  $|\eta|$  = 4.9. The LAr calorimetery is contained in a cylinder with an outer radius of 2.25m and extends longitudinally to  $\pm 6.75m$  along the beam axis. The bulk of the hadronic calorimetry is provided by scintillator tile calorimeters, which is separated into a large barrel and two smaller extended barrel cylinders are 4.25m and its half length is 6.10 m. The overall calorimeter system provides good jet and missing  $E_T$  performance of the detector.

Figure 4.7: overall Calorimeter Layout

#### 4.5 Muon Spectrometer

Muons interact weakly and electromagnetically like electrons, but they can reach outside of the calorimeters because muon mass is almost about 200 times heavier than electron mass. Therefore, the muon spectrometer is placed at the outermost of the detectors.

High momentum final state muons are one of the most promising and robust signatures of physics at the LHC. To exploit this potential, the ATLAS is equipped with a high resolution muon spectrometer [16] with stadalone trigger and momentum measurement capability over a wide range of transverse momentum( $p_T$ ), pseudorapdity( $\eta$ ), and azimuthal angle( $\phi$ ). Muon measurement at ATLAS is based on the magnetic deflection measurement of muon tracks in a system of the large superconducting air

core toroids instrumented with tracking chambers. Four type of muon spectrometers are installed in ATLAS detector, two of them, Resistive Plate Chamber and Thin Gap Chambers are trigger chambers and the other, Monitored Drift Tube and Cathode Strip Chamber are for precision measurement. In the range  $|\eta|_1$ 1.0, bending fields are provided by a large barrel magnet consisting of eight coils surrounding the hadron calorimeter. For 1.4 <  $|\eta|$  < 2.7, muon tracks are bent in two smaller endcap magnets inserted into both end of the barrel toroid. In the interval 1.0 <  $|\eta|$  < 1.4 magnetic deflection is provided by a combination of barrel and endcap fields. This magnet configuration provides a field that is mostly orthogonal to the muon trajectories, while minimizing the degradation of resolution due to multiple scattering.

The detailed description about each muon spectrometer is mentioned in chapter 5 of "Muon Spectrometer".

# Chapter 5

# **Muon Spectrometer**

ATLAS is a multi purpose detector for LHC and consists of several detector parts. Muon detectors [16] are a part of ATLAS and play following two roles; momentum measurements with precise chambers and event trigger for muons with trigger chambers.

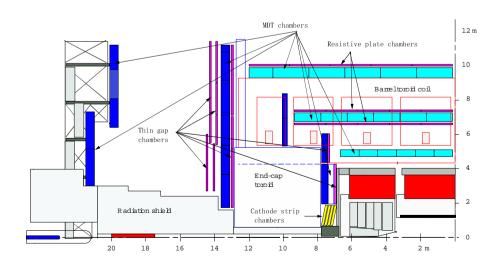

A quarter view of the Muon system in R-Z plane is shown in Figure 5.1.

In both the barrel and endcap region, there are 3 stations of muon chambers.

There are 3 air-core toroidal magnets; a barrel magnet with 26 m long and 19.5m in radius, and two endcap magnets with 5.6 m long and 3 m in radius. The pictures of these magnet are shown in Figure 5.2 and 5.3. Trajectories of a muon from the interaction points are bent in these toroidal magnetic fields. Momentum of the muon can be obtained by measurement of the curvature of the track.

Figure 5.1: R-Z View of the ATLAS Muon System

Figure 5.2: Barrel Toroid Magnet

Figure 5.3: Endcap Toroid Magnet

#### 5.0.1 Measurement Method of Muon

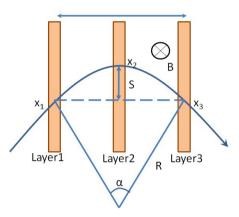

A popular method about measurement of muon track is to focus to transverse momentum measurement.

The momenta of charged particles can be calculated by detecting their trajectories in the magnetic field. If a track is detected at three equally spaced points, the sagitta *s* of an indication of bentness is defined as shown in Figure 5.4 and can be calculated as

$$s = R(1 - \cos\frac{\alpha}{2}) \sim \frac{R\alpha^2}{8} \tag{5-0-1}$$

Then the momentum P of a charged particle in magnetic field B is calcurated as

$$P = 0.3BR \tag{5-0-2}$$

whre R is the measured radius of the orbit, then concerning  $\alpha$  to be

$$\alpha = 0.3 \frac{BL}{P} \tag{5-0-3}$$

the sagitta is represented as

$$s = 0.3 \frac{BL^2}{8P}. (5-0-4)$$

Thus, the momentum can be obtained from measurement of sagitta.

Measurement of sagitta is a basical algorithm for measurement of  $p_T$ , to find and select high  $p_T$  muon track.

LVL1 Muon System measures sagitta of muon candidates using several layers of detectors. In nominal case, high  $p_T$  muon may have small sagitta. But ATLAS magnetic field is not uniform and even in some region that as almost no integrated magnetic field. It affects bentness of muon tracks dependents on their location of tracks.

Figure 5.4: Measurement of Sagitta

#### 5.1 Precision Chamber

Two types of precision chambers are installed in ATLAS muon spectrometers. They are Monitord Drift Tube (MDT) and Cathode Strip Chamber (CSC).

MDTs are installed in barrel region and endcap region, and cover  $|\eta| < 2.0$ , CSCs are installed in forward region and cover  $2.0 < |\eta| < 2.7$ .

Precision chambers measure the track coordinates in bending direction with high precision.

#### **5.1.1** Monitored Drift Tube

The Monitored Drift Tube (MDT) measures position of charged tracks precisely in the bending direction of the toroidal magnet. The basic element of MDT is an aluminium drift tube. Its diameter

| Parameter                   | Value                   |

|-----------------------------|-------------------------|

| Tube Material               | Al                      |

| Outer Tube Diameter         | 29.970mm                |

| Tube Wall Thickness         | 0.4mm                   |

| Wire Material               | gold-plated W/Re (97/3) |

| Wire Diameter               | $50  \mu \mathrm{m}$    |

| Gas Mixture                 | $Ar:CO_2 = 97:3$        |

| Gas Pressure                | 3.0 bar                 |

| Gas Gain                    | $2 \times 10^4$         |

| Applied Voltage             | 3080V                   |

| Maximum Drift Time          | about 700ns             |

| Average Resolution per Tube | $80\mu\mathrm{m}$       |

Table 5.1: MDT Parameters

is 29.970mm, with the wall thickness of 0.4mm. A Tungsten-Rhenium wire of diameter 50  $\mu$ m is strung at the center of tube. The wire is fixed on the cylindrical end plug which keeps the spacial position of wire with respect to the tube with good accuracy. The tube is filled with Ar(97):CO2(3) gas at 3 bar. Applied High Voltage for the wire with average gain of 2 ×10<sup>4</sup>.

The maximum drift time is about 700ns and average of spacial resolution per tube is about 80  $\mu$ m. The main parameters of the MDT are summarized in Table 5.1.

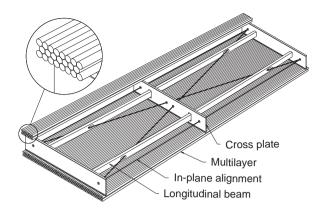

MDT tubes are packed together and form a chamber. MDT is installed in three stations; inner, middle and outer. Middle and outer MDT stations consist of three layers and inner MDT station consists of four layers.

The position and deformation affect momentum quality of MDT. They should be known to a precision of 30  $\mu$ m. An optiacal monitoring sensor to align the MDT form a laser-based alignment system which consists of three active elements of LED, lens and CCD camera. The resolution of measurement is about 1  $\mu$ m.

Figure 5.5: A Schematic View of MDT for Barrel

### 5.1.2 Cathode Strip Chamber

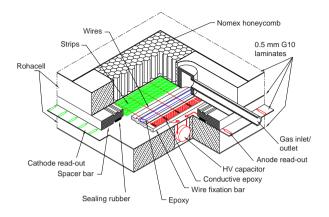

CSC is Multi Wire Proportional Chambers(MWPC) with a cathode strip readout. Position resolution of charged tracks is  $60\mu m$ .

The MDT can not be operated in the forward region where high counting rate ( >200KHz/cm2) is expected, because the drift time of MDT is rather long

CSCs are installed in high counting rate area, and covers upto  $|\eta| < 2.7$ . The capacity of counting rate for CSC is  $1 \text{kHz/cm}^2$  was expected. The schematics of CSC is shown in Figure 5.6. Anode wire diameter is  $30 \mu \text{m}$ . Applied high voltage is 1900V. The gain achieves  $6 \times 10^6$  Electron drift time should be less than 40ns resulting a time resolution of 7ns. Applied gas is composed of  $\text{Ar/CO}_2 = 8:2$ . It has low neutron sensitivity (less than  $10^{-4}$ ).

Two types of CSCs are installed; small chamber and large chamber. Readout strip pitch is 5.31mm for large chamber, and 5.56mm for small chamber. Track coordinate resolution of CSC is achieved 60  $\mu$ m, and the resolution of  $\phi$  direction is about 5mm.

Figure 5.6: Cathode Strip Chamber

### **5.2** Trigger Chamber

ATLAS DAQ has trigger system to reduce background and choose the interesting phenomena among huge background events. LVL1 Muon Trigger is a part of first stage of ATLAS trigger system. The LVL1 trigger, which optimized to find high  $p_T$  muons is implemented in ATLAS trigger system.

The main role of the Trigger Chambers is find and select the most interesting high  $p_T$  muon in each bunch crossing and provide L1A (Level1 Accept) in each detector system.

Two types of trigger chambers are installed in ATLAS muon system. They are Resistive Plate Chamber (RPC) and Thin Gap Chamber (TGC). Six layers of RPCs are installed in barrel region which covers  $|\eta| < 1.05$ . Seven layers of TGCs are installed in Endcap regions which cover  $1.05 < |\eta| < 2.4$  on both sides. Both chambers generate fast signal, whose response time achieves in order of nano seconds. Position resolution is required to be about 1cm; it is enough to do coarse  $p_T$  measurement and track identification. Second coordinate measurement about 5cm is required because MDT has few sensitivity for  $\phi$  direction, for higher level trigger and offline analysis.

### 5.2.1 Resistive Plate Chamber

The Resistive Plate Chamber is a gaseous detector. It does not have any wires. Two parallel plates are faced with a gap of 2mm. The plates are made of 2mm thick of Bakelight with resistive surface. (volume resistivity is 1 to  $5 \times 10^{10} \Omega$ )

9.8 kV of applied voltage allows avalanches along charged tracks with a streamer probability of less than 1%. Readout metal plate is put on the outer faces of resistive plates. The filled gas

is  $C_2H_2O_4(94\%)/Iso - C_4H_{10}(5.0\%)/SF_6(0.3\%)$ . The position resolution in  $\eta$  coordinate and  $\phi$  coordinate is about 10mm and time resolution achieved less than 10ns. The local rate capability is about 1kHz/cm<sup>2</sup>.

Figure 5.7: Resistive Plate Chamber

### 5.2.2 Thin Gap Chamber

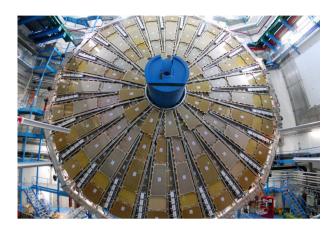

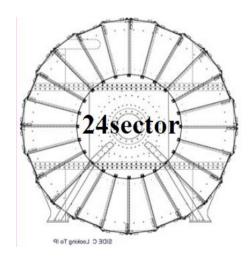

Thin Gap Chamber(TGC) is a trigger chamber and installed in both endcap region, and TGCs are installed like a wheel structure(Figure 5.8). The small  $\eta$  region is named Endcap and covers  $1.05 < |\eta| < 1.9$  for each side, and the large  $|\eta|$  region named Forward and covers  $1.9 < |\eta| < 2.4$ .

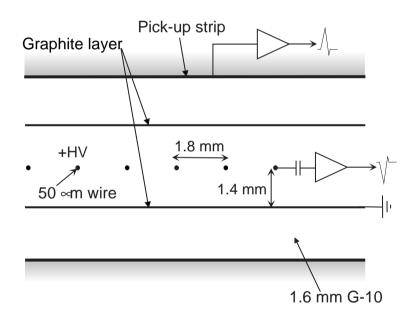

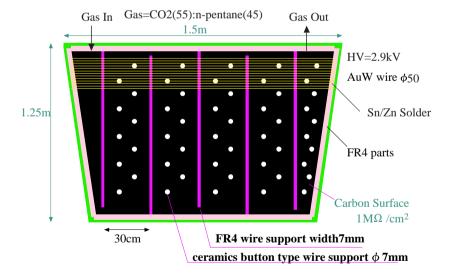

TGC has two types channel readout of anode wire and cathode strip. The diameter of anode wire of tangsten with Au coating is  $50 \,\mu\text{m}$ . The distance between wire anode and strip cathode are shorter than the distance between wires as shown in Figure 5.9. The cathode consists of carbon coated glassepoxy which surface resistance is  $1\text{M}\Omega/\Box$ . This thin gaps make shorter drift time and high time resolution. Two graphite cathode plane on FR4 board are placed 1.4 mm from the wire plane. The pick up strip of copper on the outer surface of FR4 are formed in orthogonal direction to the wire, this structure makes two dimensional position information. To keep the gap between anode and cathode, wire supports are placed as shown in the Figure 5.11.

The optimized HV is applied for each chamber. The volumes are determined taking into account number of noisy channel, and hit efficiency. Applied voltage is 2800V is default, but higher voltage upto 2950 V is applied for low gain chambers.

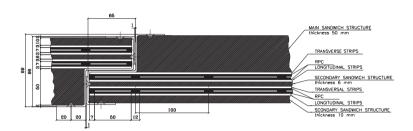

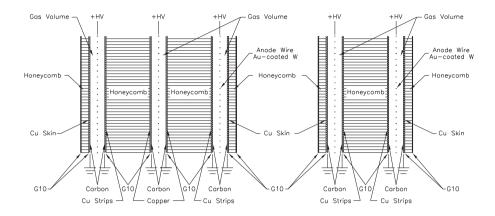

Two types of TGC are fabricated; doublet type and triplet type. Doublet TGC consists of 2 layers wire and 2 layers strip. Wire and strip pair sandwiches honeycombs. This honeycomb structure reinforces the strength of TGC with light weight. Triplet TGC consists of 3 layers wire and 2 layers of strip. There are three pairs of cathodes but only outer layers are picked up. Cross section of TGCs

# are shown in Figure 5.10

Chambers are filled with gas of  $CO_2$ :n-pentane [17] = 55:45. This type of cell geometry allows operation in limited-proportional mode.

Figure 5.8: Installed TGC Big Wheel

Figure 5.9: Structure of TGC

Figure 5.10: Cross section of triplet (left) and doublet (right) TGCs

Figure 5.11: Structure of TGC Wire Support

### 5.3 Toroidal Magnet

Each toroidal magnet consists of eight flat coils as octant symmetrically around the beam axis, Endcap coils are interleaved between barrel coils.

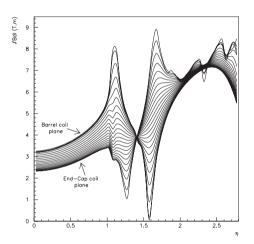

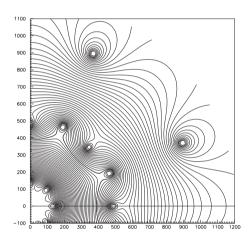

Integrated intensity of magnetic field in barrel region is 2 to 6 Tm, and the one in endcap region is 4 to 8 Tm as shown in Figure 5.12.

Figure 5.13 shows line of magnetic field at Z=10m. In the interference region of barrel and endcap magnets (r=400 $\sim$ 500cm), magnetic field is not uniform and not along  $\phi$  direction.

Figure 5.12: Magnetic Field Distribution in  $\eta$ . Figure 5.13: X-Y View of Magnetic Field at Z = Horizontal axis means  $\eta$ , and vertical axis means 10m (Horizontal axis means X coordinate, and verthe integrated intensity of magnetic field(Tm).

## 5.4 LVL1 Muon Trigger

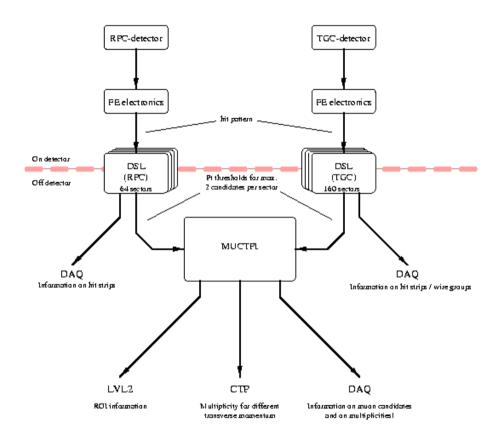

Muon system has a triggering step of LVL1 in the scheme of ATLAS DAQ. A schematic of the ATLAS LVL1 Muon Trigger is shown in Figure 5.14. LVL1 Muon Trigger is provided from barrel and endcap chambers. Muon candidates are selected in endcap and barrel region in parallel. MuCTPI combines these information and send it to the CTP.

Figure 5.14: A Schematic of the ATLAS LVL1 Muon Trigger

### 5.4.1 Requirements of LVL1 Muon Trigger

The LVL1 Muon Trigger aims to find high  $p_T$  muons and reduce the trigger rate upto 15kHz at maximum.

Algorithm of LVL1 Muon Trigger is processed without deadtime, and it must be produced in each beam collision. The information of LVL1 Muon Trigger consists of position information of ROI, discriminated  $p_T$  in six level, and Bunch Crossing Identification (BCID).

### **5.4.2** Muon to Central Trigger Processor Interface (MuCTPI)

MuCTPI has a role to pass LVL1 Muon Trigger Candidates to CTP from RPC and TGC. Each LVL1 Muon Trigger provides the information of trigger candidate consisting of position information and six level of pT threshold information. MuCTPI receives these infomatin, and treat the chamber overlap and boundary.

Trigger information will be sent to CTP.

# Chapter 6

# **Endcap Muon Trigger**

TGC is used to provide the LVL1 Encdap Muon Trigger

LVL1 Endcap Muon Trigger is processed using dedicated electronics online. Processes in these electronics are in the pipeline provide the trigger of consecutive beam collisions.

Coincidence of TGC hits between three stations on each side gives good trigger efficiencies with enough  $p_T$  resolution and background rejections. In this chapter, how to achieve the ATLAS required performance will be presented from the viewpoints of algorithm, electronics, and implementation.

# 6.1 Overview of LVL1 Endcap Muon Trigger

LVL1 Endcap Muon Trigger system covers  $1.05 < |\eta| < 2.4$  in both sides of ATLAS.

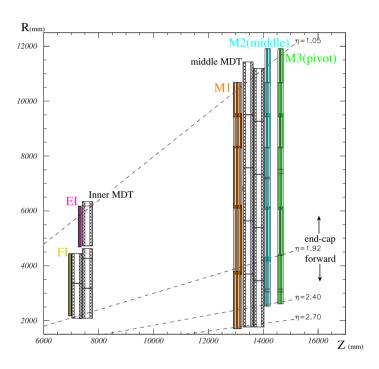

TGC chambers are installed in 4 stations; Inner, M1, M2, M3. M1, M2 and M3 stations are parts of the Big Wheel located at z of about 14m. In the M1 station, TGCs with three gas gaps (called Triplet type) are installed. TGCs with two gas gap (called Doublet type) are installed in other stations. Figure 6.1 shows a cross-section of TGC stations.

At first, hits on the pivot plane (TGC at M3) are used to draw the infinite momentum path for a muon candidate. A window for the coincidence is defined for each trigger plain (TGCs in M2 and M3) in R and  $\phi$  directions around the infinite momentum track. Coincidenced signals of R- $\phi$  will make a trigger candidate if a hit is found in the window corresponding to the hit position in the pivot plane. The deviation from infinite momentum and observed hits found in trigger planes is related to the momentum. Overview of LVL1 Endcap Muon Trigger algorithm is shown in Figure 6.2.

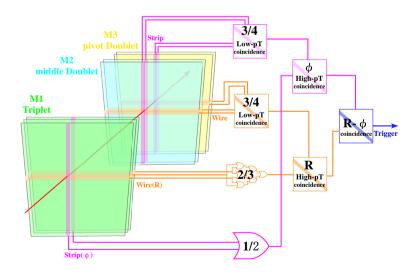

The LVL1 Endcap Muon Trigger system consists of 3 parts of coincidence; 2 station coincidences, 3 station coincidences and  $R-\phi$  coincidences, as shown in Figure 6.3. In 2 station coincidences and

3 station coincidences, R and  $\phi$  information are processed in parallel. In 2 station coincidences, at least 3 hits are required among 4 layers at M2 and M3 (pivot) station. The 2 station coincidence is called Low-pT coincidence because it can cover lower p<sub>T</sub> tracks. In 3 station coincidences, hits in M1 station are required in addition to 2 station coincidences. The 3-station coincidences is called High-pT coincidence. Track sagitta of  $\delta R$  and  $\delta \phi$  are calculated in both 2 station coincidences and 3 station coincidences.

Final decision of LVL1 Endcap Muon Trigger is done by R- $\phi$  coincidences. It selects muon candidates and determines their Region of Interest (ROI), p<sub>T</sub> level, and Bunch Counter ID(BCID). These information will be sent to Central Trigger Processor through Muon Central Trigger Processor.

Figure 6.1: A cross-section of the TGC Stations. (Horizontal axis means z position(mm), and vertical axis means position of radius R(mm).)

### 6.1.1 Big Wheel

Three stations of TGCs, M1, M2 and M3, are called as Big Wheel. TGCs in the Big Wheel in each side cover  $1.05 < \eta < 2.4$  and can be divided into two regions, Endcap and Forward;  $1.05 < \eta < 1.9$  is Endcap region, and  $1.9 < \eta < 2.4$  is Forward region.

Figure 6.2: A cross-section of the of LVL1 Endcap Muon Trigger Scheme (Horizontal axis means z position(m), and vertical axis means radius.)

Figure 6.3: Coincidences between stations in LVL1 Endcap Muon Trigger

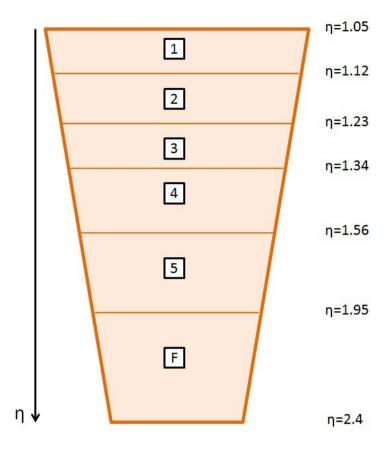

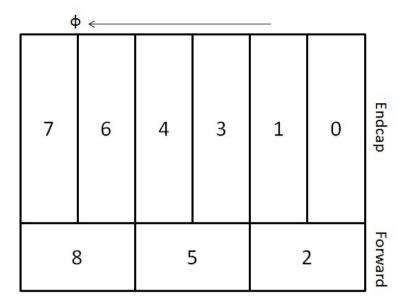

Pivot plane (M3 station) in Endcap region consists of 5 TGC chambers numbered from small  $\eta(1)$  to large  $\eta(5)$ , and Forward region contains one TGC chamber, (as shown in Figure 6.4)

Figure 6.4: TGC numbering on pivot plane

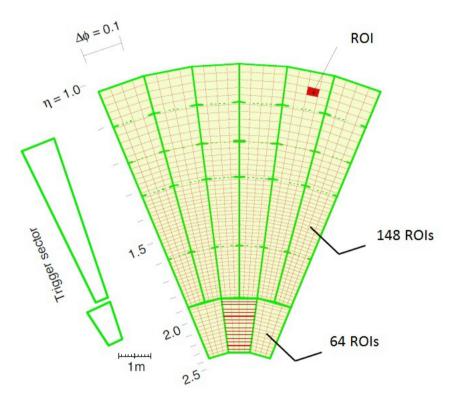

Trigger Sector is defined for the operation and implementation of LVL1 Endcap Muon Trigger. Each trigger sector can provide upto 2 muon candidates in each bunch crossing. ROI is an unit for position of trigger information. Each muon candidates is sent to CTP with its ROI and  $p_T$  level. The Forward region contains 24 trigger sectors divided in  $\phi$  direction. A trigger sector contains 64 ROIs, 16 divided in the R direction and 4 divided in the  $\phi$  direction.

A Forward Trigger Sector is 24 divided for  $\phi$  direction. ROI is defined as a region of 8 divided for the R direction and 4 divided for the  $\phi$  direction.

### 6.1.2 Small Wheel

Small wheel is installed at about z = 7m and consists of Endcap Inner (EI) and Forward Inner (FI). EI and FI are Doublet TGCs. Small wheel covers  $1.05 < |\eta| < 1.9$ . FI covers all  $\phi$  region, but EI has

Figure 6.5: Trigger Sector and ROIs in the sector. Each region surrounded by green line corresponds to a trigger sector, and a red colored cell is an example of ROI.

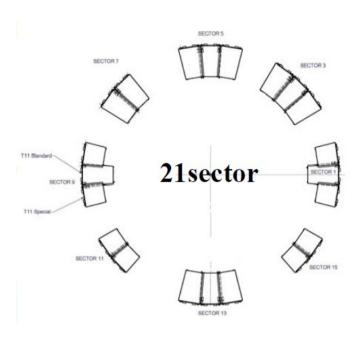

21 sectors and 8 holes toroidal magnet coils as shown in Figure 6.6 and 6.7.

Hit information on Small Wheel are not used in the current scheme of LVL1 Endcap Muon Trigger, but they are used in higher level trigger(LVL2 and Event Filter).

Figure 6.6: Overview of Endcap Inner

Figure 6.7: Overview of Forward Inner

# 6.2 Implementation on the TGC Electronics System

Detailed description on the Endcap muon trigger system is presented in this section.

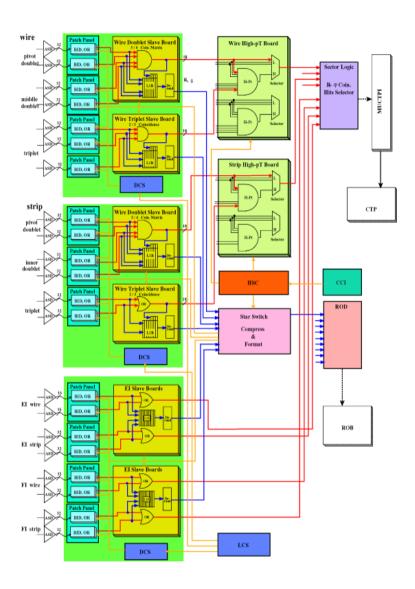

Figure 6.8 shows an overview of the TGC electronics scheme. Both wire and strip signals are transmitted to Amplifier Shaper Discriminator (ASD) [25][26] circuits. Four circuits are impelemented in an ASD chip, and four ASD chips are mounted on an ASD board. So, each ASD board can handle 16 channels. ASD boards are installed on the edge of a TGC and enclosed inside the TGC electronics shielding.

Signals from ASD board are sent to PS-Boards. Patch-Panel (PP) ASICs, Jtag Routing Controller(JRC), embedded Local Monitor Board (eLMB) and Slave Board (SLB) ASICs [27] are mounted on the PS-Board. PS Boards are placed on surface of the TGC wheels. Electronics for doublets are mounted on the outer surface of M3 and those for the triplets on the inner surface of M1.

Hit information in an event will not reach at same time without timing adjustment PP ASICs. Hit information in each bunch is sent to SLB ASICs, where 2 station coincidence and readout circuits are placed. Trigger information (position and sagitta) from the 2 station coincidence is encoded and passed to High-pT coincidence(HPT) Boards [28]. HPT boards are installed in HSC crates placed near the outer rim of the M1 wheel. Signals from doublet and triplet SLBs are combined to find tracks in R-z plane and  $R-\phi$  plane independently.

Trigger signals from both wire and strip HPT boards are sent the Sector Logic (SL) via optical link between the ATLAS detector and the counting room(USA15). The SL contains R- $\phi$  coincidence and track selector circuit to find muon candidates (upto 2 candidates in each trigger sector) with  $p_T$  and position information. Six level of  $p_T$  threshold will be determined in SL to select highest  $p_T$  candidate. Region of Interest (ROI) will be determined by wire and strip coincidence coordination for each candidate. These trigger candidates are sent to Muon Central Trigger Processor (MuCTPI). The SL has SLB ASICs also to read out information from HPT boards and trigger results. The detail of SL will be described in next chapter. Hereafter the electronics boards in each step and described in detail.

### 6.2.1 ASD

Each ASD board has 4 ASD chips and handles 16 channels of wire and strip signals from TGCs. ASD ASIC contains 4 channels of two-stage amplifiers with a base-line restorer and discriminators.

Figure 6.8: Overview of the TGC LVL1 Endcap Muon Trigger Electronics System

Figure 6.9: TGC electronics Placement

Output signals are sent to PS boards through twisted cables by using Low-voltage differential signaling (LVDS). The power, threshold voltage and test pulses for ASD boards are supplied from the PS boards.

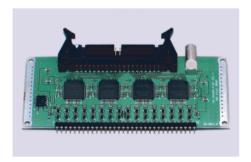

Figure 6.10: ASD Board

### 6.2.2 Patch Panel

The bunch crossing where a muon going through TGCs is produced should be identified by using timing information. In addition, signals need to be synchronized to take coincidences. However, signals from different positions arrive to PS boards in different timing because of differences on time of flight from the interaction point and cable propagation delay. The BCID for each hit signal is determined by the Patch Panel (PP) ASIC.

A block diagram of the PP ASIC is shown in Figure 6.11. At the first stage, LVDS receivers

followed by variable delays are implemented. One PP ASIC can handle 32 channels. The delay time can be varied in 32 steps and each step is 0.84 nsec. Hit signals can be masked out and/or asserted by using the MASK circuit. Then, signals are latched with the LHC clock to determine BCID. The output signals are synchronized with the clock. The signal will be sent after passing an OR logic to avoid the double count in the TGC overlap region.

Test pulses for ASD boards can be generated by the PP ASIC. The amplitude, width and timing of the test pulse can be varied. Parameters for delays, masks and test pulses are controlled by JTAG protocol.

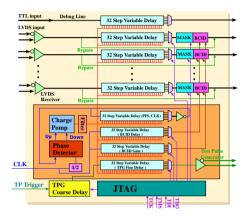

Figure 6.11: Block Diagram of PP ASIC

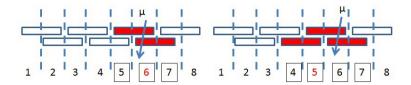

### 6.2.3 Slave Board (SLB) and 2 station coincidence

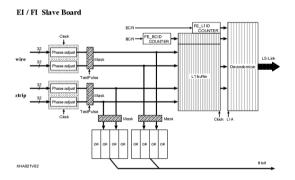

The SLB ASIC has two functional parts; trigger and readout.

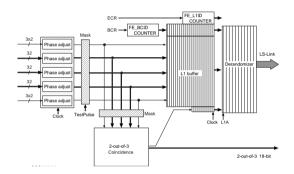

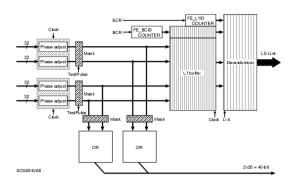

In one SLB ASICs, 5 kinds of circuits are implemented; wire doublets, strip doublets, wire triplet, strip triplet and inner stations (EI/FI). Different coincidence circuits and corresponding encoding circuits are implemented.

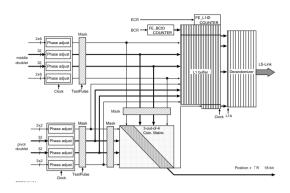

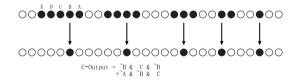

Figure 6.12 show block diagrams of SLB ASICs for wire doublets. Each SLB covers 4 adjacent trigger sub-sectors. Signals from both M2 (middle) and M3 (pivot) doublets are fed into the 3 out 4 coincidences. The candidate with least sagitta is searched in two adjacent sub-sectors. Each output with position and sagitta information is encoded in 9 bits. The trigger part consists of phase adjusters, masks and coincidences. Phase adjust circuit is used to synchronize input signal timings. Mask circuits performs de-clustering consecutive hits, masking in/out and generating test pulses. Figure 6.16 shows de-clustering rule. If consecutive hit channels are detected, the second lowest number of

hit channels is selected.

Figure 6.12: Block Diagram of 3 out of 4 SLB

Figure 6.13: Block Diagram of 2 out of 3 SLB

Figure 6.14: Block Diagram of 1 out of 2 SLB

Figure 6.15: Block Diagram of EIFI SLB

Figure 6.16: SLB Declustering Rule

The purpose of the readout part is to transfer inputs and outputs of the SLB for triggered events. The readout part consists of LVL1 buffer and derandomizer. The LVL1 buffer is a shift-register with 212 bits wide and 128 depth. 212 bits are further structed with 160 bits for input data, 40 bits for data of trigger line, and 12 bits of BCID. Data is kept until the L1A arrives. Data in 3 consecutive bunches (L1A timing, the previous BCID, and the next BCID) are transferred to the derandomizer, which sends data to the Star Switch together with 4bits of event counter via serial LVDS link.

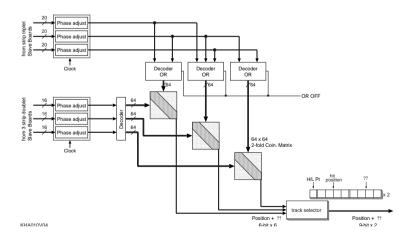

### 6.2.4 High-Pt board (HPT) and 3 station coincidence

The HPT processes 3 station coincidence. The HPT board receives 2 station coincidence and triplet coincidence information to find muon track with 3 station coincidence. Three station coincidences can make better resolution than 2 station coincidences for measuring of sagitta. HPT ASIC calculates from the  $\delta R$  and  $\delta \phi$  the curvature of muon track.

Wire and strip information are processed independently like 2station coincidence. Output information of HPT has three components; hit position on M3(pivot plane), sagitta value, and coincidence level. Coincidence level signify the track candidate if they filled requirements of 3 station coincidence or not. Each HPT ASICs find upto 2 candidates, 3 station coincidenced candidate is higher priority one.

An encoding circuit is implemented on HPT boards for strip. Strip HPT boards are implemented a HPT chip same as HPT for wire. This encoding circuit adjust the output information to fit the strip form.

G-Link is a kind of optical fiber. Output of HPT is adopted for the G-Link. HPT ASIC output the parallel data and it is converted a serial data which processed with G-Link serializer. Output data is sent to Sector Logic of the final step of TGC trigger electronics.

### 6.2.5 Sector Logic, $R-\phi$ coincidence

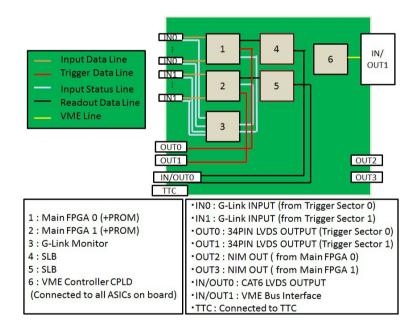

Sector Logic(SL) processes the final decision of the LVL1 Endcap Muon Trigger. SL has two important tasks;  $R-\phi$  coincidences and track selection.

SL receives G-Link serialized optical signal from HPT modules. This signal is converted to parallel data on SL board.

Sector Logic handles both wire and strip data to finds and selects high  $p_T$  muon tracks using R- $\phi$

Figure 6.17: HPT Board

Figure 6.18: Block Diagram of HPT Wire

coincidence. Each trigger sector can provide up to two trigger candidates.

SL should select the highest  $p_T$  muon tracks. Track candidates are listed and they are sorted.  $p_T$  value to select the trigger candidate is discriminated number. Six level of  $p_T$  threshold is instituted on the scheme of LVL1 Muon Trigger. A combination menu of  $p_T$  threshold is defined by ATLAS experimental plan, which is changed by progress status of the experiment and condition of detector system. Sector Logic must be composed as a rewritable system to follow such chanse and apply a new logic.

An SL selects trigger candidates which have highest  $p_T$  threshold number. This determination of  $p_T$  threshold is processed with Coincidence Window. The Coincidence Window is a kind of look up table which consists of  $p_T$  threshold versus  $\delta R$  and  $\delta \phi$ . Sector Logic is designed to apply different pattern of Coincidence Window in each ROI.

If an SL finds more than three candidates, and their  $p_T$  threshold values are same number, then track candidates which found on small  $\eta$  ROI will be primary candidate. And if an SL find some trigger candidates on same  $\eta$  ROI, then the lowest  $\phi$  ROI will be selected.

There are two output stream on SL. 34 pairs LVDS cable is adopted on SL board for trigger line output. This cable is connected to Muon Central Trigger Processor (MuCTPI).

CAT6 LVDS serial data will be sent to readout line. An SLB is adopted on a trigger sector.

More detail of functionality will be presented on next chapter.

| CLOCK      | Provided from LHC or ATLAS detector system or LTP on each subsystems.   |

|------------|-------------------------------------------------------------------------|

| L1A        | Level1 Accept. This signal is issued from CTP or LTP on each subsytems. |

| BCR        | BCID Reset signal.                                                      |

| ECR        | Event Counter Reset.                                                    |

| EVID(L1ID) | EVent IDentifier.                                                       |

| BCID       | Bunch Crossing ID.                                                      |

Table 6.1: TTC signals

### 6.2.6 SSW

Star Switch(SSW) module supports the readout process. This module send the data, which are retrieved from SLB ASICs, to Readout driver module (ROD). An SSW manages up to 23 SLBs. SSW formats the readout data and serialize to optical signal. And SSWs configures PP ASICs and SLB ASICs. Cat6 LVDS cable is connected for the communication between SLB and SSW.

### 6.2.7 TTC

Timing, Trigger and Control distribution (TTC) [24] is a system which used in all ATLAS system. Purpose of this system is to provide some signals to establish a coherence of process between all Front End electronics. TTC can provide clock and L1A to each sub systems. In addition TTC can be handled and executed a test and a calibration command.

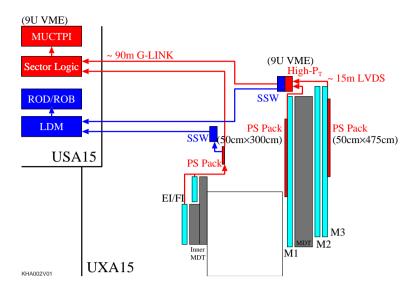

# **Chapter 7**

# The Sector Logic

Sector Logic is the final part of LVL1 Endcap Muon Trigger decision as already described. SLs are installed at a counting room USA15 in ATLAS cavern area to avoid hard radiation. USA15 is 100m away from experimental hole of UX15.

This chapter describs about hardware implementation and functions of Sector Logic.

# 7.1 Requirments

Required functions of SectorLogic are listed as following.

- Measure the transverse momentum and position of a track using wire and strip information. And select up to two muon candidates with highest  $p_T$  in each trigger sector.

- Classify the muon candidate into six levels according to measured  $p_T$ .

- Determine the ROI of the muon candidate based on measured position.

- Provide the BCID which the muon candidate belongs to.

- Process without deadtime as other LVL1 Endcap Muon Trigger electronics.