PDF issue: 2024-11-12

# A study on low-energy memory architecture for image processors

## Mori, Haruki

```

(Degree)

博士 (工学)

(Date of Degree)

2019-03-25

(Date of Publication)

2021-03-25

(Resource Type)

doctoral thesis

(Report Number)

甲第7517号

(URL)

https://hdl.handle.net/20.500.14094/D1007517

```

※ 当コンテンツは神戸大学の学術成果です。無断複製・不正使用等を禁じます。著作権法で認められている範囲内で、適切にご利用ください。

### **Doctoral Dissertation**

# A study on low-energy memory architecture for image processors

画像処理プロセッサ向け低エネルギメモリアーキテクチャ に関する研究

平成 31 年 1 月

神戸大学大学院システム情報学研究科

Haruki Mori 森 陽紀

## **Abstract**

This dissertation reports low-energy and low-cost memory architecture for real-time and energy efficient image recognition application.

Chapter 1 shows research background of this dissertation and fundamental characteristics of the multi-port static random access memory (SRAM) as an application specific image memory for the real-time motion detection processor. Then, the fundamental features of distributed deep learning and its memory system for image recognition is also described in this chapter.

In Chapter 2, intrinsic features and issues in the multi-port SRAMs as image memory and in the memory architecture of deep learning processor is described. Where, an increased SRAM operating active energy in read/write cycles and the unnecessary energy consumption on bitline (BL) in SRAM array, and an exponentially increased memory capacity and bandwidth in distributed deep learning processor, are explained. This dissertation presents a low-energy and low-cost SRAM circuit designs, and the high scalable and energy efficient deep learning algorithm/hardware development overlooking whole data-flow and memory architecture optimization.

Chapter 3 describes 1-write/2-read eight-transistor (8T) three-port SRAM design; a novel 1-write/2-read three-port SRAM based on the 8T bitcell, and the combination with majority-logic are presented.

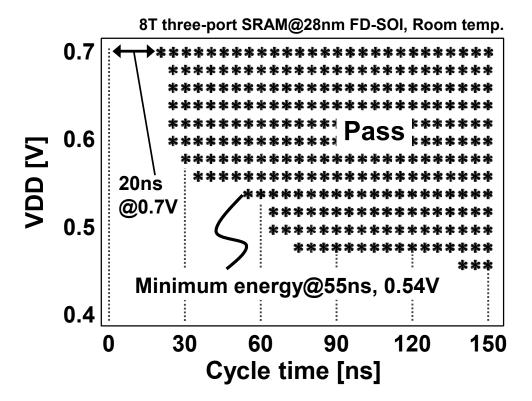

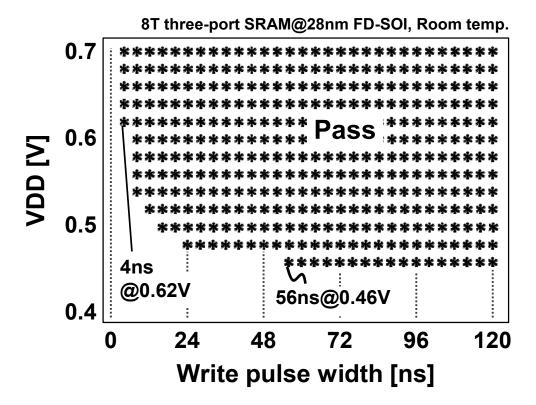

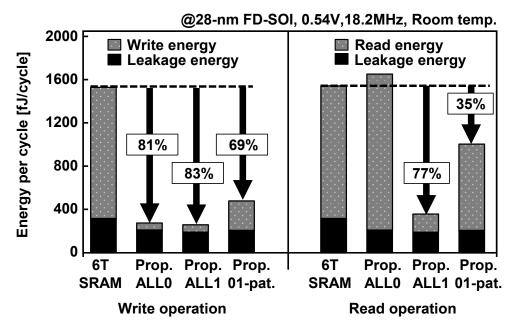

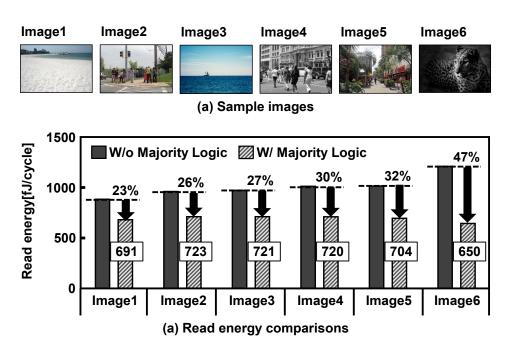

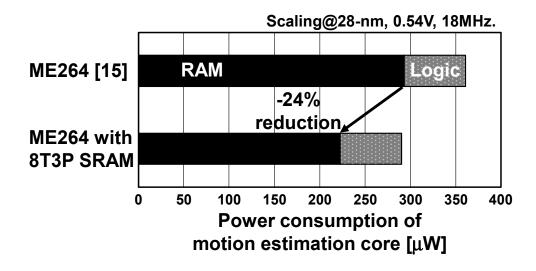

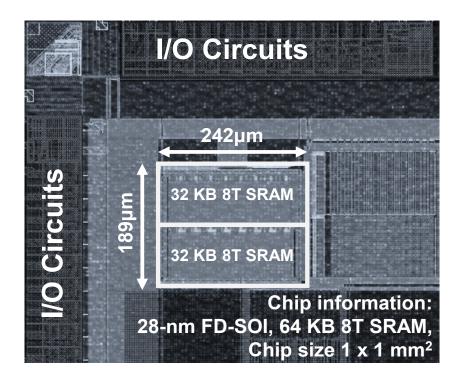

1) This study presents a low-energy and low-voltage 64-kb 8T three-port image memory using 28-nm FD-SOI process technology. Our proposed SRAM accommodates eight-transistor bit cells comprising one-write/two-read ports and a majority logic circuit to save active energy. The test chip operates at a supply voltage of 0.46 V and access time of 140 ns. The minimum energy point is a supply voltage of 0.54 V and an access time of 55 ns (=18.2 MHz), at which 484 fJ/cycle in a write operation and 650 fJ/cycle in a read operation are achieved assisted by the majority logic circuit. These factors are 69 % and 47 % smaller than those in a conventional 6T SRAM using the 28-nm FD-SOI process technology. Furthermore, the operating energy consumed on the proposed SRAM is saved by 290 μW, which signifies 24 % of energy reduction in total over the conventional H.264 motion estimation

image processor.

Chapter 4 presents two-types of BL swing reduction techniques for low-energy 8T dual-port SRAM; 1) a selective sourceline drive (SSD) scheme with the consecutive memory access and 2) an MSB-based inversion logic for low-energy 8T dual-port SRAM in image processing.

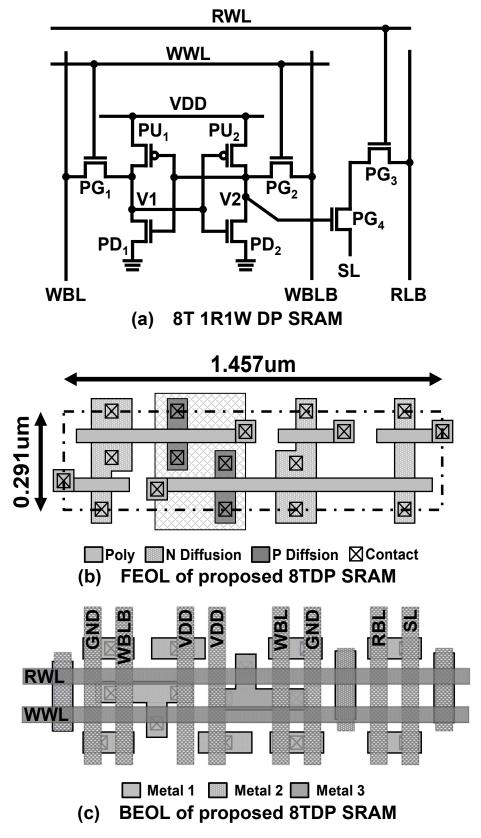

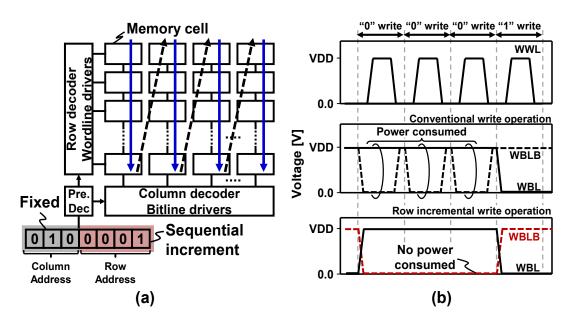

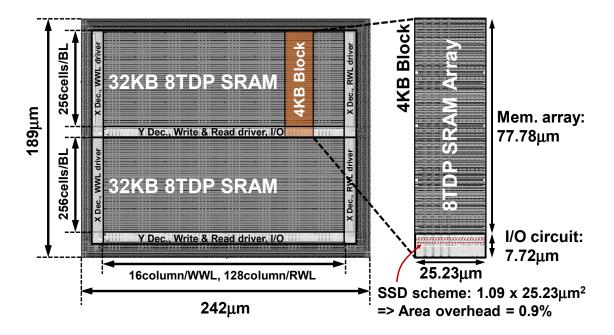

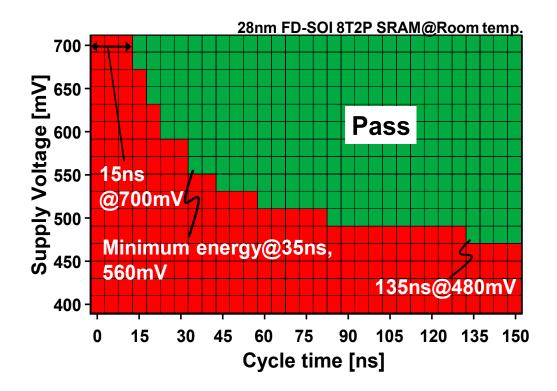

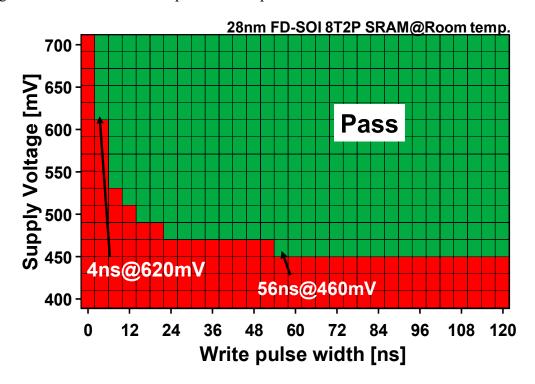

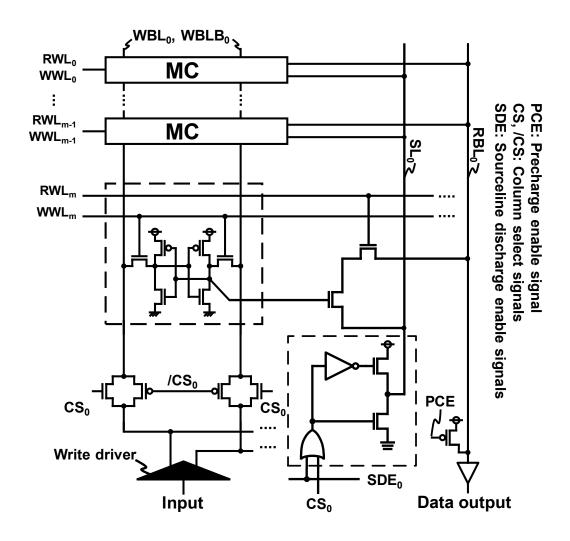

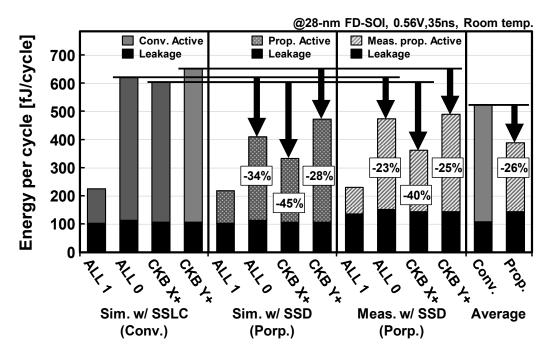

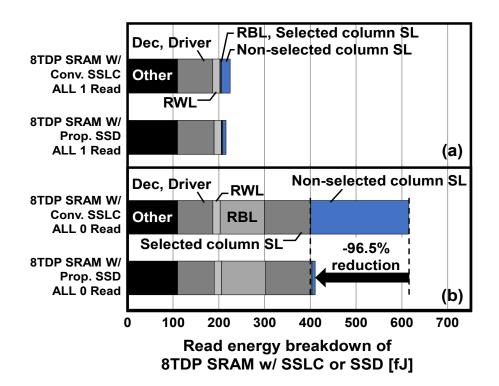

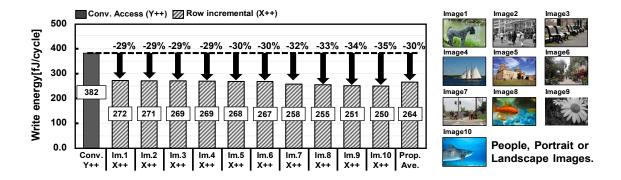

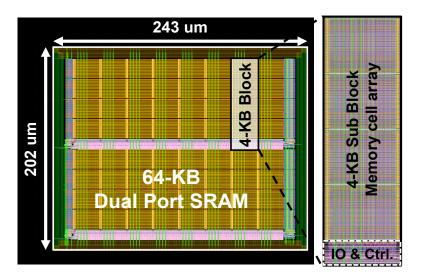

- 1) This study presents a low-energy 64-kb 8-transistor (8T) one-read/one-write dual-port image memory with a 28-nm fully depleted SOI (FD-SOI) process technology. Our proposed SRAM adopts a selective sourceline drive (SSD) scheme and a consecutive data write technique for improving active energy efficiency at low voltage. The novel SSD scheme controls sourceline voltage and eliminates leakage energy at unselected columns in read operations. We fabricated a 64-kb 8T dual-port SRAM in the 28-nm FD-SOI process technology. The 8T SRAM cell size is 0.291 × 1.457 μm². The test chip exhibits 0.48-V operation at access time of 135 ns. The energy minimum point is at a supply voltage of 0.56 V and an access time of 35 ns, where 265.0 fJ/cycle in write operations and 389.6 fJ/cycle in read operations are achieved. These factors are, respectively, 30% and 26% smaller than those of the 8T dual-port SRAM with the conventional scheme.

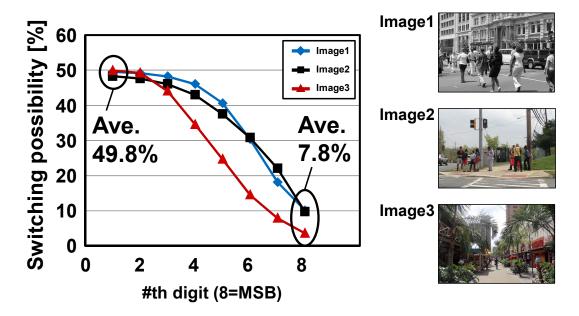

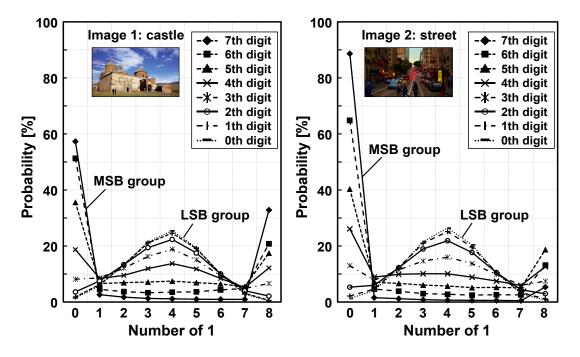

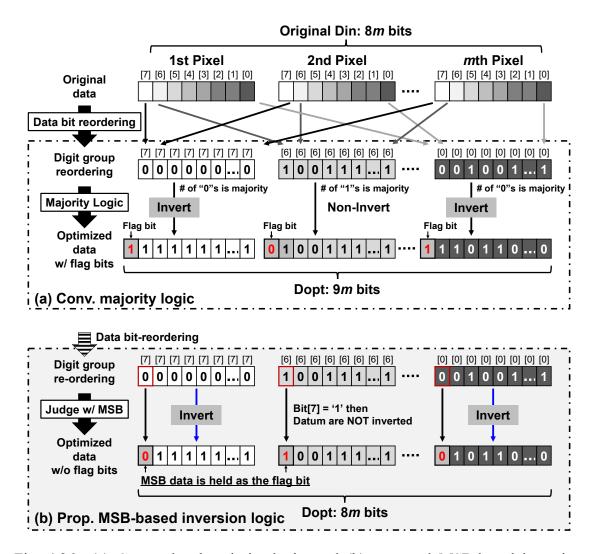

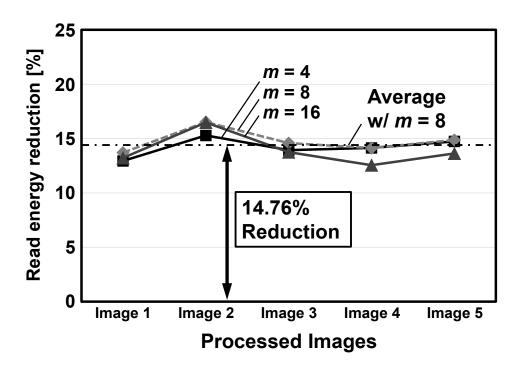

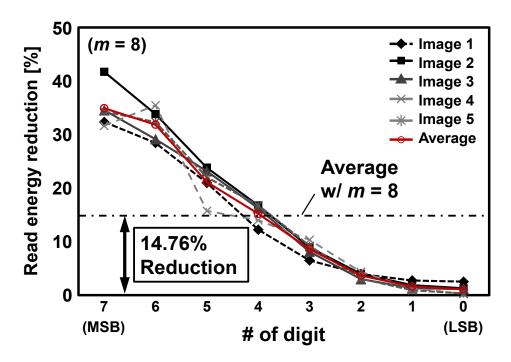

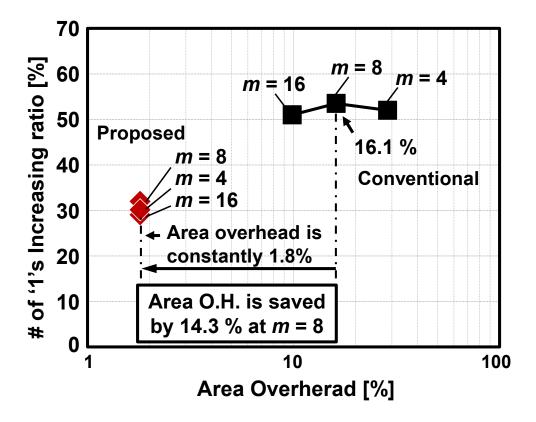

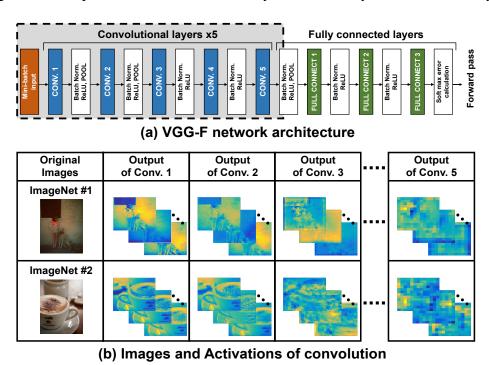

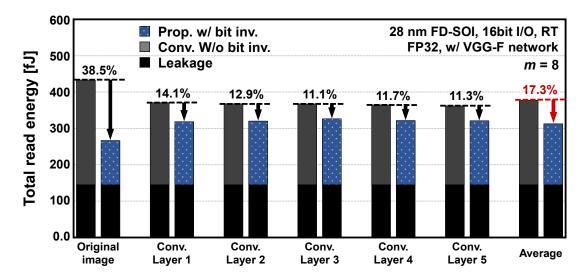

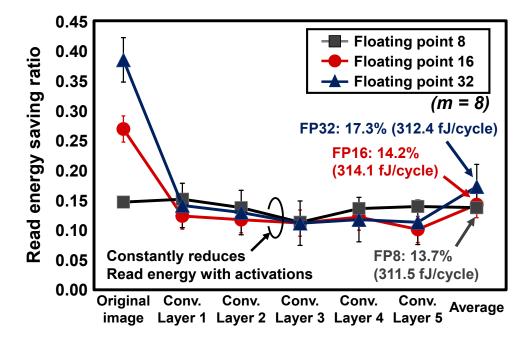

- 2) This study presents low-energy 8T dual-port SRAM with a novel MSB-based (most-significant-bit-based) inversion logic for an image processor such a deep-learning processor. Our proposed SRAM is suitable for real-time and low-power image processing, in which data have statistical correlation and data bit reordering are exploited. The proposed MSB-based inversion logic eliminates an additional flag bit in a majority logic; the MSB digit in an input datum judges whether or not to invert the datum. Thus, the area overhead of 16.1 % for the 8-bit conventional majority logic is dramatically saved. The area overhead of the proposed SRAM is merely 1.8 % for the MSB-based inversion logic. We verified that, with the proposed technique, 14.7 % of total energy can be saved in a 28-nm 64-kb FD-SOI SRAM when a set of images is read out. Furthermore, the saving factor is extended to 17.3 % when image processing in the VGG-F convolutional neural network (CNN) is considered, where 312.4 fJ/cycle in the read operation is achieved.

In Chapter 5, memory bandwidth and capacity reduction techniques with the model parallelism for high scalable distributed deep learning are described. Where, a layer-block-wise pipeline stochastic gradient decent (SGD) algorithm and its hardware architecture are proposed for distributed deep learning.

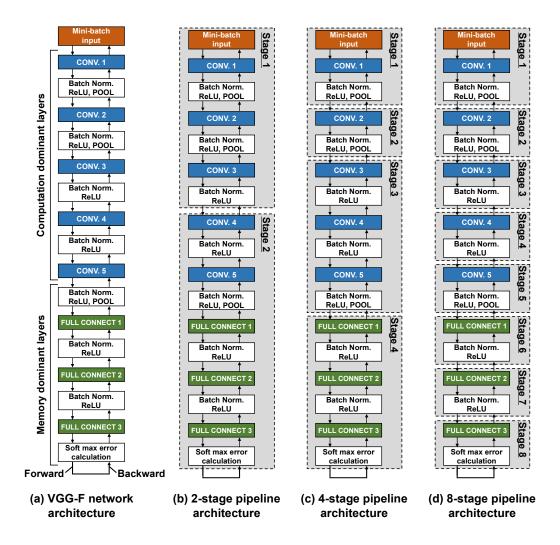

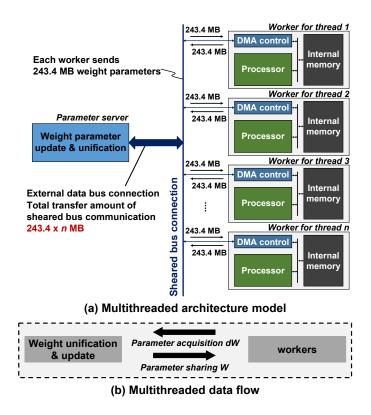

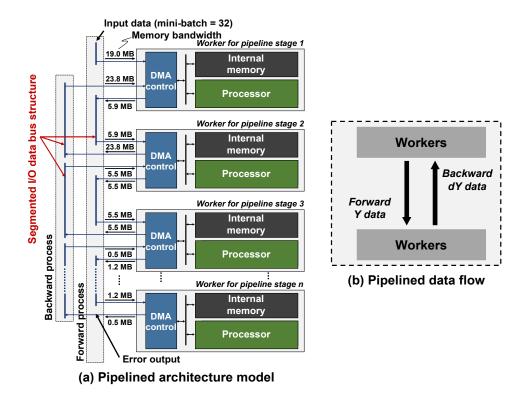

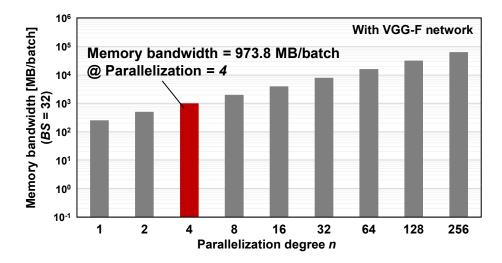

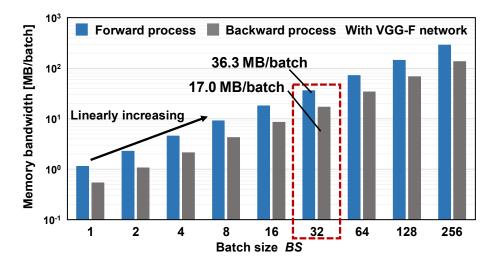

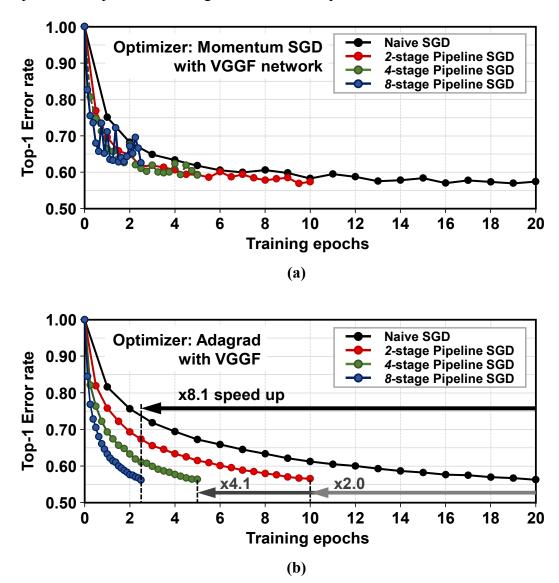

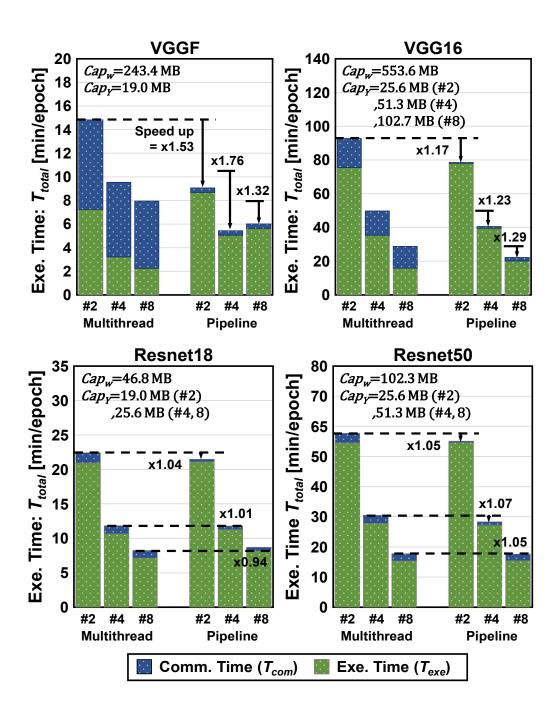

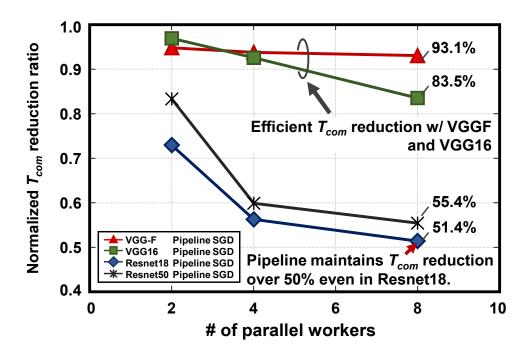

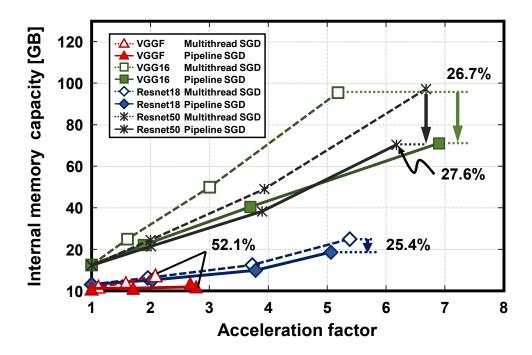

This study presents a pipelined stochastic gradient descent (SGD) algorithm and its hardware architecture with a memory distributed structure. In the proposed architecture, a pipeline stage takes charge of multiple layers: a "layer block". The layer-block-wise pipeline has much less weight parameters for network training than conventional multithreading because weight memory is distributed to workers assigned to pipeline stages. The memory capacity of 1.95 GB for the four-stage proposed pipeline is approximately half of the 3.79 GB for multithreading when a batch size is 32 in VGG-F network model. Unlike multithreaded data parallelism, no parameter server for weight update or shared I/O data bus is necessary. Therefore, the memory bandwidth is drastically reduced. The proposed four-stage pipeline only needs memory bandwidths of 36.3 MB and 17.0 MB per batch, respectively, for forward propagation and backpropagation processes, whereas four-thread multithreading requires a bandwidth of 1.21 GB overall for send and receive processes to unify its weight parameters. At the parallelization degree of four, the proposed pipeline still maintaining training convergence by a factor of 1.76, compared with the conventional multithreaded architecture although the memory capacity and the memory bandwidth are decreased.

In the final chapter 6, we summarize this dissertation. This thesis proposes the low-energy and low-cost memory architecture to realize high-speed and high-scalable image processing overlooking whole memory architecture. The work contributes to achieve an energy-efficient SRAM design for advanced technology and development of high-speed and energy-efficient image processing flame work with higher scalability.

Keywords: 8T SRAM, 28-nm SRAM, Consecutive Access, FD-SOI, Image Memory, Low Power, Multi-Port SRAM, Majority Logic, MSB-Based Inversion Logic, Deep Neural Network, Model Parallelism, Pipelined Backpropagation, Distributed Memory, Memory Capacity Reduction, Memory Bandwidth Reduction.

# **Table of Contents**

| Abstrac   | t                                                           | i    |

|-----------|-------------------------------------------------------------|------|

| Table of  | Contents                                                    | v    |

| List of I | igures                                                      | viii |

| List of T | Cables                                                      | xiii |

| Chapter   | 1 Introduction                                              | 1    |

| 1.1 I     | Background of Research Area                                 | 1    |

| 1.1.1     | The role of SRAM architecture in image processing           | 1    |

| 1.1.2     | Background of memory architecture in Deep-Learning image    |      |

| recogn    | ition processor                                             | 5    |

| 1.2       | Objectives of This Study                                    | 6    |

| 1.3       | Overview of This Dissertation                               | 7    |

| Chapter   | 2 Issue of Memory Architecture in Image Processors          | 11   |

| 2.1       | Features and issues in the SRAM architecture                | 11   |

| 2.1.1     | Fundamental features of multi-port SRAM                     | 11   |

| 2.1.2     | The issues in the multi-port SRAM                           | 16   |

| 2.2 1     | Fundamental Features and Issues of Deep Neural Network      | 19   |

| 2.2.1     | Fundamental features of deep neural network                 | 19   |

| 2.2.1     | The issue of memory architecture in the deep neural network | 22   |

| 2.3       | Summary                                                     | 25   |

| Chapter   | 23 Low-energy Multi-Port SRAM Cell Design                   | 26   |

| 3.1.1     | The multi-port SRAM design in image processor               | 26   |

| 3.1.2     | ? 1-Write/2-Read 8T three-port SRAM cell design             | 28   |

| 3.1.3     | Precharge-less write circuit                                | 33   |

| 3.1.4     | Static noise margin (SNM) in 8T 1W2R three-port SRAM        | 34   |

| 3.1.5     | Combination with majority logic                             | 36   |

| 3.1.6     | Chip implementation and measurement results                 | 37   |

| 3.2       | Summary                                                     | 43   |

| Chapter 4   | BL Swing and Leakage Reduction for 8T Dual-Port SRAM   | 44   |

|-------------|--------------------------------------------------------|------|

| 4.1 Pro     | posed Dual-Port SRAM Design                            | . 44 |

| 4.1.1       | Overview of dual-port SRAM structure                   | . 44 |

| 4.1.2       | Selective Sourceline drive (SSD) scheme                | . 46 |

| 4.1.3       | The 1R1W 8T SRAM bitcell design                        | . 51 |

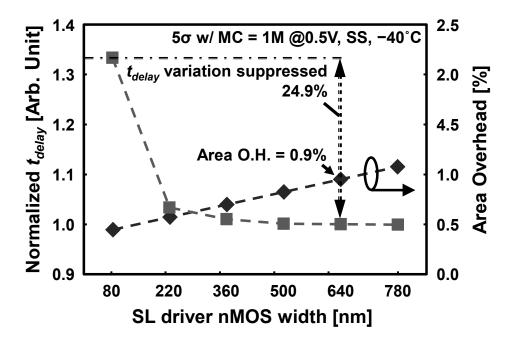

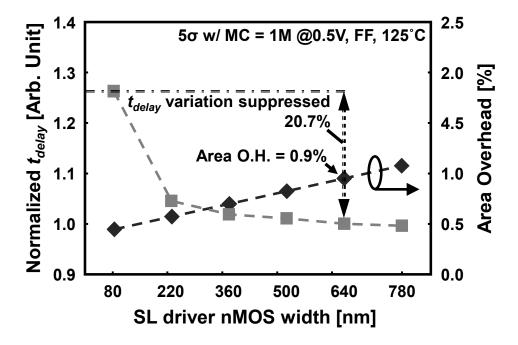

| 4.1.4       | RBL delay and area optimization in SSD scheme          | . 53 |

| 4.1.5       | Operating speed evaluation in the write cycle          | . 58 |

| 4.1.6       | Consecutive memory access in video processing          | . 59 |

| 4.1.7       | Chip implementation and measurement results            | . 61 |

| 4.2 Sur     | nmary                                                  | . 69 |

| 4.3 MS      | B Based Inversion Logic with Dual-Port 8T SRAM         | . 70 |

| 4.3.1       | Overview of dual-port SRAM and data-bit reordering     | . 70 |

| 4.3.2       | Proposed MSB based inversion logic                     | . 71 |

| 4.3.3       | Parameter optimization                                 | . 73 |

| 4.3.4       | Circuit design for MSB-based inversion logic           | . 76 |

| 4.3.5       | Performance evaluation in DL tasks                     | . 79 |

| 4.4 Sur     | nmary                                                  | . 82 |

| Chapter 5   | Co-design of the Distributed Deep Learning Accelerator | 83   |

| 5.1 Lay     | er Block Wise Pipeline                                 | . 83 |

| 5.1.1       | Overview of distributed deep learning                  | . 83 |

| 5.1.2       | Software design of layer-block-wise-pipeline           | . 85 |

| 5.1.3       | Hardware model and evaluation                          | . 88 |

| 5.1.4       | Performance evaluation                                 | . 92 |

| 5.2 Sur     | nmary and Discussion                                   | . 98 |

| Chapter 6   | Conclusion                                             | 99   |

| References  | s                                                      | 103  |

| List of Pub | olications and Presentations                           | 112  |

| Publication | ons in journals and transactions                       | 112  |

| Presentat   | ions at international conferences                      | 112  |

| Invited pr  | resentations at domestic conferences                   | 113  |

| Presentat   | ions at domestic conferences                           | 113  |

| Acknowledgement |   | 116 | 3 |

|-----------------|---|-----|---|

|                 | , |     | • |

# **List of Figures**

| 1.1  | Trend of power consumption in SoCs; the memory consumes over 50% of            |

|------|--------------------------------------------------------------------------------|

|      | whole energy in image processor                                                |

| 1.2  | The memory system in image processor                                           |

| 1.3  | The energy breakdown in the HOG processor; the memory has impact its           |

|      | energy performance                                                             |

| 1.4  | The device structure of FD-SOI process technology; the BOX layer and           |

|      | ultra-thin silicon body provides better electrostatic behavior                 |

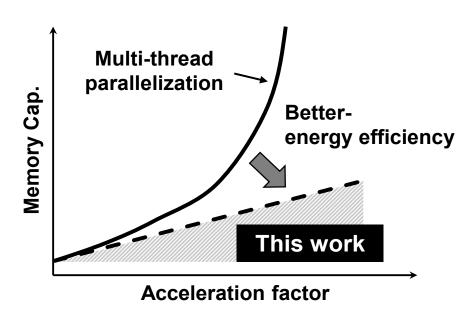

| 1.5  | The relationship between the total memory size and the acceleration factor     |

|      | when using highly parallelized deep learning; this work targeted high scalable |

|      | and energy efficient deep learning5                                            |

| 1.6  | Overview of this dissertation9                                                 |

| 2.1  | Variation of commonly composed single-ported and multi-ported 6T, 8T,          |

|      | and 10T SRAM bitcells                                                          |

| 2.2  | Block diagram of SRAM array                                                    |

| 2.3  | Block diagram of memory system in the multi-core processor                     |

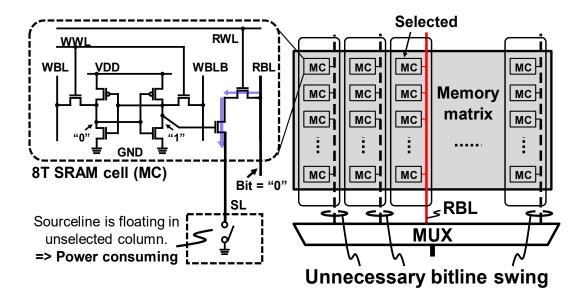

| 2.4  | Circuit schematic of sourceline (SL) structure, and current flow model of      |

|      | unnecessary read current at the unselected column in conventional 8T SRAM      |

|      | cells with single-ended read ports                                             |

| 2.5  | The concept of convolutional neural network (CNN)                              |

| 2.6  | The correlation between the accuracy and the deepnesss of network model        |

|      | [31]                                                                           |

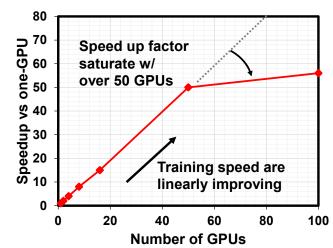

| 2.7  | The relationship between the acceleration factor and the .number of workers.   |

|      | The acceleration factor saturates over 50 GPUs situation [32]                  |

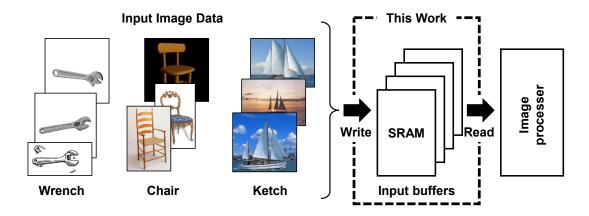

| 3.1  | Memory system in image processing. This work targeted the development of       |

|      | low-power and low-cost image memory                                            |

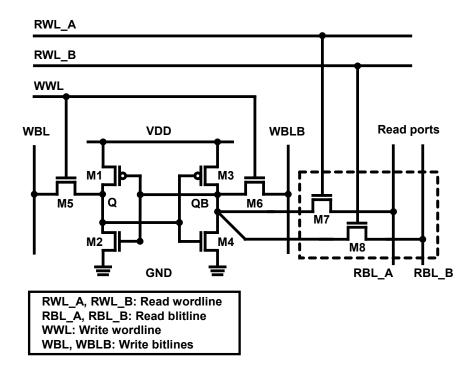

| Fig. | 3.2 Schematic of proposed 8T three-port SRAM with single ended read ports      |

|      |                                                                                |

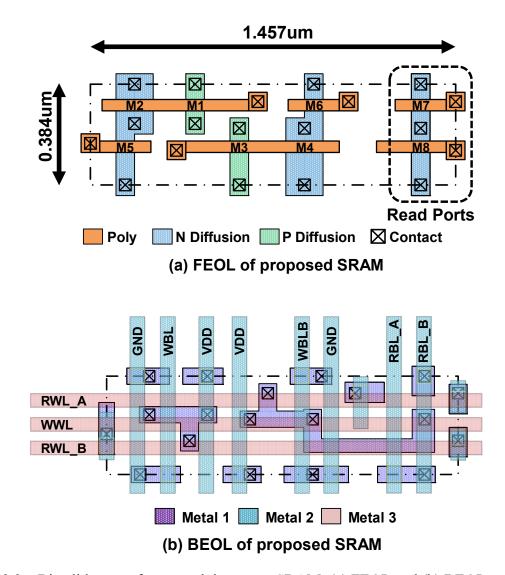

| 3.3  | Bitcell layout of proposed three-port SRAM: (a) FEOL and (b) BEOL 30           |

| 3.4  | Waveforms of proposed 8T three-port SRAM in read operation; (a) Wordline       |

|      | pulse, (b) when the Node QB holds "0" data, (c) when Node QB holds "1"         |

|      | data                                                                          |

|------|-------------------------------------------------------------------------------|

| 3.5  | Schematic of the proposed 8T three-port SRAM and write/read current flow      |

|      | model, (a) when the Node QB holds "0" data, (b) when Node QB holds "1"        |

|      | data                                                                          |

| 3.6  | Schematics of write circuits between conventional SRAM and proposed           |

|      | SRAM architecture: (a) conventional circuit and (b) precharge-less circuit 33 |

| 3.7  | Waveforms in the write operation: (a) Write wordline (WWL) pulse, (b)         |

|      | Write bitline (WBL and WBLB) signals in a conventional write circuit and (c)  |

|      | a precharge-less write circuit.                                               |

| 3.8  | Variety of access situations in the proposed 1-W/2-R three-port SRAM 35       |

| 3.9  | Simulated butterfly curves at several Vdd from 1.0 V down to 0.4 V: (a)       |

|      | single-port read out and (b) dual-port read out                               |

| Fig. | 3.10 Concept of SRAM with majority logic.(a) Block diagram, and (b) flag      |

|      | bit                                                                           |

| 3.11 | Power reduction ratio at each digit in majority logic                         |

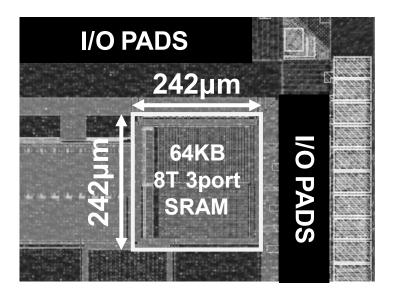

| 3.12 | Test chip micro photograph of proposed 8T three-port SRAM                     |

| 3.13 | Measured read Shmoo plot                                                      |

| 3.14 | Measured write Shmoo plot                                                     |

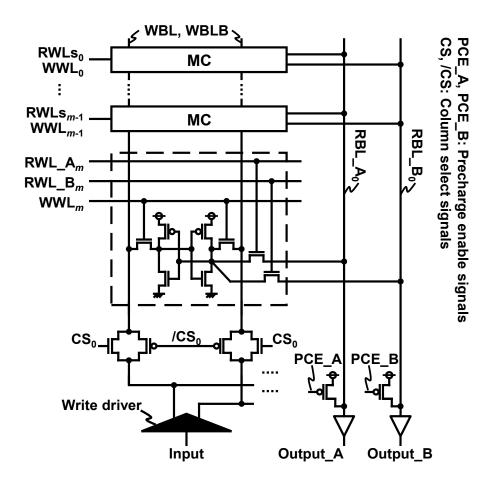

| 3.15 | Schematic of proposed 8T three-port SRAM array and its peripheral circuits    |

|      | 40                                                                            |

| 3.16 | Measured write energies, read energies, and comparisons with conventional     |

|      | 6TSRAM                                                                        |

| 3.17 | Read energies saved by majority logic in actual image data                    |

| 3.18 | Estimated power consumption of motion estimation image processor 42           |

| 4.1  | Read energies saved by majority logic in actual image data                    |

| 4.2  | Conventional 8T SRAM memory matrix with the SSLC scheme. Unselected           |

|      | SLs are floating because of an nMOS switch. They consume unnecessary          |

|      | energy                                                                        |

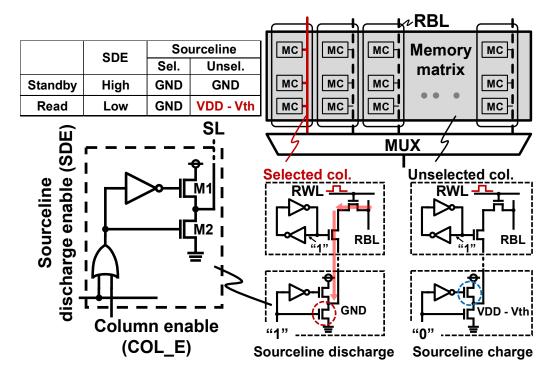

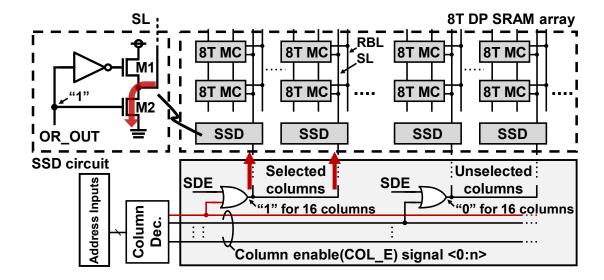

| 4.3  | Concept of proposed 8T SRAM with the selective sourceline drive (SSD)         |

|      | scheme in the read operation. 47                                              |

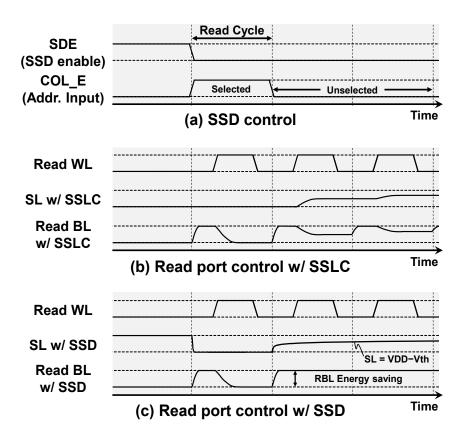

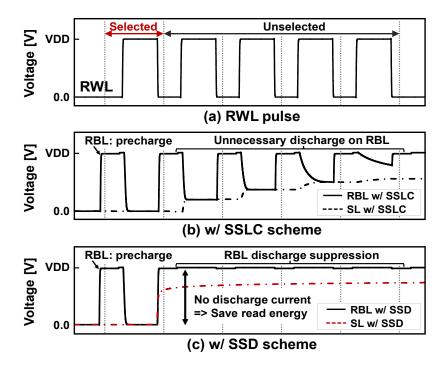

| 4.4  | Column control in the proposed SSD scheme in read operation                   |

| 4.5  | Signal timing control flow in the conventional SSLC and the proposed SSD      |

|      | scheme in read operation: (a) SSD control signals, (b) read port control       |

|------|--------------------------------------------------------------------------------|

|      | signals with the SSLC scheme, and (c) read port control signals with the SSL   |

|      | scheme. 49                                                                     |

| 4.6  | Simulated "0"-read operating waveforms: (a) RWL waveform commonly              |

|      | used in the conventional SSLC scheme and the proposed SSD proposed             |

|      | scheme, (b) RBL and SL waveforms in the conventional SSLC scheme, and          |

|      | (c) RBL and SL waveforms in the proposed SSD scheme                            |

| 4.7  | Proposed 8T 1R1W dual-port SRAM cell in a 28-nm FD-SOI: (a) circuit            |

|      | design, (b) FEOL layout design, and (c) BEOL layout design                     |

| 4.8  | Read bitline (RBL) delay tdelay and area overhead versus the gate width option |

|      | of the SL pull-down nMOS transistor M2 (SS corner, -40°C). The slowest         |

|      | RBL delays at each gate width size are shown                                   |

| 4.9  | Read bitline (RBL) delay tdelay and area overhead versus the gate width option |

|      | of the SL pull-down nMOS transistor M2 (FF corner, 125°C): The fastes:         |

|      | RBL delays at each gate width size are shown                                   |

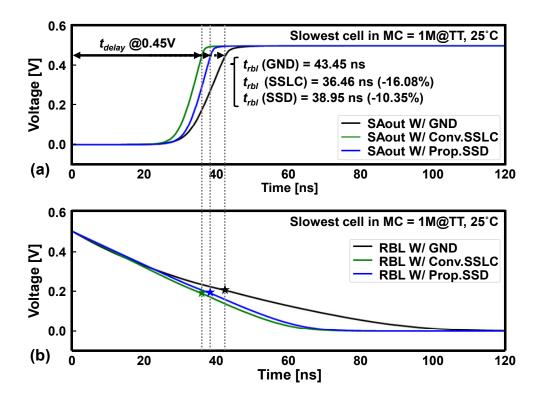

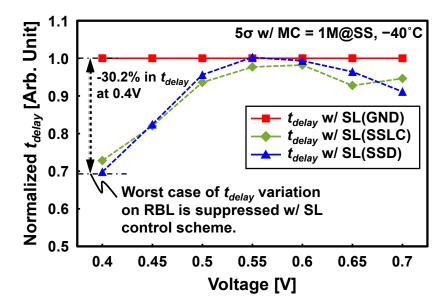

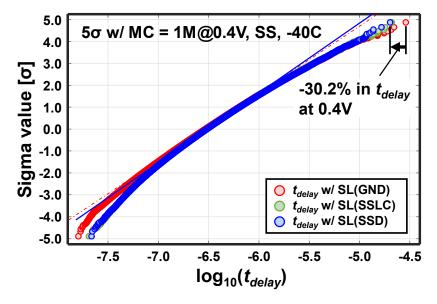

| 4.10 | Simulated read out delay comparison between conventional grounded SL           |

|      | conventional SL with SSLC scheme, and proposed SL with SSD scheme 55           |

| 4.11 | Simulated read out delay comparison on slowest cells at varied supply          |

|      | voltage between conventional grounded SL, conventional SL with SSLC            |

|      | scheme, and proposed SL with SSD scheme. 57                                    |

| 4.12 | tdelay distributions in the conventional grounded SL, the conventional SI      |

|      | with the SSLC scheme, and the proposed SL with the SSD scheme on a             |

|      | quantile-quantile plot. 57                                                     |

| 4.13 | Consecutive memory access in video processing: (a) block diagram and (b)       |

|      | waveforms in write operation. 58                                               |

| 4.14 | Switching possibility in image data                                            |

| 4.15 | Consecutive memory access in video processing: (a) block diagram and (b)       |

|      | waveforms in write operation. 60                                               |

| 4.16 | A 64-kb SRAM (32 kb × 2 bank) macro layout design comprises 16 × 4-kb          |

|      | subarray block (= 256 × 16 cells)                                              |

| 4.17 | Chip micrograph of the test chip. 62                                           |

| 4.18 | Measured Shmoo plot in read operation                                          |

| 4.19 | Measured Shmoo plot in Write operation                                       |

|------|------------------------------------------------------------------------------|

| 4.20 | Schematic of the proposed 8T dual-port SRAM with the SSD scheme 64           |

| 4.21 | Simulated and measured energy comparisons between the conventional           |

|      | SSLC scheme and the proposed SSD scheme in read operation                    |

| 4.22 | Simulated energy breakdown comparison between the conventional SSLC          |

|      | scheme and the proposed SSD scheme in (a) "ALL 1" and (b) "ALL 0" read       |

|      | operations. 66                                                               |

| 4.23 | Write energy saving in incremental accesses                                  |

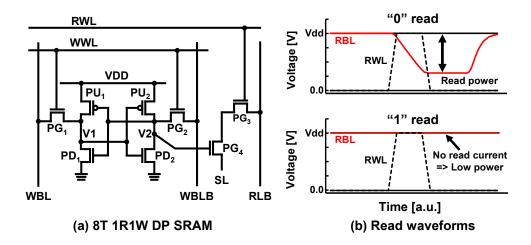

| 4.24 | 8T 1R1W Dual-port SRAM (a) schematic and (b) Operating waveforms             |

|      | when "0" or "1" read operation                                               |

| 4.25 | Distributions of the number of "1"s in different digit groups, analyzed with |

|      | HD size image (Image 1: castle, and Image 2: street)                         |

| 4.26 | (a) Conventional majority logic, and (b) proposed MSB-based inversion        |

|      | logic: both logic use the data bit reordering                                |

| 4.27 | Normalized read energy reduction ratio in the proposed MSB-based bit         |

|      | inversion with data bit reordering: comparison in each image                 |

| 4.28 | Normalized read energy reduction ratio in the proposed MSB-based bit         |

|      | inversion with data bit reordering: comparison at each digit                 |

| 4.29 | Area overhead comparison between the conventional majority logic and the     |

|      | proposed MSB-based inversion logic in peripheral circuitry                   |

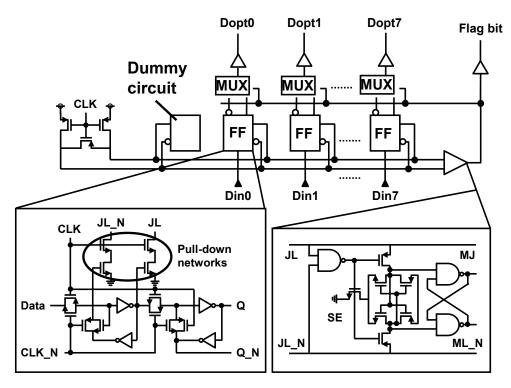

| 4.30 | The conventional majority logic: write circuitry schematics                  |

| 4.31 | The conventional majority logic: (a) simulated waveforms when "0" is the     |

|      | majority, and (b) waveforms when "1" is the majority in write operation 77   |

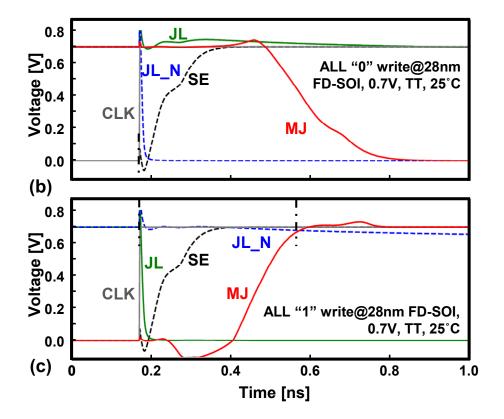

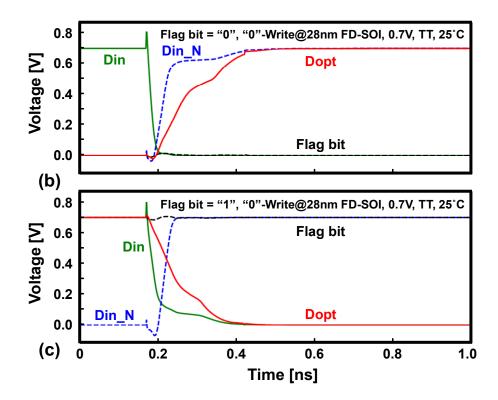

| 4.32 | The proposed MSB-based inversion logic: (a) write circuitry schematics 78    |

| 4.33 | The proposed MSB-based inversion logic: (b) when the flag bit = "0", and     |

|      | (c) when the flag bit = "1"                                                  |

| 4.34 | Chip layout design of the proposed SRAM                                      |

| 4.35 | (a) VGG-F with CNNs, and (b) samples of input images and activations of      |

|      | the convolutional layers generated by the VGG-F                              |

| 4.36 | Measured read energy comparison with FP32 in 28nm FD-SOI                     |

| 4.37 | Read energy reduction ratios in FP8, FP16, and FP32 precisions               |

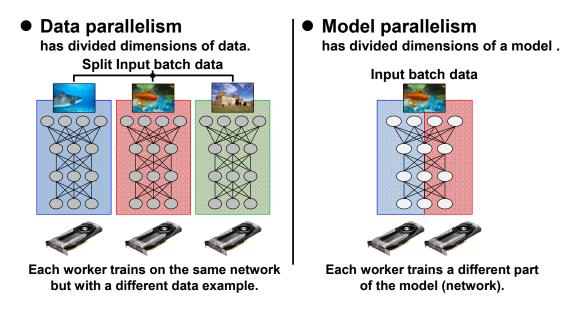

| 5.1  | The conceptual models of data parallelism and model parallelism              |

## xii List of Figures

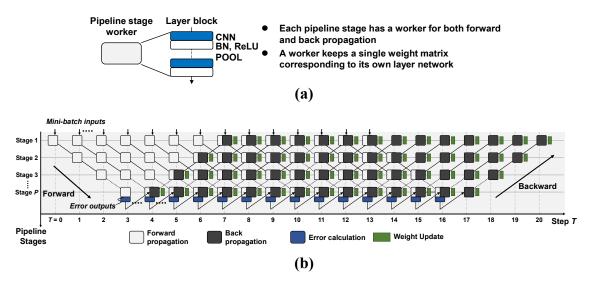

| 5.2  | Concept of layer block wise pipeline; (a) Pipeline stage and layer-block, (b)   |

|------|---------------------------------------------------------------------------------|

|      | Conceptual data-flow diagram of the proposed layer-block-wise pipeline with     |

|      | weight update latency.                                                          |

| 5.3  | Partitioning variations for VGG-F in the layer-block-wise pipeline; (a)         |

|      | VGG-F network architecture, (b) Partitioning for 2-stage pipeline architecture, |

|      | (c) Partitioning for 8-stage pipeline architecture                              |

| 5.4  | (a) Architectural model of shared-bus multithreading and (b) its data flow 90   |

| 5.5  | (a) Architectural model of the layer-block-wise pipeline and (b) its data flow. |

|      | 90                                                                              |

| 5.6  | Memory bandwidth trends against the parallelization degree in                   |

|      | multithreading92                                                                |

| 5.7  | Memory bandwidth trends against the batch size in the layer-block-wise          |

|      | pipeline. 92                                                                    |

| 5.8  | Training convergence comparison for parallelization degrees of 1, 2, 4, and 8   |

|      | with (a) Momentum SGD, (b) SGD using the Adagrad LR adaptation 94               |

| 5.9  | Total execution time $T_{total}$ comparisons and breakdown mapping for each     |

|      | networks between the conventional multithread and the proposed pipeline 96      |

| 5.10 | Normalized Tcom reduction ratio comparisons between the conventional            |

|      | multithread and the proposed layer-block-wise pipeline in various network       |

|      | models with number of parallel workers 2, 4, and 8 97                           |

| 5.11 | Relationship between the internal memory capacity and the acceleration          |

|      | factor for the conventional multithread and the proposed pipeline               |

|      |                                                                                 |

# **List of Tables**

| 3.1 | Transistor W/L sizes in the proposed SRAM cell. The proposed 8T SRAM          |

|-----|-------------------------------------------------------------------------------|

|     | cell is designed on the logic rule bases                                      |

| 3.2 | Overview of the configurations of the implemented test chip 41                |

| 4.1 | Statistical data comparison between different SL-structure in read operation. |

|     |                                                                               |

| 4.2 | Tast chip features. 67                                                        |

| 4.3 | Dual-Port 8T SRAM Comparison. 68                                              |

| 4.4 | Specifications: input images and activation of convolutions                   |

| 5.1 | Memory capacity and memory bandwidth in conventional multithreads 91          |

| 5.2 | Memory capacity and memory bandwidth in proposed pipeline                     |

# Chapter 1 Introduction

#### 1.1 **Background of Research Area**

#### 1.1.1 The role of SRAM architecture in image processing

The work for this dissertation is twofold. First, I implemented low-power and low-voltage embedded static random access memory (SRAM) design aiming high energy efficiency on real-time image recognition processor. I also developed a high-speed and an energy-efficient distributed deep-learning (DL) algorithm and its hardware accelerator overlooking whole data flow and memory architecture optimization.

Low-energy image recognition is demanded for internet of things (IoT) devices in various fields such as safety driving systems, machine vision and augmented reality (AR) systems with fine resolution. Image resolution enhancement requires large memory capacity and large chip area. It also entails higher energy consumption because of the increased amounts of image data that must be processed. The memory capacity and area cost is relatively increased than the cost of logic part and other peripheral circuit according to the technology scaling. In fact, the power consumption in memory (global memory, caches, and register files) dissipates more than 40 % of the energy of the image processor (e.g. GTX 580, Nvidia Corp.) [1]. For IoT devices handling image information, more energy-efficient memory technology is anticipated.

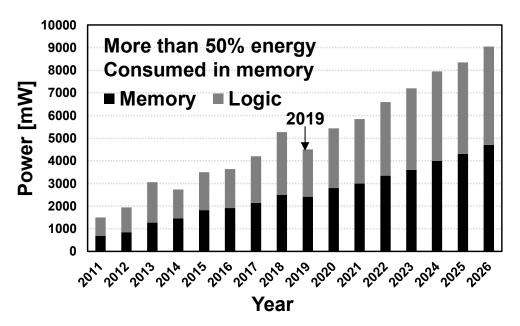

SRAM is the most common type of the embedded memories for the modern SoCs. SRAM has better compatibility to logic circuits and faster random access performance than the other memories. Processors leverages SRAM as the first level cache memory, a scratch pad memory and a main memory on a video coding system and image recognition system. As process technology is scaled down, SRAM occupies over 50% of the total area and 65% of the total power in 2022 [2], as shown in Fig. 1.1. Therefore, SRAM must play an integral role in the power, performance, and an area of the modern SoCs.

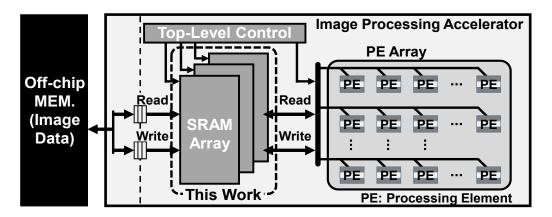

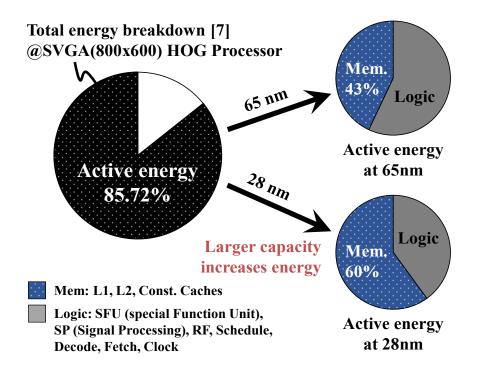

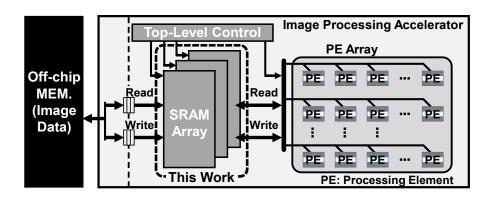

Input data for image processing are stored temporarily in SRAM. In an image processor, many processing cores access SRAM for multi-thread processing. Fig. 1.2 portrays the memory system in an image processing unit. The SRAM array stores data such as image maps, feature maps, and various parameters for its processing on the many processing elements (PE). Demand for multi-port SRAMs has increased to accommodate high-speed, low-energy image processing. The multi-port SRAM is suitable for parallel operation. It improves the total chip performance and/or memory bandwidth by enabling multiple simultaneous operations in the same bank [3]. Parallel processing is a key technology for real time image applications that require embedded memories with multiple access ports [4–6]. However, the energy reduction of SRAM part is remaining important challenges for future IoT devices. Actually, as the transistor scaling, larger SRAM capacity than ever will be implemented in an SoCs. Fig. 1.3 shows the energy consumption of SRAM in whole image processor. 43% of energy is consumed in SRAM part manufactured by 65 nm process [7], while the energy consumption of SRAM part is increased to 60% in 28 nm process technology. To date, multiport SRAMs that support simultaneous write and read operations with low-energy operation have been proposed for use as image processors [8–10].

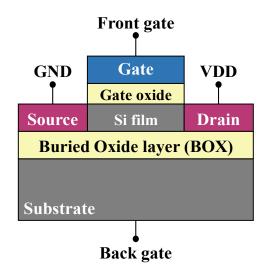

Low-voltage operation is one of the primary challenges for active-power improvement, but the minimum operating voltage ( $V_{min}$ ) of SRAM part is remaining still higher than the  $V_{min}$  of logic part in SoCs. Fully depleted silicon on insulator (FD-SOI) process technology is one of the promising ways to provide high-speed and low-voltage SRAM [11, 12]. Figure 1.4 depicts the simplified device structure in the FD-SOI process technology. A 28-nm FD-SOI process technology is a fine process, that has a fully depleted transistor with an ultra-thin silicon body and a thin buried oxide (BOX) layer, giving them excellent electrostatic control in near-threshold voltage region. Therefore, it brings stable features at low-voltage operation. The BOX layer reduces the leakage current by controlling the electrical flow in a transistor from a source node to a drain node. Moreover, the BOX layer suppresses the parasitic capacitance between the source node and the drain node. These features of the 28-nm FD-SOI process technology realize the production of ultra-low-power SRAM design [13–17].

Energy efficiency of SoCs is improved in the near-threshold region because dynamic energy and leakage energies are well balanced [18]. The combination of a low threshold voltage and low supply voltage is beneficial for high-activation logic circuitry, whereas a high threshold voltage and a high supply voltage are suitable for memory operations.

Trend of power consumption in SoCs; the memory consumes over 50% of whole energy in image processor.

The memory system in image processor.

For memory, the activation is low because only a selected wordline (WL) and certain bitlines are activated. In such cases, the high threshold voltage suppresses the leakage current and total energy. Process technologies such as fin field-effect transistor (Fin-FET) and FD-SOI have a smaller S-factor. Moderate threshold voltage and moderate supply voltage achieve the best scenario, especially for memory [19–22]. However, the SRAM also tends to be affected by process variation (local variation and global variation) in the low voltage region. The low-power and proper SRAM circuit design is more important than ever. Thus, consequently, SRAM has imperative issues of energy dissipation, minimum operating voltage, and variation effect in the deep submicron technology.

Fig. 1.3 The energy breakdown in the HOG processor; the memory has impact its energy performance.

- FD-SOI has been adopted in the 28nm node [11].

- Improving transistor behavior, especially at low supply voltage.

- 28nm FD-SOI enables an ultra-low power SRAM design [14].

- Thicker gate dielectric reduced gate leakage.

Fig. 1.4 The device structure of FD-SOI process technology; the BOX layer and ultra-thin silicon body provides better electrostatic behavior.

#### 1.1.2 Background of memory architecture in Deep-Learning image recognition processor

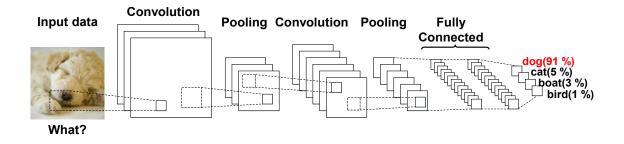

The perceptron, a primitive artificial neural network, has a single layer comprising input synapses and output neurons as nonlinear activations [23]. The multilayer perceptron is an extension of the single-layer perceptron with hidden layers, in which training is conducted through backpropagation [24]. A convolutional neural network (CNN) imitates part of the human visual cortex in the cerebrum. It is an extension of a multilayer perceptron.

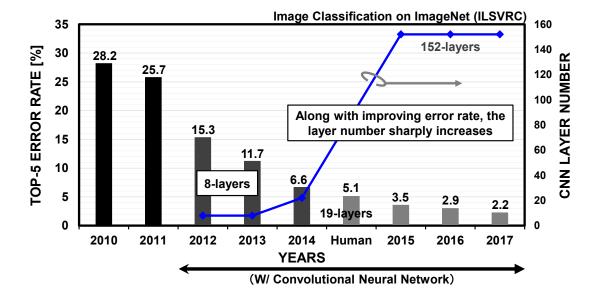

Recently, a deeper network having more than three layers is generally called as a "deep neural network (DNN)" or "deep learning". The DNN has exhibited its potential for image recognition ability. Its accuracy is improving year by year. At the ImageNet Large Scale Visual Recognition Competition (ILSVRC), AlexNet with five CNN layers and three fully connected layers made an overwhelming achievement over conventional feature-based image recognition schemes in 2012 [25]. Its top-five error rate was 15.3%, which was more than 10 % better than the second-best entry based on the handmade features. Since 2012, the error rate in image recognition has been improved by DNNs. At ILSVRC 2015, ResNet, comprising with 151 CNN layers and one fully connected layer, remarkably won the competition by a top-five error rate of only 3.57 % [26],

Fig. 1.5 The relationship between the total memory size and the acceleration factor when using highly parallelized deep learning; this work targeted high scalable and energy efficient deep learning.

which is better than the 5.1% figure representing human ability [27]. Today, DNNs are applied mainly to image recognition applications, but DNNs themselves has general-purpose characteristics and abilities; DNNs are now attracting attention not only in for engineering, but also for use in medicine, pharmacy, and biology applications [28]. The development of deep learning technology is expected to contribute to the improvement of wide range industrial fields.

Figure 1.5 shows a trend of memory capacity versus acceleration factor in distributed deep learning. In the conventional multi-thread parallelism, the memory capacity increases lineally. However, because of the memory bandwidth of communication between the parameter server and many workers, the acceleration factor saturates in the middle of parallelization degree. In this case, it is not faster even with a lot of graphics processors. The conventional parallelism has scalability constraints in its memory structure. The communication delay on the data bus and the huge memory capacity with duplicated network, which degrades scalability and increase energy consumption. When considering the future networks that have numerous layers must be trained by numerous users in various industrial fields, the existing computing resource is not sufficient to satisfy the deserved accuracy, although we use the highly paralleled GPGPUs. In order to improve such issues, more high-scalable algorisms and low-cost hardware architecture is anticipated. Therefore, our target is low-cost and high-scalable deep learning flame work.

# 1.2 Objectives of This Study

This dissertation focuses on application specific design of memory architecture for low-power, real-time and high-scalable image processors.

The first objective of this study is active energy reduction in read and write operation of multi-port SRAMs. The multi-port SRAM is suitable for parallel operation. In particular, an image processor requires larger multi-port SRAM capacity. Therefore, its energy consumption is drastically increased by higher resolution. Consequently, multi-port SRAMs with lower active or standby energies have become more important than ever. All the SRAMs in this dissertation employ eight-transistors (8T) multi-port SRAM bitcells (the 8T three-port SRAM, and two-types of 8T dual-port SRAM) with improved active or leakage energy.

The second objective is to decrease leakage energy consumption for further energy reduction. In submicron process technologies, the leakage and unnecessary current are more critical than those by larger technology nodes. This study presents selective sourceline (SL) drive circuit technics to eliminate unnecessary current in unselected read bitlines (RBLs) and to effectively improve the energy efficiency in read operation. Another dual-port design proposes the most significant bit (MSB) based inversion logic. This circuit technique reduces the number of RBL swing for low-energy operation especially in the image recognition deep learning tasks.

The third objective is to decrease the memory bandwidth and the memory capacity in the distributed deep learning. The highly parallelized deep learning for image recognition is suffering from the scalability deterioration by increased data bus communication between a lot of parallel workers. The large amount of memory bandwidth increases communication delays in data bus and therefore computational time is also increased. Furthermore, it entails higher energy consumption in memory with increased number of memory access. The objective of this study is to develop a high throughput deep learning system which accelerates the training period. The co-design of algorism and hardware architecture enables development of optimized memory architecture and parallel data flow. For this purpose, we propose a novel layer-block-wise-pipeline algorism and its architecture to reduce memory bandwidth and memory capacity with segmented data bus architecture and distributed memory architecture. In this dissertation, we discuss multiple versions of parallelization models and compare them.

#### 1.3 **Overview of This Dissertation**

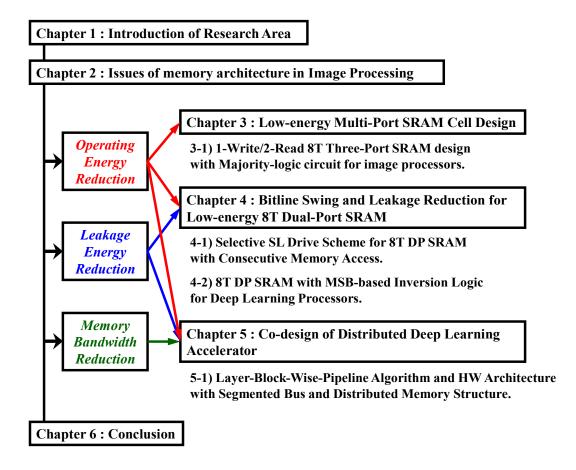

Figure 1.6 illustrates an overview of this dissertation. Firstly, I explain the background, objectives, and overview of this study in chapter 1. Secondly, the issues of memory architecture in image processing technique are presented in chapter 2. In this dissertation, the novel techniques are explained to address the issues which are denoted in chapters 3, 4, and 5.

Chapter 3 presents one-write/two-read (1W/2R) 8T three-port SRAM design and implementation. Here, a novel 1W/2R three-port SRAM with 8T bitcell is proposed. The combination of the proposed SRAM and a majority logic circuit exhibits low-energy performance. The proposed 8T three-port SRAM accommodates eight-transistor bit cells comprising one-write/two-read ports and a majority logic circuit to save active energy. We fabricated a 64-kb 8T three-port SRAM using 28-nm FD-SOI process technology and compared it with conventional ten-transistor (10T) three-port SRAM in ME264 (with H.264 codec) motion estimation image processor.

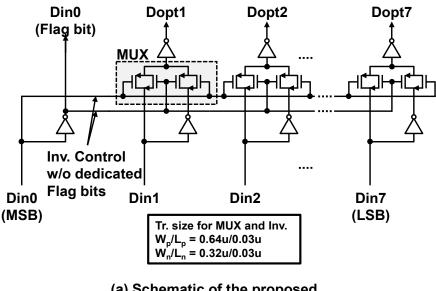

In Chapter 4, two types of BL swing and leakage reduction technique for low-energy 8T dual-port SRAM. Firstly, a low-energy 8T dual-port image memory with sourceline drive technique is presented. The proposed 8T dual-port SRAM with selective sourceline drive (SSD) scheme improves active energy efficiency at the low-voltage. We implemented a 64-kb 8T dual-port SRAM in the 28-nm FD-SOI process technology. Secondly, an 8T dual-port SRAM with a novel most significant bit (MSB) based inversion logic is presented to save the active energy on RBLs. Our proposed SRAMs are advantageous for real-time and low-power image processing, in which data have statistical correlation. Furthermore, the proposed MSB based inversion logic eliminates an additional flag bit, therefore, our SRAMs have smaller area overhead than the conventional scheme.

Chapter 5 introduces memory bandwidth and capacity reduction techniques for high-scalable parallelism in distributed deep learning. The layer-block-wise pipeline algorithm and its hardware architecture are presented to speedup the stochastic gradient descent (SGD) algorism with low cost. In the proposed architecture, a pipeline stage takes charge of multiple layers: a "layer block". The layer-block-wise pipeline has much less weight parameters for network training than conventional multithreading because weight memory is distributed to workers assigned to pipeline stages. Unlike multithreaded data parallelism, no parameter server for weight update or shared I/O data bus is necessary. Therefore, the memory bandwidth and internal memory capacity are drastically reduced in the deep learning processors.

Finally, the conclusion of this dissertation is summarized in Chapter 6. This thesis consistently presents the energy efficient and low-cost memory architecture for high-speed, low-energy and high-scalable image processors overlooking whole memory architecture in future image applications.

Fig. 1.6 Overview of this dissertation.

# Chapter 2 Issue of Memory Architecture in Image Processors

As described in the previous chapter, the memory architecture plays significant role to optimize memory flow in the image processing. It influences energy, area, and the whole performance in the image processors. In this chapter, the specific features and inherent issues of memory architecture in image processing are summarized. To optimize the energy performance, the increased active or leakage energy in multi-port SRAM are discussed. Also, exponentially increased memory bandwidth and capacity caused by the conventional distributed neural network training and those impact in the computational cost must be explained.

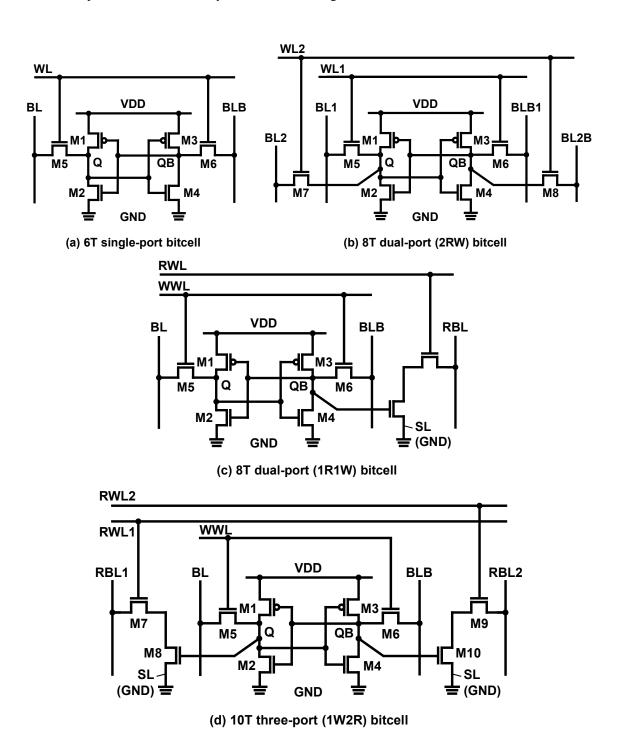

Firstly, we describe the conventional SRAMs as image memory. Here, the features of 6T, 8T, and 10T SRAM bitcells and its design issues are explained. Secondly, we focus to the advanced features of dual-port SRAM and its inherent issues. The unnecessary current and leakage current on the read-port are primary issues in the dual-port SRAMs. RBL swing in the dual-port SRAM also increases active energy. In the deep learning processors, the issues of increased memory bandwidth and capacity must be addressed for future deep learning tasks. The enormous bus communication and drastically increased internal memory capacity degrade scalability of parallelism in deep learning. This chapter notes the primary issues and important challenges to be tackled for future energy-efficient image processing.

## 2.1 Features and issues in the SRAM architecture

### 2.1.1 Fundamental features of multi-port SRAM

Figure 2.1 (a)-(b) illustrates variation of commonly composed single-ported and multi-ported 6T, 8T, and 10T SRAM bitcells. Fig. 2.1(a) shows the 6-transistors (6T) SRAM bitcell. The 6T SRAM bitcell consists of two pMOS pull-up (load) transistors (M1, M3), two nMOS pull-down (driver) transistors (M2, M4), and two nMOS pass-gate (access) transistors (M5, M6). This type of SRAM bitcell is most generally used in the high performance SoCs, because of symmetrical structure. It can achieve

high density integration and quick generation by SRAM compilers. Most of conventional embedded SRAMs are based on the 6T single-port SRAM. The cross coupled inverter circuit holds a bit data as a storage node. The pair of the BLs enables either single write or read (1WR) operation during certain access time. This BL pair is precharged to VDD every cycle before operation and standby mode. The WL is activated for upcoming write or read operation. The BL pair supports quick differential sensing which is effective for high-speed and energy-efficient operation (=small signal sensing). In the 6T SRAM, wordlines (WLs) and bitline-pairs (BLs and BLBs) are vertically and horizontally assigned in the SRAM array.

While the SRAM architectural idea, such as SRAM matrix duplication, can be used to support more than 1WRs in single operation, larger number of transistors are required to realize multi-port functionality, results of certain layout area overhead. Generally composed examples such multi-ported function, include the 8T 2WR dual-port SRAM cell shown in Fig. 2.1(b). It has two pairs of nMOS pass-gate transistors to support independent read and write operations. However, since BL pairs are commonly used for read and write cycle, well known half select disturb problem is remaining. The 8T 1W1R dual-port SRAM consists of 6T bitcell and a dedicated read-port to enable simultaneous write and read access, as depicted in Fig. 2.1(c). The dedicated read port is comprised of two nMOS transistors (M7, M8), this type of SRAM bitcell is commonly used for disturb-free read operation. This nMOS decoupled read port is called as single-ended read port. In this structure, since the SL of read port is generally connected to the GND, the RBL voltage has to fully charged and discharged in the read operation (=large signal sensing). Therefore, read energy on RBL charge/discharge in the single-ended read port is repeatedly consumed. Those features of 8T 1W1R dual-port SRAM with the single-ended read-port significantly increases active energy in the read operation. The extended version of 1W1R dual-port SRAM with dedicated read port realized with the 10-transistor (10T) bitcell is proposed as 10T 1W2R three-port SRAM. It has two single-ended read ports to realize one write and two read (1W2R) operations simultaneously. Thus, the multi-port SRAM can provide SRAM operation in parallel in the same bank, which is preferable for highly paralleled application such as matrix-matrix operations included in image processing. However, its bitcell structure leads larger area and higher energy consumption in the SRAM array.

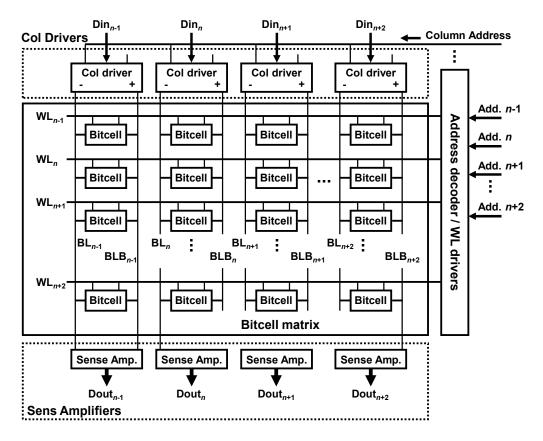

Figure 2.2 shows the block diagram of SRAM bitcell matrix and peripheral control circuitry. The target cell in the matrix can be accessed by selecting the WL and BL pair, which aligned to horizontal and vertical directions. The row/column enable signals are generated by the X and Y address decoders, which respectively select a WL and a BL pair in the matrix. The sense amplifiers are enabled in the read cycle, which read the voltage difference between the BL and the BLB. Finally, the SRAM outputs the read out data (Dout) signals. In the write cycle, the BL pairs are precharged to VDD voltage before the data inputs. After that, BL and BLB is biased to opposite voltage level, such as (BL: VDD, BLB: GND) or (BL: GND, BLB: VDD) by the write drivers according to the input data. The selected WL is enabled by the WL drivers. The WL pulse activates pass-gate transistors in the bitcell, which is a trigger for the write operation to the target SRAM cell.

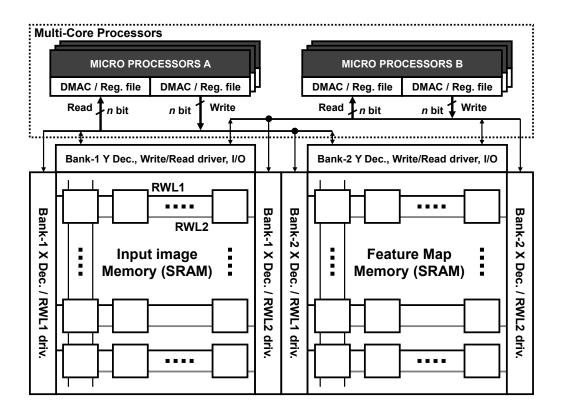

The multi-thread architecture is commonly used for the image processing applications to realize real-time processing, which can be adopted simply with two or more independent processing units. The execution of numerous matrix-matrix operations in parallel is effective way to accelerate the high-quality image or video processing. Figure 2.3 describes the block diagram of memory system in multi-core and multi-thread processor. In this example, the SRAM array is divided into two banks; the SRAM Bank-1 for the input image data and Bank-2 for the feature maps. To execute the filter operation in processing cores, the input data and feature map data are required simultaneously. Thus, the many processing cores access the SRAM simultaneously for multi-thread processing. In such case we explained here, demands for multi-port SRAM have been increased to realize high-speed and low-power image processor. The multi-port SRAM is reportedly suitable for plural core accesses. It significantly improves energy and total performance. To date, a multiport SRAM that supports simultaneous write and read operations is proposed for use as the image processor [5–6]. In those image processor, the number of read operations is drastically increased than write operations. To reduce the energy consumption and optimize whole throughputs, the energy reduction and read circuit improvement techniques are anticipated for such a multi-core image processor.

Fig. 2.1 Variation of commonly composed single-ported and multi-ported 6T, 8T, and 10T SRAM bitcells.

Fig. 2.2 Block diagram of SRAM array.

Fig. 2.3 Block diagram of memory system in the multi-core processor.

### 2.1.2 The issues in the multi-port SRAM

As described previously, the multi-port SRAM is commonly used for multi-core image processors. In this part, we focus the 1W1R dual-port SRAM, which enables simultaneous write and read operation without half select problems. A thing in multi-port SRAM to be considered is its increased area cost. The multi-port SRAM generally require larger area than the conventional 6T SRAM bitcell. Actually, as I shown in Fig. 2.1(d), the 10T three-port SRAM structure is also used as the 10T dual-port SRAM, when the RWL1 and the RWL2 is unified as an RWL. Then, the RBLs can be used as RBL pair. However, its bitcell size is increased significantly. In the high resolution image processing, the larger SRAM capacity is preferable. Thus, the SRAM bitcell area has large impact for entire area cost in SoCs. Therefore, in these dual-port SRAM, the dedicated read-port is mainly adopted as a single-ended structure. The single-ended read port with asymmetric bit-cell can be achieved lower area cost than the symmetrical one, thanks of the lower number of composed transistors.

In the single-ended read port structure with two or more nMOS transistors, the source line of read port is conventionally connected to the ground (GND) voltage. Therefore, the RBL must be fully amplified to read out the stored data when the storage node QB holds "1". It is noteworthy that the single-ended read port has a strong data dependency on its energy consumption. Those feature of conventional single-ended read port, which possibly increases power consumption on the RBLs than the differential sensing scheme. This fact is remaining as an important issue in the dual-port SRAM.

The RBL timing problem is another factor. Because the RBL has to be fully discharged in the read operation, longer access time is necessary for the single-ended structure than the differential one. When considering the operation in sub-threshold region, since the *Vth* variation become worse, and setup/hold margin design should be more severe. Therefore, its operation frequency is lowered than the differential sensing scheme, because the single ended structure needs longer access time. Nevertheless, these differential sensing devices and symmetrical SRAM bitcells entail a greater area cost. To address these issues explained here, various important earlier works have proposed for the dual-port SRAM architectures. (I will explain the details in the chapter 4.)

As described in an earlier report, an 8T 1W1R dual-port SRAM is typically used for

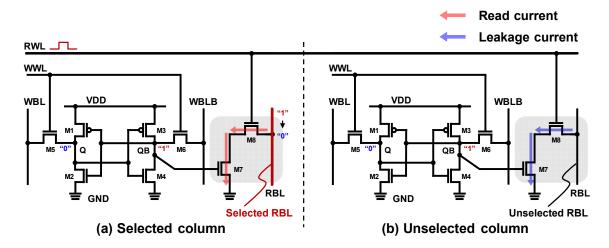

leveraging disturb-free access because of the dedicated read port [29]. The 8T dual-port SRAMs with lower active/standby powers have become more important than ever. The 8T 1W/1R dual-port SRAM structure can eliminate the well-known read disturb problem by preventing charge sharing with internal storage nodes when a read WL is activated. A read port of the 8T dual-port SRAM employs a SL as a footer line, which is shared in the same row address to perform low-energy operations. Figure 2.4 shows the circuit schematic of the SL structure, and the current flow model of unnecessary read current at the unselected column in conventional 8T SRAM cells with single ended read ports. In the read operation, the RBLs are precharged to "1" and the RWL selects a target row address. At the selected column, the RBL voltage is discharged to "0", therefore, the sense amplifier (SA) can amplify the RBL voltage, in the case of Fig. 2.4(a). On the other hand, in the half selected column where RWL is shared with selected column, the RBL current is consumed unnecessarily although the column is not selected for the read out. This structure increases energy consumption on the RBLs, and degrades active energy efficiency. While the circuit techniques, the divided WL structure, can be adopted to the RWLs to reduce energy consumption, it requires additional peripheral circuitry and significantly degrades area performance. As our earlier work [30] proposes the selective sourceline control (SSLC) structure with 8T 1W1R dual-port SRAM, which is developed to reduce leakage current through unselected RBLs. However, some read bitlines are, still discharged slightly in unselected columns because the floating SLs of the conventional scheme [30] degrades energy efficiency.

In this dissertation, our proposed works address the multi-port functionality, area efficiency, variation effects in sub-threshold region, and energy efficiency from the point of circuit design to improve these issues in the 8T dual-port SRAM. The details are discussed in the Chapter 4.

Fig. 2.4 Circuit schematic of sourceline (SL) structure, and current flow model of unnecessary read current at the unselected column in conventional 8T SRAM cells with single-ended read ports.

# 2.2 Fundamental Features and Issues of Deep Neural Network

### 2.2.1 Fundamental features of deep neural network

The neural network imitates cerebral nerve system in the animal or human brain. A hierarchical neural network has plural units in each layer and the units are connected between adjacent layers. The units of each layer are called "perceptron" and weight parameters  $\{w_{1,1}, w_{1,2}, \ldots, w_{(m,n-1)}, w_{(m,n)}\}$  are assigned to the connection (synapse) of the perceptron. The calculation of neural network is performed by the multiplication of input data and synapse. When each data  $\{x_1, x_2, \ldots, x_m\}$  is transferred to the input layer, the  $u_j$  is calculated by the multiplication with the weight parameters and the addition of the bias parameter  $b_j$ . Then, the  $u_j$  is transferred to the next layer, by the Equation (1).

$$u_{j} = \sum_{i=1}^{m} w_{i,j} x_{i} + b_{j} \quad (j = 1, 2, ..., n)$$

(1)

The  $u_j$  must be multiplied by the activation function  $f(u_j)$  to compute an output of target layer. The output of activation function is expressed as Eq. (2). For the activation function, a nonlinear function is generally used in neural network such as monotonically increase nonlinear functions.

$$z_j = f(u_j) \ (j = 1, 2, ..., n)$$

(2)

While the activation functions include step function, softsign, sigmoid functions, the normalized linear function as rectified linear units (ReLU) represented by equation (3), is typically used these days. In the ReLU function, when the partial derivative is defined as in Eq. (4), both the forward propagation and the back propagation should have much less computational cost than the other functions listed above.

$$f(u) = \begin{cases} u & (u > 0) \\ 0 & (u \le 0) \end{cases} \tag{3}$$

$$\frac{\partial f}{\partial u} = \begin{cases} 1 & (u > 0) \\ 0 & (u \le 0) \end{cases} \tag{4}$$

The forward propagation is calculated by the above procedure, and the output of each unit in the final layer is defined as  $y_j$ . Once the output of the final layer of the neural network is obtained, an error function (loss function)  $E_n(w)$  is calculated. The error function  $E_n(w)$  is an indicator to measure the accuracy of the output data generated by the present weight parameter. The regression problems commonly use a square error function. The number of neurons in the output layer must be matched with the number of categories of training data. Here, we assume the number of neurons in the output layer: y and the training data (categories): d is k, then, the output of loss function  $E_n(w)$  is expressed as Eq. (5).

In the network training, to optimize the weight parameters which assigned at each synapses, an optimization function  $E_n$  (w) is commonly used. This optimization procedure is repeatedly executed. It is known that a stochastic gradient descent algorism (SGD) is effective method to find the optimum update value of weight coefficients and to decrease the error function's value. In the SGD algorism, the gradient of the error function with respective weight coefficient is calculated.

$$E_n(\mathbf{w}) = \frac{1}{2} \sum_{k=1}^{K} (y_k - d_k)^2$$

(5)

$$\nabla E(\mathbf{w}) = \frac{\partial E(\mathbf{w})}{\partial \mathbf{w}} \tag{6}$$

Hereinafter, we define the parameter meanings; l: total layer number, i: the layer number and j = i+1, W: weights, dW: deltas, and  $\varepsilon$ : learning rate. Then, the weight coefficient from the layer i to the layer j is expressed as Eq. 7.

$$w_{i,j}^l = w_{i,j}^l - \epsilon \Delta w_{i,j}^l \tag{7}$$

Here, the learning rate (LR):  $\varepsilon$  is an important parameter which control the update amount of weight coefficient. The LR is one of the hyper parameter, which value is determined by the users. In partial derivative calculation Eq. (7), the computational cost

increases sharply from the output layer to the input layer. In order to perform this calculation efficiently, the weight update amount is calculated by the back propagating gradient from the output layer to the input layer. The details of the transformed error propagation calculation are expressed below equations. At the first step, the gradient is defined as Eq. (8). Then, the deltas in the output layer is shown as Eq. (9).

$$\delta_j^{(l)} \equiv \frac{\partial E_n}{\partial u_j^{(l)}} \tag{8}$$

$$\delta_j^{(L)} = \left( y_j - d_j \right) * f' \left( u_j^{(L)} \right) \tag{9}$$

The gradients of the intermediate layer are calculated by below equation, Eq. (10). After that, the update amount of the weight coefficients at each layer can be obtained as shown in Eq. (11).

$$\delta_{j}^{(l)} = \sum_{k} \delta_{k}^{(l+1)} w_{kj}^{(l+1)} f'\left(u_{j}^{(l)}\right)$$

(10)

$$\Delta w_{i,j}^l = \frac{\partial E}{\partial w_{i,j}^l} = \delta_j^{(l)} z_i^{(l-1)} \tag{11}$$

This results means that the deltas of the (l+1)-th layer is transferred to the upstream layer, then the delta in the layer l is obtained from the weights of the (l+1)-th layer and the input of the layer l at the forward propagation. Therefore, the update amount of each layer's weight coefficients can be calculated. Thanks to the characteristics of the propagation rule; the deltas are obtained sequentially from the output layer to the input layer to calculate update amount of the weight coefficient; the backpropagation procedure can be parallelized easily.

In the convolutional neural network (CNN), it consists of plural network layers, which uses not a fully connected layer as described so far. In the convolutional layer, calculation is performed by a filter operation like an image processing instead of the simple product-sum operation in the fully connected layer. Here, we consider the H×W size image data. The input of the convolutional layer defined as  $x_{i,j}$ . The N×N filter as weight coefficient is defined as  $w_{s,t}$ , and the parameter b is bias. Then, the output of the

$$u_{p,q} = \sum_{s=0}^{N-1} \sum_{t=0}^{N-1} w_{s,t} x_{(p+s),(q+t)} + b$$

(12)

convolutional layer  $u_{p, q}$  is expressed as Eq. (12).

The output of the convolutional layer is usually input to the pooling layer. In the pooling layer, a compression of the pixel data to decrease the vertical and horizontal pixel sizes is executed. The convolutional neural network (CNN) is composed of many convolutional layers. Figure 2.5 shows a concept of CNN network. The network contains convolutional layers, normalization layers, activation layers, pooling layers, fully connected layers, and so on. Actually, CNNs have been scaled up with numerous synapses and neurons in deeper layers.

The concept of convolutional neural network (CNN). Fig. 2.5

#### 2.2.1 The issue of memory architecture in the deep neural network

As CNNs have generality with a deeper and larger-scale network, their error rates of cognition continue to improve. Accordingly, computational times become much longer, particularly those for training purpose. Furthermore, the recognition accuracy is improving steadily according to the network size [31], as shown in Fig. 2.6.

Recently, to accelerate the CNN computations, the mini-batch processing is popularly used. Normally, the network training requires the numerous training samples. In the ImageNet dataset that is provided from ILSVRC 2012, it contains 1.28 million images for network training purpose. Therefore, when we consider the network training with a large dataset, enormous computational cost and training time is required because of the increased number of parameter updates for each sample. In this situation, the mini-batch training has become popular as an effective way to execute the network training. The mini-batch training updates the weight parameters with multiple samples in the single iteration. Because the variation of gradients is compensated by the multiple samples, the training convergence will be better. However, in cases of memory capacity, the input data memory or activations of each convolutional layers are lineally increase as the increased number of sample images which must be hold. In the larger batch size, it no longer fits in the internal memory on a single worker.

For further acceleration, the data parallelism is known as one of the promising way to speed up the deep learning. The data parallelism divides the dimensions of the data. The divided data is distributed to the parallel workers. The worker trains same network but with a different data samples. The mini-batch training is categorized as data parallelism, which can be applied to the multi-worker training. In those data parallelism, to increase the parallelization degree, many workers duplicate same network model and hold it in the internal memory. The unification process of deltas collects and take average the deltas that is generated by the back propagation, it must be transferred from each worker to the parameter server. The weight unification process updates weight parameter by using the unified delta. The many parallel workers need large amount of transfer bandwidth, this is why the communication delay will be longer and longer. Figure 2.7 shows the relationship between the acceleration factor and the number of workers. The data parallelism with multiple workers are effective to accelerate the deep learning tasks. However, the total memory capacity in the internal memory is drastically increased. Furthermore, the communication delay on the data bus is significantly increased at the highly distributed parallelization. The acceleration factor saturates even if over 50 GPUs are paralleled [32]. In the conventional parallelization model, the memory bandwidth and memory capacity limits a scalability of deep learning acceleration.

In this work, we targeted the development of low-cost and high-scalable deep learning processor with lower internal-memory capacity and lower memory bandwidth on the data transfer bus. Our algorism and architecture expands a scalability with lower memory cost and higher energy-efficiency than the conventional data parallelism.

Fig. 2.6 The correlation between the accuracy and the deepnesss of network model [31].

- 1. Accelerate training time is the key for future DNN application.

- 2. External data communication between GPUs and servers are required for weight unification.

- 3. Speed up factor is saturated with large-number of GPUs, that is the scalability limitation in distributed deep learning.

The relationship between the acceleration factor and the .number of workers. The acceleration factor saturates over 50 GPUs situation [32].

#### 2.3 **Summary**

This section summarizes the issues of multi-port SRAMs as an image memory, and the memory system in the distributed image recognition processors.

For the multi-port SRAM, these issues are explained

- Increased active energy on the access ports, and its area cost

- Energy efficiency degradation by the unnecessary current flow and leakage current.

For the deep learning processor, below issues and challenges are explained.

- How to accelerate the computational time to train network models.

- Increased amount of internal memory capacity

- Increased memory bandwidth with parallelized workers

These issues have to be considered on whole memory architecture level to achieve low-power and low-energy image recognition processor. The cooperative design with device technology in SRAM, memory efficient algorithm design, and hardware development have to be integrated. In this dissertation, the novel techniques are presented in Chapters 3 to 5 to address the issues.

# Chapter 3 Low-energy Multi-Port SRAM Cell Design

All the static random access memory (SRAM) in this chapter were implemented in the 28-nm FD-SOI process technology supported by ST-Microelectronics Co. Ltd. This chapter describes low-power 2-read/1-write 8T three port SRAM design. We studied following contents:

- 1) The design of novel 2-read/1-write three-port 8T SRAM bitcell in 28-nm FD-SOI with small area overhead.

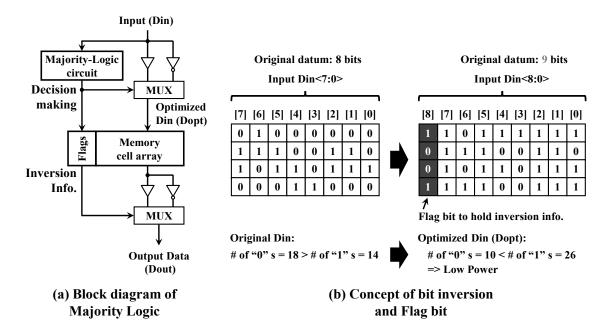

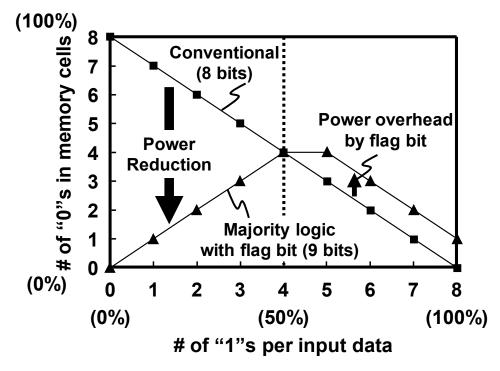

- 2) The combination with the proposed SRAM and majority logic circuit for further energy reduction.

Finally, the energy efficiency and the performance improvement in the actual H.264 motion estimation image processor is explained when the proposed SRAM techniques are adopted.

# 3.1.1 The multi-port SRAM design in image processor

When considering the mechanism of image or video sequence, image processor must perform the matrix-matrix computation for filtering operation. Normally, the high-speed SRAM as an internal memory is indispensable for effective data loading, because the external data access conspicuously lead longer access delay in memory. Actually, high-performance SRAM is used as a frame buffer and a reconstructed image memory in a real-time video or image processing in the H.264 image processor, shown in Fig. 3.1. In particular, parallel computation by multi-thread processing of matrix-matrix operations as seen in the image processing is beneficial for its real-time operation.

From this reason, input data for image processing are stored temporarily in SRAM. In an image processor, many processing cores access the SRAM for multi-thread processing, as presented in Fig. 1. Demands for multi-port SRAM have been increased to accommodate high-speed and low-power image processing. The multi-port SRAM is suitable for parallel operation. It improves the total chip performance. To date, a multiport SRAM that supports simultaneous write and read operations is proposed for use as the image processor [5], [6]. The three-port SRAM is reportedly suitable for use as an image processor [7], [33]. When comparing features of two images, simultaneous

Fig. 3.1 Memory system in image processing. This work targeted the development of low-power and low-cost image memory.

read operations are requested to SRAM cells. Furthermore, realizing real-time processing requires a write operation for the next comparison at the same time as the read operation. Therefore, two read operations and one write operation must be performed simultaneously, which require multiport SRAMs that have two-read/one-write access ports for the image processor.

In the multi-port SRAM, the larger area overhead is critical due to the increasing number of transistors in the SRAM cell. In the image processor, the larger number of SRAM capacity is required to process high-resolution image and video sequence. The resolution improvement brings higher energy consumption in SRAM.

Conventionally, the bit-cell layout in the three-port SRAM needs a larger bit-cell area than that of an 8T dual-port SRAM cell due to the larger number of transistors which must be accommodated in the SRAM cell [33]. In particular, an image processor requires larger multiport memory capacity, which gives a serious impact on its cost. In this paper, we exhibit an 8T three-port SRAM smaller than the conventional three-port bitcell. Its area is as small as the conventional 8T dual-port SRAM.

We propose two types of circuit techniques in the multi-port SRAM to improve area efficiency and to achieve low-voltage and low-power operation. We designed a 28-nm FD-SOI 8T three-port SRAM for a low-power image processor and compared it to a 28-nm FD-SOI 6T SRAM in the conventional form.

## 3.1.2 1-Write/2-Read 8T three-port SRAM cell design

Multi-port SRAM with plural read ports improves functionality to handle the simultaneous accesses. Since the write and read ports are controlled independently, write and multiple read operations can be performed simultaneously on different cells in the same bank. In this way, the multi-port SRAM is suitable for parallel operation such as image processing. The conventional 1-write/2-read three-port SRAM needs larger bitcell area than the 8T dual-port SRAM due to the increasing number of transistors in the SRAM cell [33]. In particular, an image processor requires a larger multi-port SRAM capacity, which gives a serious impact on its cost.

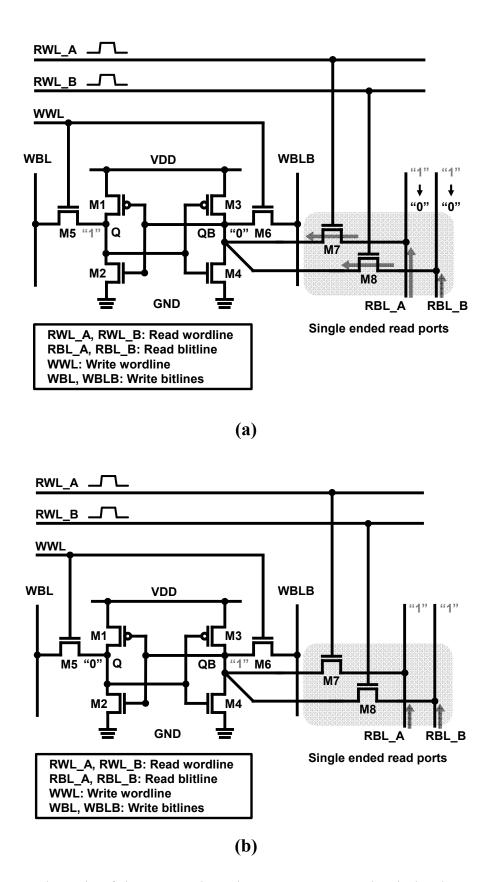

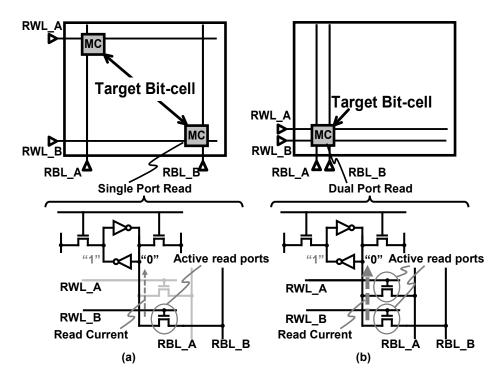

A circuit schematic of the proposed 8T three-port SRAM is presented in Fig. 3.2. It has a pair of write bitlines and two single-ended read bitlines (one-write/two-read bitcell structure). The proposed SRAM has two pull-up pMOSs (load-pMOS), two pull-down nMOSs (drive-nMOS), and four transfer nMOSs (access-nMOS). In this circuit, M7 and M8 transistors are the two single-ended read ports. Source nodes of M7 and M8 transistors are connected to node QB. The drain nodes are connected to read bitlines (RBL\_A, RBL\_B). The gate nodes of M7 and M8 are connected to the read wordlines (RWL\_A, RWL\_B). Both read ports (read ports A and B) are consolidated on one side

Fig. 3.2 Schematic of proposed 8T three-port SRAM with single ended read ports.

| _ |             |             |               |                     |                    |  |  |  |

|---|-------------|-------------|---------------|---------------------|--------------------|--|--|--|

|   | Tr. size    | Pull-up Tr. | Pull-down Tr. | Write pass gate Tr. | Read pass gate Tr. |  |  |  |

|   |             | (M1, M3)    | (M2, M4)      | (M5, M6)            | (M7, M8)           |  |  |  |

|   | Width [nm]  | 80          | 142           | 80                  | 80                 |  |  |  |

|   | Length [nm] | 30          | 30            | 30                  | 30                 |  |  |  |

Transistor W/L sizes in the proposed SRAM cell. The proposed 8T SRAM cell is designed on the logic rule bases.

Logic Rule based design

and has asymmetric cell structure. This asymmetrical 8T SRAM cell achieves higher density than the conventional three-port SRAM cell.

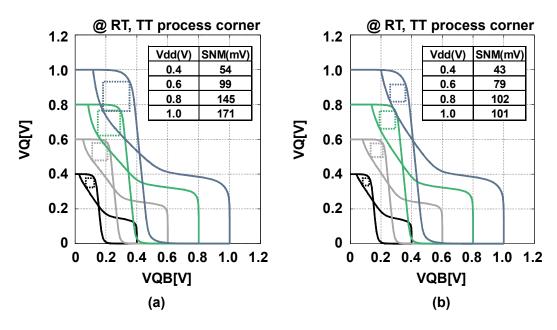

The  $\beta$  ratio in the SRAM cell indicates a strength of the pull-down transistor against to the pass-gate transistor. The  $\beta$  ratio must be remained sufficiently to ensure the proper read operation. In our design, the W/L size of the pull-down transistor in the bitcell is chosen to remain a sufficient SNM (static noise margin) even when the both read ports are activated. All transistor W/L sizes in the bitcell are shown in Table 3.1. In this case, the  $\beta$  ratio in the proposed three port SRAM cell is 1.77 (= 142 nm/80 nm).

Figure 3.3(a) presents front-end-of-line (FEOL) of the proposed 8T three-port SRAM. Read ports comprising M7 and M8 transistors are arranged separately from a 6T SRAM cell, which share a common contact located at the middle as the QB node. This layout achieves a smaller cell area than in symmetrical layout in which the additional read ports are arranged at both ends [29]. However, a vertical distance between upper and lower gates (gate pitch) is increased because the M-3 metal for additional read wordlines (RWLs) are inserted.

Figure 3.3(b) shows the back-end-of-line (BEOL) of the proposed SRAM. The SRAM cell size is determined by the number of horizontal and vertical wires. In our proposed SRAM, two read ports consisting of M7 and M8 transistors are configured as two single-ended read ports having three bitlines and three wordlines shown as Metal 2 and Metal 3. The cell area is 0.56 µm<sup>2</sup> on a logic rule base, which is as small as the dual-port 8T bitcell [34], although the number of read ports is increased. The small-area bitcell contributes to reduce parasitic capacitance on the WLs and BLs in SRAM matrix. This feature of proposed SRAM is beneficial for low-energy operation by saving the leakage and the operating energy.

Bitcell layout of proposed three-port SRAM: (a) FEOL and (b) BEOL. Fig. 3.3

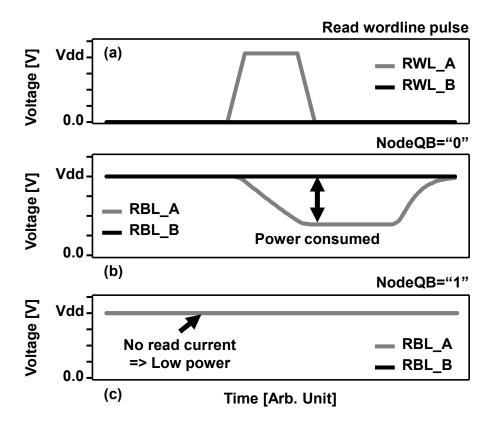

The operating waveforms in the read operation are depicted in Fig. 3.4(a)-(c). Initially, the wordline pulse is inputted to the selected row, as shown in Fig. 3.4(a). If the QB node holds the "0" data, the read current flows through the pass-gate transistor M7 or M8 to the QB node, as shown in the case of Fig. 3.4(b). On the other hand, no read current flows through the read bitlines (RBL\_A and RBL\_B) when the internal node, node QB, is "1", as shown in Fig. 3.4(c). Figures 3.5(a) and (b) show the behavior of the current flow at the read operation in the proposed SRAM. Fig. 3.5(a) shows a read current flow when the QB node stores "0" data and RWLs are activated. In this situation, read current is pulled from RBL\_A, RBL\_B to the QB node. The RBLs are precharged right before the read cycle. The charge/discharge energy on the RBLs are consumed every read cycle. On the other hand, because "1" data is stored in the QB node, the source node of M7 and M8 is equally driven to the VDD. Therefore, the read current flow from the RBLs to the QB node does not consumed, as depicted in Fig. 3.5(b). From this reason, maximizing the number of "1"s at node QB is important to reduce dynamic energy in the read operation.

Fig. 3.4 Waveforms of proposed 8T three-port SRAM in read operation; (a) Wordline pulse, (b) when the Node QB holds "0" data, (c) when Node QB holds "1" data.

Schematic of the proposed 8T three-port SRAM and write/read current flow model, (a) when the Node QB holds "0" data, (b) when Node QB holds "1" data.

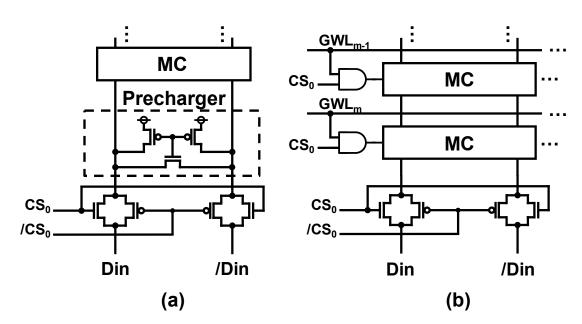

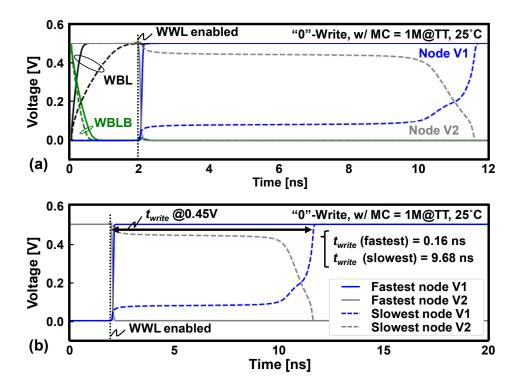

#### 3.1.3 Precharge-less write circuit

Figures 3.6(a)-(b) presents comparison of write circuit between the conventional 6T SRAM and the proposed 8T three-port SRAM. Figure 3.6(a) depicts the conventional write circuit with write bitline precharge scheme which as shown with pMOS transistors to charge a bitline pair. The conventional write circuit must have a precharge scheme to maintain stability of read operations because both read and write operations use the common bitline pair. Figure 3.6(b) depicts the precharge-less write circuit. Successive writes of the same data consume less energy because the proposed 8T SRAM does not need a precharge scheme on the write bitlines because of the dedicated read ports for the read operation. However, it incurs the well-known half-select problem along the write wordline. In our design, the divided wordline structure is therefore adopted to avoid the half-select problem [35]. However, the divided word line structure entails the large area overhead in SRAM macro, therefore only write wordlines have a divided architecture.

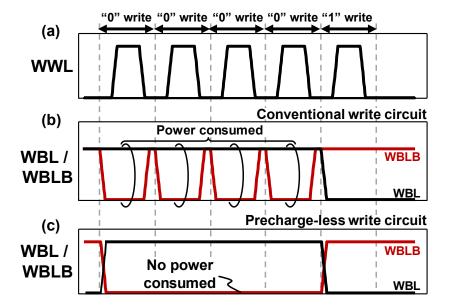

Figures 3.7(a)-(c) portrays simplified waveforms during four '0' write cycles and an "1" write cycle. Figure 3.7(a) shows the waveform of the write wordline (WWL) pulse commonly used in the conventional SRAM and the proposed SRAM. Figure 3.7(b) shows waveforms of the write bitlines (WBL and WBLB) in the conventional write scheme. The either bitline is dropped to the ground voltage in write cycle. Therefore,

Fig. 3.6 Schematics of write circuits between conventional SRAM and proposed SRAM architecture: (a) conventional circuit and (b) precharge-less circuit.

Fig. 3.7 Waveforms in the write operation: (a) Write wordline (WWL) pulse, (b) Write bitline (WBL and WBLB) signals in a conventional write circuit and (c) a precharge-less write circuit.

the charge/discharge power on the WBL is consumed in every cycle by the precharge scheme. Figure 3.7(c) portrays waveforms of the write bitlines in the proposed SRAM. By virtue of the precharge-less write scheme, which reduces the write energy, the charge/discharge power on WBLs is consumed only when a write datum is changed.

#### 3.1.4 Static noise margin (SNM) in 8T 1W2R three-port SRAM