PDF issue: 2025-01-15

# Study on threshold voltage and carrier mobility in organic thin-film transistors

#### Kimura, Yoshinari

```

(Degree)

博士 (工学)

(Date of Degree)

2020-09-25

(Date of Publication)

2021-09-01

(Resource Type)

doctoral thesis

(Report Number)

甲第7877号

(URL)

https://hdl.handle.net/20.500.14094/D1007877

```

※ 当コンテンツは神戸大学の学術成果です。無断複製・不正使用等を禁じます。著作権法で認められている範囲内で、適切にご利用ください。

#### **Doctoral Dissertation**

#### 博士論文

Study on threshold voltage and carrier mobility in organic thin-film transistors 有機薄膜トランジスタの閾値電圧および キャリア移動度に関する研究

July, 2020

令和2年7月

Graduate School of Engineering, Kobe University 神戸大学大学院工学研究科

Yoshinari Kimura

木村 由斉

# **Contents**

# Chapter 1

1.1. Background

# **General Introduction**

| 1.2. Brief history of organic TFTs                              | 2        |

|-----------------------------------------------------------------|----------|

| 1.3. Structure of organic TFTs                                  | 3        |

| 1.4. Semiconductor properties of organic molecules              | 4        |

| 1.5. Charge transport for organic TFTs                          | 6        |

| 1.6. Materials for organic TFTs                                 | 7        |

| 1.6.1 Organic semiconductor materials                           | 7        |

| 1.6.2 Gate dielectric materials                                 | 10       |

| 1.7. Purpose of this thesis                                     | 11       |

| 1.8. Outline of this thesis                                     | 11       |

| 1.9. References                                                 | 13       |

| Chapter 2  Analytical Methods of Organic Transistor Charact     | eristics |

| 2.1. Introduction                                               | 16       |

| 2.2. Characteristics of organic TFTs                            | 16       |

| 2.2.1 Current-voltage characteristics                           | 16       |

| 2.2.2 Field-effect mobility and threshold voltage               | 18       |

| 2.2.3 Contact resistance and sheet resistance                   | 19       |

| 2.2.4 Relationship between threshold voltage and charge density | 20       |

| 2.3. References                                                 | 22       |

1

# Operational Stability in Pentacene Thin-Film Transistors with

## **Threshold Voltages Tuned by Oxygen Plasma Treatment**

| 3.1. Introduction           | 23 |

|-----------------------------|----|

| 3.2. Experimental methods   | 24 |

| 3.3. Results and discussion | 26 |

| 3.4. Summary                | 36 |

| 3.5. References             | 37 |

# Chapter 4

# Energy Distribution of Interface States Generated by Oxygen

#### **Plasma Treatment**

| 4.1. Introduction                        | 41 |

|------------------------------------------|----|

| 4.2. Analytical methods                  | 42 |

| 4.2.1 Characteristics of MOS capacitors  | 42 |

| 4.2.2 Interface states of MOS capacitors | 44 |

| 4.3. Experimental methods                | 45 |

| 4.4. Results and discussion              | 48 |

| 4.4.1 Transistor characteristics         | 48 |

| 4.4.2 MOS capacitor characteristics      | 50 |

| 4.4.3 Interface state density            | 52 |

| 4.5. Summary                             | 56 |

| 4.6. References                          | 57 |

# **Evaluation of Carrier Mobility by Using Organic Metal-Oxide- Semiconductor Capacitors Based on a Distributed Constant Circuit**

| 5.1. Introduction                                                             | 61 |

|-------------------------------------------------------------------------------|----|

| 5.2. Analytical methods                                                       | 63 |

| 5.2.1 Characteristics of MOS capacitors with a large uncovered pentacene area | 63 |

| 5.2.2 Mobility and threshold voltage in uncovered pentacene area              | 65 |

| 5.3. Experimental methods                                                     | 66 |

| 5.4. Results and discussion                                                   | 68 |

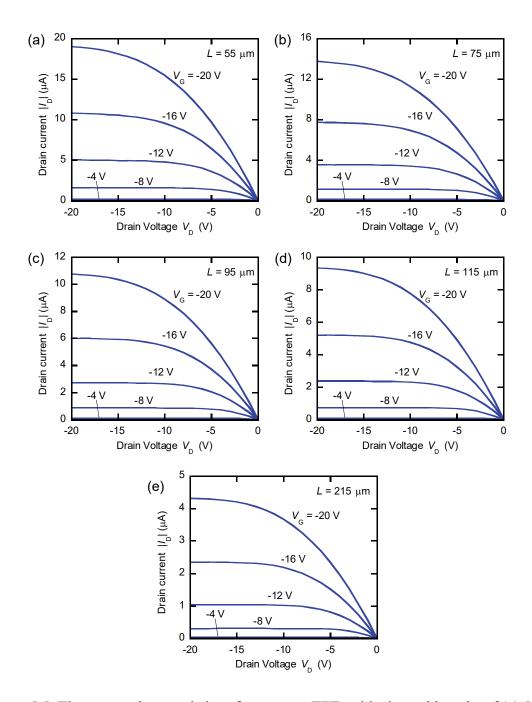

| 5.4.1 Transistor characteristics                                              | 68 |

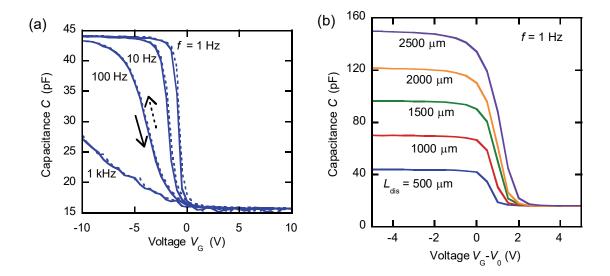

| 5.4.2 MOS capacitor characteristics                                           | 74 |

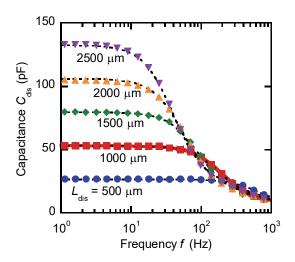

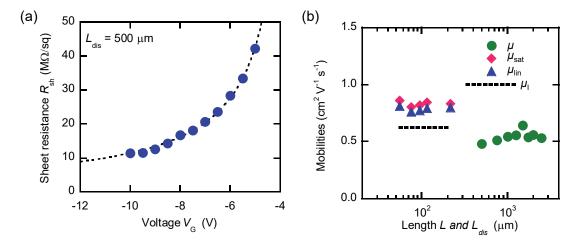

| 5.4.3 Sheet resistance and mobility                                           | 77 |

| 5.5. Summary                                                                  | 79 |

| 5.6. References                                                               | 80 |

|                                                                               |    |

| Chapter 6                                                                     |    |

| Conclusions                                                                   | 83 |

| List of Publications                                                          | 85 |

| Acknowledgements                                                              | 90 |

### **General Introduction**

#### 1.1 Background

Today, humans are living surrounded by a lot of electronic equipment such as personal computers and mobile phones. Electronics technology is an essential technology for human life. In particular, a transistor is the core device.

A metal-oxide-semiconductor field-effect transistor (MOSFET) using Si and SiO<sub>2</sub> was first reported by Kahng and Atalla in 1960 [1]. MOSFET is a device play a role of an electrical switch. Today, MOSFET is used for more than one million in one electronic device, and is an indispensable device in human life. Also, development of thin-film transistors (TFTs) using a hydrogenated amorphous silicon (a-Si:H) is important. TFT is different from FET in that the substrate and gate electrode are independent and the conducting channel is formed in the accumulation region. a-Si:H TFTs play an important role in applications where FETs are not suitable. The successes of transistors to date are achieved by improvements in these Si semiconductor.

Organic TFTs using organic materials have been attracted attention in recent years. Organic materials have advantages such as flexible, light-weight, and solubility. Thus, organic layer can be formed on an inexpensive substrate such as plastic and paper. In addition, organic layer can be deposited not only by vacuum process but also by printing process using organic solution. Therefore, by using organic materials, flexible, light-weight, large-area, low-cost, and thin devices can be fabricated. Organic TFTs are expected to realize a new type of electronic device

that is difficult for Si-based transistors.

#### 1.2 Brief history of organic TFTs

Organic TFTs have been studied since the 1980's. Tsumura et al. reported the first organic TFT in 1986 [2]. The first organic TFT with polythiophene as an organic semiconductor showed a characteristic of a p-channel transistor and a field-effect mobility of about  $10^{-5}$  cm<sup>2</sup>/(V s). Guillaud et al. reported n-channel organic TFTs using bisphthalocyanine derivatives in 1990 [3]. Since these reports, many researchers have investigated organic TFTs.

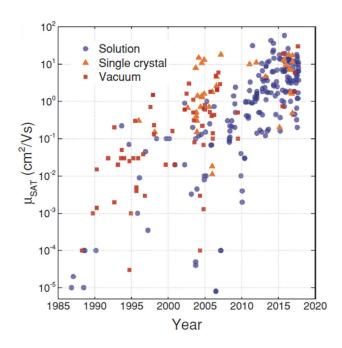

Many of the improvements in performance of organic TFTs have been focused on the improvements in a field-effect mobility. Figure 1 shows the evolution of field-effect mobility in organic TFTs depending on fabrication processes [4]. The mobility is  $10^{-5}$  cm<sup>2</sup>/(V s) in the first report of 1986, and over  $10 \text{ cm}^2$ /(V s) in 2015. The mobility has improved  $10^6$  times in the last 30 years. The mobility of organic TFTs exceeds that of a-Si (about  $0.5 \text{ cm}^2$ /(V s)) transistors. Therefore, the organic TFTs are considered to have practical performance in terms of the mobility.

Improvements in the organic semiconductor materials, device structures, and fabrication techniques contribute to the improvements of the mobility. In particular, the variety of fabrication techniques available for organic TFTs is a major advantage over Si MOSFETs. Organic TFTs are fabricated by thermal evaporation or solution process. The optimized process has contributed to not only improve device performance shown in Fig. 1.1 but also reduce deposition cost and time.

Figure 1.1: Evolution of field-effect mobility in organic TFTs depending on fabrication processes. [4]

#### 1.3 Structure of organic TFTs

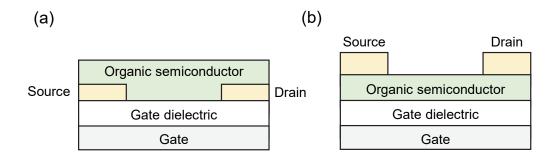

Figure 1.2 shows commonly used structures of organic TFTs. An organic TFT is made of four parts. They are a gate electrode, a gate dielectric, an organic semiconductor layer, and source/drain electrodes. The source and drain electrodes are in direct contact with the organic semiconductor layer. The gate electrode is isolated from the organic semiconductor by the gate dielectric. The current through the organic semiconductor is controlled by applying voltage to gate and drain electrode and connecting source electrode to ground. The structure of an organic TFT is called bottom-contact (shown in Fig. 1.2(a)) or top-contact (shown in Fig. 1.2(b)) structure depending on the positions of source/drain electrodes and organic semiconductor. Each of these structures has advantages. In the bottom-contact structure, source/drain electrodes are deposited on the gate dielectric. Because the micro-patterning techniques such as photolithography can be used, organic TFTs with micro channel-length can be fabricated easily. Reducing channel-length is important for TFTs to operate at high frequency. However, it is

difficult to fabricate the top-contact structure by using these micro-patterning techniques. This is because the organic semiconductor molecules are easily destroyed by high temperature, light irradiation, or an organic solvent. On the other hand, contact resistance at interface between the organic semiconductor and source/drain electrodes has been reported to be lower in top-contact structure than bottom-contact structure [5-7]. Therefore, the top-contact organic TFT tends to have good characteristics than bottom-contact one. Some groups have reported various other structures such as top-gate [8], floating-gate [9], and double-gate structures [10].

Figure 1.2: Illustration of bottom-gate (a) bottom-contact and (b) top-contact structures of organic TFTs.

#### 1.4 Semiconductor properties of organic molecules

Carrier density and carrier mobility of organic semiconductor using for an organic TFT are much smaller than those of Si semiconductor. Thus, organic semiconductors are materials with characteristics closer to dielectrics than semiconductors [11]. This indicates that organic semiconductors are intrinsic semiconductors.

The operating mode of the semiconductor is classified into *n*-type or *p*-type depending on whether the conduction carrier is electron or hole. The operating mode of a Si semiconductor is determined by controlling the carrier density by doping donors or acceptors. On the other

hands, for organic semiconductors, because the carrier density in the organic semiconductor is low, it is difficult to control the carrier density by doping. Also, the organic molecules may be destroyed by doping. Thus, the carriers inside an organic semiconductor are dominated by the carriers injected from an electrode that is in direct contact with the organic semiconductor. In other words, the carriers accumulate in the organic semiconductor only when they are injected from the electrode. The injection barrier between an electrode and organic semiconductor affects carrier transport.

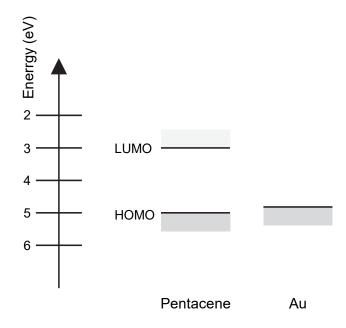

The operating mode of the organic TFTs depends on the positions of the work function of electrode and the frontier orbitals (highest occupied molecular orbitals, HOMO, and lowest unoccupied molecular orbitals, LUMO) of organic semiconductor. As an example, the case of pentacene and gold is explained. They are materials typically used for organic TFTs. Figure 1.3 shows the energy schemes of pentacene and gold. Data for pentacene and gold was taken from Ref. 12 and 13. The work function of gold and the HOMO level of pentacene are almost in the same position. This indicates that holes are easily injected because the injection barrier height for holes is low. On the other hand, the difference between the work function of gold and the LUMO level of pentacene is about 2 eV. This difference is much higher than the thermal energy at room temperature (0.026 eV). It is difficult to inject electrons in pentacene from Au. Therefore, when using pentacene as a semiconductor and gold as a contact metal, pentacene shows the conduction characteristic of a *p*-type semiconductor [12].

Figure 1.3: Energy schemes of pentacene and gold.

#### 1.5 Charge transport for organic TFTs

The interfaces between the organic semiconductor and the source/drain electrodes and between the organic semiconductor and the gate dielectric have an important role for the performance of organic TFTs.

Carriers injected from the drain electrode flow through the organic semiconductor to the source electrode. Carrier transport is limited by contact resistance at the interface between the organic semiconductor and the source/drain electrodes. The contact resistance strongly affects the characteristics of the organic TFT. In particularly, a large contact resistance is a problem when the channel length between the source and drain electrodes is short. The injection barrier between the organic semiconductor and the source/drain electrodes in Fig. 1.3 is the main cause of the contact resistance. Thus, the characteristic is improved by matching the work function of the contact metal with the HOMO or LUMO level of the organic semiconductor. Modification

of the metal surface with a monolayer is one method to change the work function of the metal [13-15]. For example, by modifying the Au surface with pentafluorobenzenthiol (PFBT), work function of Au shifts from 4.8 eV to 5.5 eV [13]. Also, TFT characteristics are improved [16].

A channel region for carrier transport is formed within the organic semiconductor near the interface between the organic semiconductor and the gate dielectric [17]. In addition, the quality of organic semiconductor crystals depends on the flatness and energy of the gate dielectric surface. The organic semiconductor crystals change when treated with UV ozone or a self-assembled monolayer (SAM) [18-20]. Therefore, the interface properties also affect the characteristics of the organic TFT [19,20].

#### 1.6 Materials for organic TFTs

#### 1.6.1 Organic semiconductor materials

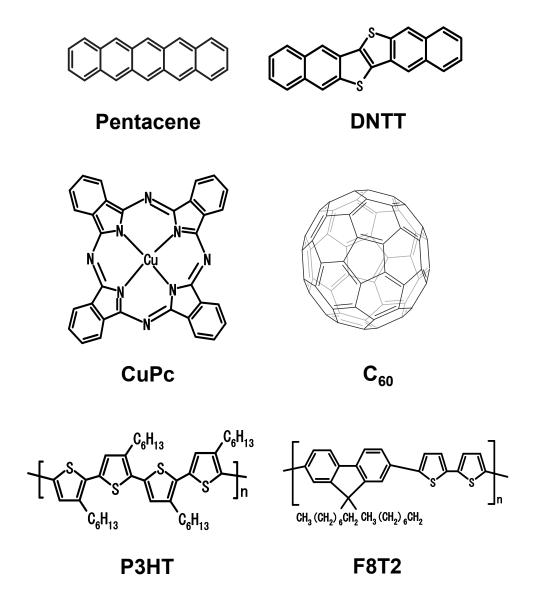

Many organic semiconductor materials used in organic TFTs have been reported because of the ease of designing new organic molecules. Figure 1.4 shows typical organic semiconductor materials used in organic TFTs. Organic semiconductor materials are classified as small molecules or polymers.

Small molecular materials have the advantage of showing better transistor characteristics than polymer materials. Pentacene is the material most used for *p*-channel organic TFTs [12]. As other materials, dinaphtho[2,3-*b*:2',3'-*f*]thieno[3,2-*b*]thiophene (DNTT) [21,22] and copper phthalocyanine (CuPc) [23] are famous materials as *p*-channel organic TFTs. On the other hand, fullerene C<sub>60</sub> [24] and C<sub>60</sub> derivatives [25] are generally used for *n*-channel organic TFTs. Because many small molecular materials are difficult to dissolve in organic solvent, they were generally deposited by thermal vapor deposition. On the other hand, solubility in organic solvents can be obtained by introducing side chains into the small molecular material such as alkyl DNTT [26,27] and 6,13-bis(triisopropyl-silyethynyl) pentacene [28,29]. In small

molecular materials with side chains, organic semiconductor layer can be formed by using solution processes such as inkjet and spin coat.

Polymer materials have the advantage of being easy to form an organic semiconductor film by using solution process. Solution process is available for small molecular materials. However, the stability of the characteristics of organic TFTs with small molecule semiconductor formed by solution process is low. In polymer materials, a uniform semiconductor film can be easily form by using solution process and TFTs operate stably. For polymer materials, poly(3-hexythiophene) (P3HT) [30,31] and poly(9,9-dioctylfluorene-co-bithiophene) (F8T2) [31,32] is widely used for organic TFTs.

Figure 1.4: Typical organic semiconductor materials for organic TFTs.

#### 1.6.2 Gate dielectric materials

Gate dielectrics are as important as organic semiconductors. The gate dielectrics are required to have various properties such as high withstand voltage, high gate capacitance, flatness of surface, low surface energy, and mechanical flexibility. The dielectric materials are selected according to the application. As the gate dielectric materials for organic TFTs, inorganic materials or organic polymer materials are used.

SiO<sub>2</sub> is the most used materials for gate dielectric of organic TFTs. SiO<sub>2</sub> is easy to form a film and has excellent electrical and mechanical stability. However, the characteristics of organic TFTs are limited by the trapping sites and surface energy on the SiO<sub>2</sub> surface. In particular, surface energy strongly affects the quality of the organic semiconductor crystals formed on the gate dielectric. Their influence has been partially improved by covering the SiO<sub>2</sub> surface with a SAM. For SAM materials, silane molecules, such as hexamethyldisilazane [33] and alkyl trichlorosilane [34,35], and phosphonic acid molecules [36] are used.

Organic polymer dielectrics are used to take advantage of its mechanical flexibility. Because the surface of organic polymer dielectrics is covered with organic molecules, they lead to good crystallinity of an organic semiconductor. For organic polymer dielectric materials, parylene [37,38] and CYTOP [39] are widely used. The flexible organic TFTs with organic polymer dielectric show performance close to that of the organic TFTs with SiO2 dielectric.

In many reports, organic TFTs operate at a high voltage of several tens of volts. Driving organic TFTs at low voltage is important to reduce power consumption of devices. In order to operate organic TFTs at low voltage, the gate dielectrics need to have a high gate capacitance. The gate capacitance  $C_{OX}$  is given as  $\varepsilon/d$ , where d is the thickness and  $\varepsilon$  is the dielectric constant of the gate dielectric. High dielectric constant or thin dielectric layer is needed to obtain a high gate capacitance. Thinning the gate dielectric layer may cause dielectric breakdown. Thus, use of dielectric materials with high dielectric constant (high-k) is effective for organic TFTs to

operate at low voltage. For high-k dielectric materials, Al2O3, TiO2 or HfO2 is used [40]. By using these materials, low voltage operation of organic TFTs is achieved.

#### 1.7 Purpose of this thesis

Organic TFTs have various issues for practical applications. Control of the threshold voltage and accurate evaluation of the mobility for their applications are important issues. For a Si semiconductor, the threshold voltage can be controlled by changing the doping concentration. However, it is difficult to dope donor or acceptor in an organic semiconductor. Hence, control method of the threshold voltage in organic TFTs is not established. On the other hand, the mobility of organic TFTs is generally evaluated by using the current–voltage characteristics. However, this method evaluates the mobility including the contact resistance. Methods for controlling the threshold voltage and evaluating the intrinsic mobility of organic TFTs are required. In this thesis, influence of oxygen plasma treatment on the threshold voltage in organic TFTs is investigated. Furthermore, the charge at the surface of gate dielectric induced by oxygen plasma is evaluated quantitatively. In addition, the intrinsic mobility without including the contact resistance is evaluated by using a MOS capacitor structure.

#### 1.8 Outline of this thesis

This thesis is structured in six chapters. Chapters 1 and 2 are the introductory part in this thesis. In chapter 1 "General Introduction", brief introduction of organic TFTs were mentioned as research background. The TFTs, organic semiconductors and materials were briefly described. Then, purpose and outline of this thesis were described.

In chapter 2 "Analytical Methods of Organic Transistor Characteristics", the typical analytical model for organic TFTs is summarized. Calculation methods for parameters, such as

field-effect mobility, threshold voltage, and contact resistance, in organic TFTs are presented.

Chapters 3 through 5 are the main part in this thesis. The main part is divided into two parts. One is about influence of oxygen plasma treatment on the threshold voltage in organic TFTs and the other is about evaluation of the intrinsic mobility of organic TFTs. The former is described in chapters 3 and 4, and the latter is described in chapter 5.

In chapter 3 "Operational Stability in Pentacene Thin-Film Transistors with Threshold Voltages Tuned by Oxygen Plasma Treatment", organic TFTs having a gate dielectric treated with oxygen plasma have been investigated for control of the threshold voltage. The relationship between threshold voltage and oxygen plasma treatment is discussed. In addition, the influence of gate bias stress on threshold voltage is described.

In chapter 4 "Energy Distribution of Interface States Generated by Oxygen Plasma Treatment", the characteristics of organic MOS capacitors have been investigated for evaluation of energy distribution of interface states. The relationship between oxygen plasma treatment and the MOS capacitor characteristics is described. The energy distribution of the interface states induced by oxygen plasma treatment is discussed.

In chapter 5 "Evaluation of Organic Metal-Oxide-Semiconductor Capacitors Based on a Distributed Constant Circuit", the capacitance characteristics of organic MOS capacitors with a uncovered semiconductor area have been investigated for evaluation of the intrinsic mobility. The mobility of a MOS capacitor with an uncovered area is described assuming that the uncovered area is represented by a distributed constant circuit. In addition, the mobilities were compared with those calculated from the current–voltage characteristics of TFTs.

In chapter 6 "Conclusions", the results in this thesis are summarized.

#### 1.9 References

- [1] D. Kahng, IEEE Trans. Electron Devices **23**, 655 (1976).

- [2] A. Tsumura, H. Koezuka, and T. Ando, Appl. Phys. Lett. 49, 1210 (1986).

- [3] G. Guillaud, M. Al Sadoun, and M. Maitrot, Chem. Phys. Lett. 167, 503 (1990).

- [4] A. F. Paterson, S. Singh, K. J. Fallon, T. Hodsden, Y. Han, B. C. Schroeder, H. Bronstein, M. Heeney, I. McCulloch, and T. D. Anthopoulos, Adv. Mater. 30, 1801079 (2018).

- [5] K. Shibata, H. Wada, K. Ishikawa, H. Takezoe, and T. Mori, Appl. Phys. Lett. 90, 193509 (2007).

- [6] P. V. Necliudov, M. S. Shur, D. J. Gundlach, and T. N. Jackson, Solid-State Electron. 47, 259 (2003).

- [7] K. P. Puntambekar, P. V. Pesavento, and C. D. Frisbie, Appl. Phys. Lett. 83, 5539 (2003).

- [8] D. K. Hwang, C. F.-Hernandez, J. Kim, W. J. Potscavage Jr., S.-J. Kim, and B. Kippelen, Adv. Mater. 23, 1293 (2011).

- [9] T. Yokota, T. Sekitani, T. Tokuhara, N. Take, U. Zschieschang, H. Klauk, K. Takimiya, T.-C. Huang, M. Takamiya, T. Sakurai, and T. Someya, IEEE Trans. Electron. Devices 59, 3434 (2012)

- [10] K. Hizu, T. Sekitani, T. Someya, and J. Otsuki, Appl. Phys. Lett. **90**, 093504 (2007).

- [11]R. Tamura, E. Lim, T. Manaka, and M. Iwamoto, J. Appl. Phys. 100, 114515 (2006).

- [12] M. Kitamura, and Y. Arakawa, J. Phys.: Condens. Matter 20, 184011 (2008).

- [13] Y. Kuzumoto, and M. Kitamura, Appl. Phys. Express 7, 035701 (2014).

- [14] I. H. Campbell, S. Rubin, T. A. Zawodzinski, J. D. Kress, R. L. Martin, D. L. Smith, N. N. Barashkov, and J. P. Ferraris, Phys. Rev. B 54, 14321 (1996).

- [15] S. D. Evans, and A. Ulman, Chem. Phys. Lett. 170, 462 (1990).

- [16] J. W. Borchert, B. Peng, F. Letzkus, J. N. Burghartz, P. K. L. Chan, K. Zojer, S. Ludwigs, and H. Klauk, Nat. Commun. 10, 1119 (2019).

- [17] C. D. Dimitrakopoulos, and P. R. L. Malenfant, Adv. Mater. 14, 99 (2002).

- [18] C.-L. Fan, Y.-Z. Lin, and C.-H. Huang, Semicond. Sci. Technol. 26, 045006 (2011).

- [19] S. Kang, S. Jung, J. Park, H.-J. Lee, and M. Yi, Microelectron. Eng. 84, 1503 (2007).

- [20] D. Kumaki, M. Yahiro, Y. Inoue, and S. Tokito, Appl. Phys. Lett. 90, 133511 (2007).

- [21] R. Yamamoto, K. Noda, Y. Wada, and T. Toyabe, Electron. Commun. Jpn. 100, 61 (2017).

- [22] U. Kraft, K. Takimiya, M. J. Kang, R. Rödel, F. Letzkus, J. N. Burghartz, E. Weber, and H. Klauk, Org. Electron. **35**, 33 (2016).

- [23] R. Zeis, T. Siegrist, and Ch. Kloc, Appl. Phys. Lett. **86**, 022103 (2005).

- [24] M. Kitamura, S. Aomori, J. H. Na, and Y. Arakawa, Appl. Phys. Lett. 93, 033313 (2008).

- [25] P. H. Wöbkenberg, D. D. C. Bradley, D. Kronholm, J. C. Hummelen, D. M. de Leeuw, M. Cölle, and T. D. Anthopoulos, Synth. Met. **158**, 468 (2008).

- [26] M. Ito, T. Uemura, J. Soeda, and J. Takeya, Org. Electron. 14, 2144 (2013).

- [27] K. Nakayama, Y. Hirose, J. Soeda, M. Yoshizumi, T. Uemura, M. Uno, W. Li, M. J. Kang, M. Yamagishi, Y. Okada, E. Miyazaki, Y. Nakazawa, A. Nakao, K. Takimiya, and J. Takeya, Adv. Mater. 23, 1626 (2011).

- [28] S. K. Park, T. N. Jackson, J. E. Anthony, and D. A. Mourey, Appl. Phys. Lett. **91**, 063514 (2007).

- [29] J.-P. Hong, A.-Y. Park, S. Lee, J. Kang, N. Shin, and D. Y. Yoon, Appl. Phys. Lett. **92**, 143311 (2008).

- [30]B. H. Hamadani, and D. Natelson, Appl. Phys. Lett. **84**, 443 (2004).

- [31] T. Nagase, T. Hirose, T. Kobayashi, R. Ueda, A. Otomo, and H. Naito, Appl. Sci. 8, 1274 (2018).

- [32] L. Bürgi, T. J. Richards, R. H. Friend, and H. Sirringhaus, J. Appl. Phys. **94**, 6129 (2003).

- [33] J. B. Koo, S. H. Kim, J. H. Lee, C. H. Ku, S. C. Lim, and T. Zyung, Synth. Met. **156**, 99 (2006).

- [34] F. Gholamrezaie, A.-M. Andringa, W. S. C. Roelofs, A. Neuhold, M. Kemerink, P. W. M. Blom, and D. M. de Leeuw, Small 8, 241 (2012).

- [35] Y. Chung, E. Verploegen, A. Vailionis, Y. Sun, Y. Nishi, B. Murmann, and Z. Bao, Nano Lett. 11, 1161 (2011).

- [36] M. Salinas, C. M. Jäger, A. Y. Amin, P. O. Dral, T. M.-Friedrichsen, A. Hirsch, T. Clark, and M. Halik, J. Am. Chem. Soc. 134, 12648 (2012).

- [37] K. Fukuda, T. Suzuki, D. Kumaki, and S. Tokito, Phys. Status Solidi A 209, 2073 (2012).

- [38] V. Podzorov, V. M. Pudalov, and M. E. Gershenson, Appl. Phys. Lett. 82, 1739 (2003).

- [39] W. L. Kalb, T. Mathis, S. Haas, A. F. Stassen, and B. Batlogg, Appl. Phys. Lett. **90**, 092104 (2007).

- [40] R. P. Ortiz, A. Facchetti, and T. J. Marks, Chem. Rev. 110, 205 (2010).

# Analytical Methods of Organic Transistor Characteristics

#### 2.1 Introduction

In this chapter, equations for the evaluation and analysis of organic thin-film transistors (TFTs) characteristics are summarized. Firstly, the current–voltage characteristics and their equations generally used for evaluating organic TFTs are presented. Then, the evaluation method of the field-effect mobility, the threshold voltage, and the contact resistance is presented. Finally, relationship between threshold voltage and charge density is described.

#### 2.2 Characteristics of organic TFTs

#### 2.2.1 Current-voltage characteristics

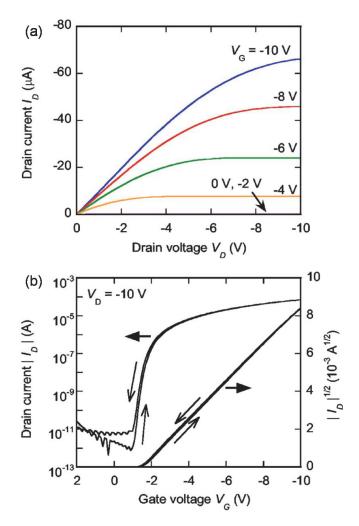

The characteristics of organic TFTs are almost similar to those of Si transistors. Figures 2.1(a) and 2.1(b) show reported examples of drain current ( $I_D$ ) versus drain voltage ( $V_D$ ) and drain current versus gate voltage ( $V_G$ ) characteristics of a pentacene TFT, respectively [1]. The drain current decreases with the gate voltage and saturates below a certain drain voltage. Their characteristics show typical p-channel MOSFET (field-effect transistor) characteristics. Therefore, standard analysis model for Si MOSFETs can be applied to organic TFTs. The following three approximations are assumed as correct [2]:

1. The channel length is much larger than the thickness of the gate dielectric and the carrier accumulation layer.

- 2. The field-effect mobility does not depend on electric field.

- 3. Only carriers accumulate when the gate voltage is applied.

The organic TFTs operate in saturation, linear, and cutoff regime. The drain current  $I_D$  flowing from the drain to the source for a p-cannel organic TFT is given by

$$I_{\rm D} = -\frac{1}{2} \mu_{\rm FE} C_{\rm OX} \frac{W}{L} (V_{\rm G} - V_{\rm TH})^2$$

for  $|V_{\rm D}| \ge |V_{\rm G} - V_{\rm TH}|$ , (2.1a)

$$I_{\rm D} = -\mu_{\rm FE} C_{\rm OX} \frac{W}{L} \left[ (V_{\rm G} - V_{\rm TH}) V_{\rm D} - \frac{1}{2} V_{\rm D}^2 \right] \quad \text{for } |V_{\rm D}| \le |V_{\rm G} - V_{\rm TH}|, \tag{2.1b}$$

$$I_{\rm D} = 0 \qquad \qquad \text{for } V_{\rm G} > V_{\rm TH}, \tag{2.1c}$$

where W and L are the channel width and length,  $\mu_{FE}$  is the field-effect mobility,  $C_{OX}$  is the gate capacitance per unit area,  $V_{TH}$  is the threshold voltage,  $V_{G}$  and  $V_{D}$  are the source-gate and the source-drain voltages.

When  $|V_D| \ll |V_G - V_{TH}|$ , the drain current is approximated as

$$I_{\rm D} \cong -\mu_{\rm FE} C_{\rm OX} \frac{W}{L} (V_{\rm G} - V_{\rm TH}) V_{\rm D}. \tag{2.2}$$

Figure 2.1: (a) Drain current versus drain voltage characteristics at various gate voltages and (b) drain current versus gate voltage characteristics of a pentacene TFT. [1]

#### 2.2.2 Field-effect mobility and threshold voltage

In TFTs, the field-effect mobility and the threshold voltage are very important parameters. The field-effect mobility indicates the ease of carrier transport in semiconductor when an electric field is applied. The threshold voltage indicates the gate voltage at which drain current begins to flow. The field-effect mobility ( $\mu_{\text{sat}}$ ) and the threshold voltage values experimentally estimated in the saturation regime are calculated by fitting a line to a measured  $|I_D|^{1/2}$ - $V_G$  curve with Eq. (2.1a). The experimental field-effect mobility ( $\mu_{\text{lin}}$ ) in the liner regime is calculated

from a measured  $|I_D|$ - $V_G$  curve using Eq. (2.1b).

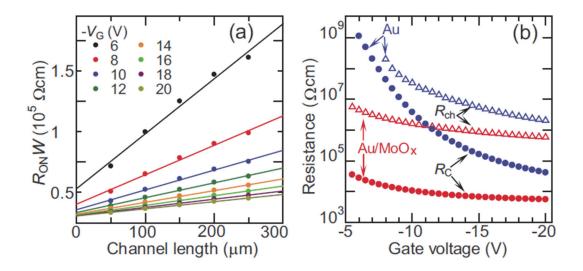

#### 2.2.3 Contact resistance and sheet resistance

The contact resistance  $R_{\rm C}$  between the organic semiconductor and the source/drain electrodes is estimated by using various methods such as transfer line method [3-5], gated four probe method [6], and Kelvin probe force microscopy [7]. The transfer line method is the most used method for experimentally evaluating the contact resistance. The contact resistance is estimated by the following procedure. First, the  $I_{\rm D}$ - $V_{\rm D}$  characteristics of organic TFTs with several channel lengths are measured. Next, the on-resistance  $R_{\rm ON}$ , which is defined as  $|\partial V_{\rm D}| / \partial I_{\rm D}|$  in the linear regime, is plotted for the channel length. Figure 2.2(a) shows an example of measured the on-resistance as a function of the channel length and the gate voltage [8]. The on-resistance increases linearly with the channel length. The on-resistance is assumed to be

$$R_{\rm ON} = R_{\rm ch} + R_{\rm C} = \frac{L}{\mu_{\rm I} W C_{\rm OX} |V_{\rm G} - V_{\rm TH}|} + R_{\rm c},$$

(2.3)

Where  $R_{ch}$  is the channel resistance,  $\mu_{I}$  is the mobility in the intrinsic transistor without contact resistance. The  $R_{C}$  and  $R_{ch}$  are estimated from the intercept and slope of figure 2.2(a). Figure 2.2(b) shows an example of the calculated  $R_{C}$  and  $R_{ch}$  [8]. The sheet resistance  $R_{TFT}$  is given by

$$R_{\rm TFT} = R_{\rm ch} \frac{W}{L} = \frac{1}{\mu_{\rm I} C_{\rm OX} |V_{\rm G} - V_{\rm TH}|}.$$

(2.4)

Figure 2.2: (a) Channel width normalized on-resistance as a function of channel length and gate voltage  $V_G$ . (b) Channel width normalized contact resistance and channel resistance as a function of  $V_G$ . [8]

#### 2.2.4 Relationship between threshold voltage and charge density

Many organic TFTs operate in the accumulation mode. Therefore, the threshold voltage of organic TFTs equals the flat band voltage. Thus, the threshold voltage of organic TFTs can be given by

$$V_{\text{TH}} = \frac{\Phi_{\text{M}} - \Phi_{\text{S}}}{e} - \frac{1}{C_{\text{OX}}} Q = \frac{\Phi_{\text{M}} - \Phi_{\text{S}}}{e} - \frac{d}{\varepsilon} Q, \qquad (2.5)$$

where e is the electron elementary charge,  $\Phi_{\rm M}$  and  $\Phi_{\rm S}$  are the work functions of the gate electrode and the organic semiconductor, respectively, d is the thickness and  $\varepsilon$  is the dielectric constant of the gate dielectric, respectively, Q is the charge density [9]. Q is written as

$$Q = Q_{\rm S} + \int_0^d \frac{x}{d} \rho_{\rm OX}(x) dx, \qquad (2.6)$$

where  $Q_S$  is the surface charge density at the interface between the gate dielectric and the semiconductor and  $\rho_{OX}$  is the charge density per unit volume in the gate dielectric. The interfaces of the gate dielectric for the gate metal and the semiconductor are defined as x = 0

and d, respectively.

In this thesis,  $Q_S$  is assumed to be mainly induced by oxygen plasma treatment. The surface charge density  $Q_S$  is expressed as

$$Q_{\rm S} = q_{\rm p} t_{\rm p} \,, \tag{2.7}$$

where  $q_p$  is the surface charge density induced by oxygen plasma treatment and  $t_p$  is the oxygen plasma treatment time. Although  $q_p$  depends on the conditions of plasma treatment,  $q_p$  is a constant under certain conditions of plasma treatment except treatment time. Substituting Eqs. (2.6) and (2.7) into Eq. (2.5), the threshold voltage is written as

$$V_{\rm TH} = \frac{\Phi_{\rm M} - \Phi_{\rm S}}{e} - \frac{d}{\varepsilon} \left( Q_0 + q_{\rm p} t_{\rm p} \right). \tag{2.8}$$

where

$$Q_0 = \int_0^d \frac{x}{d} \,\rho_{\text{OX}}(x) dx, \qquad (2.9)$$

As a result, the threshold voltage changes linearly as a function of d and  $t_p$  under the assumption that  $q_p$  is a constant.

#### 2.4 References

- [1] M. Kitamura, and Y. Arakawa, Appl. Phys. Lett. 89, 223525 (2006).

- [2] D. K. Schroder, Semiconductor Material and Device Characterization, 3rd ed. New York, USA, Wiley.

- [3] M. Kitamura, S. Aomori, J. H. Na, and Y. Arakawa, Appl. Phys. Lett. 93, 03331 (2008).

- [4] S. D. Wang, Y. Yan, and K. Tsukagoshi, Appl. Phys. Lett. 97, 063307 (2010).

- [5] U. Kraft, K. Takimiya, M. J. Kang, R. Rödel, F. Letzkus, J. N. Burghartz, E. Weber, and H. Klauk, Org. Electron. **35**, 33 (2016).

- [6] P. V. Pesavento, R. J. Chesterfield, C. R. Newman, and C. D. Frisbie, J. Appl. Phys. 96, 7312 (2004).

- [7] K. P. Puntambekar, P. V. Pesavento, and C. D. Frisbie, Appl. Phys. Lett. 83, 5539 (2003).

- [8] M. Kano, T. Minari, and K. Tsukagoshi, Appl. Phys. Lett. 94, 143304 (2009).

- [9] M. Kitamura, and Y. Arakawa, J. Phys.: Condens. Matter 20, 184011 (2008).

# Operational Stability in Pentacene Thin-Film Transistors with Threshold Voltages Tuned by Oxygen Plasma Treatment

#### 3.1 Introduction

Organic thin-film transistors (TFTs) have been applied to logic circuits [1-4] and addressing devices for active-matrix displays [5-9]. Threshold voltage control for organic TFTs is essential for realizing a circuit design for such applications of organic TFTs. Also, accurate control of the threshold voltage contributes to stable [10], high-speed [11], and low-power [12] operations of circuits.

Some approaches have been attempted to control the threshold voltage in organic TFTs. In one approach, a change in parasitic resistance between a contact electrode and a channel layer is applied [13,14]. In another approach, a self-assembled monolayer (SAM) is prepared on the surface of the gate dielectric [15-17]. However, these approaches affect other characteristics of the TFTs such as field-effect mobility and subthreshold swing. Threshold voltages are also controlled using a double-gate structure [18,19]. Although this approach enables a continuous change in the threshold voltage, it requires the fabrication of an additional electrode in the double-gate structure.

Oxygen plasma [17] and UV ozone treatments [15,20,21] have been used to obtain a hydrophilic surface for formation of a SAM on a gate dielectric. Since the threshold voltage in organic TFTs depends on fixed charges on the surface of and inside the gate dielectric, oxygen

plasma and UV ozone treatments to the surface of the gate dielectric may possibly affect the threshold voltage. In fact, the effects of oxygen plasma [22-24] and UV ozone [25,26] treatments on threshold voltages have been reported. Thus, oxygen plasma or UV ozone treatment has potentials in the accurate control of the threshold voltage in organic TFTs suitable for practical use [27].

The stability of the characteristics of organic TFTs under operation is also an important issue for their practical applications. Thus, some groups have intensively investigated the change in the threshold voltage in organic TFTs as a function of bias stress time and bias voltage [28-34]. Since the stability of the threshold voltage in organic TFTs is strongly related to condition of the gate dielectric, investigation of the stability in organic TFTs with controlled threshold voltage is demanded.

In this chapter, we report the characteristics of pentacene-based TFTs with a SiO<sub>2</sub> gate dielectric treated with oxygen plasma. In particular, the dependence of the threshold voltage in the TFTs on treatment time is examined. The threshold voltage after gate bias stress is also shown to evaluate the stability of the threshold voltage change induced by plasma treatment.

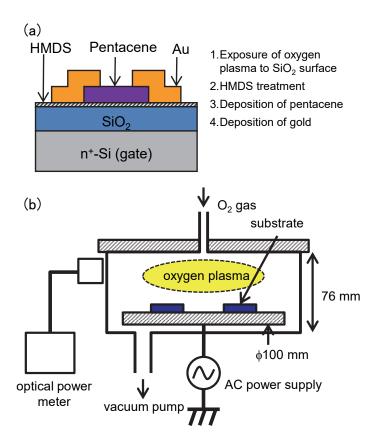

#### 3.2 Experimental methods

A cross section of the pentacene TFT examined in this chapter in shown in Fig. 3.1(a). The pentacene TFT was fabricated on a highly doped n-type Si substrate with thermally grown SiO<sub>2</sub> serving as the gate dielectric. Silicon substrates with various SiO<sub>2</sub> thickness were used to examine the characteristics of pentacene TFTs on the basis of Eq. (2.5). The SiO<sub>2</sub> thickness, *d*, are 35, 90, 300, and 500 nm, which provide unit area capacitances of 92.0, 36.9, 11.3, and 6.61 nF/cm<sup>2</sup>, respectively. The SiO<sub>2</sub> surface was treated using an oxygen plasma equipment (SAKIGAKE-Semiconductor YHS-GNS), an illustration of which is shown in Fig. 3.1(b). The oxygen flow rate was fixed at 100 mL/min. The AC power for plasma generation, *p*<sub>AC</sub>, which

is controllable in the range of less than or equal to 50 W, was adjusted by monitoring the emission intensity of the plasma. The AC power was set at 5.8 W as a standard power in this chapter. Although the power 0f 5.8 W seems to be slightly low, this power is sufficient to affect the characteristics of TFTs. This is because the vacuum chamber and the electrode of the equipment are not large, as shown in Fig. 3.1(b). The treatment time  $t_p$  was set in the range between 5 and 900 s. After the oxygen plasma treatment, the substrate was immediately exposed to hexamethyldisilazane (HMDS) vapor to obtain a hydrophobic surface. A 45-nm-thick pentacene layer was then deposited on the SiO<sub>2</sub> dielectric at room temperature through a shadow mask. The deposition rate was 1.2 nm/min. Finally, a 45-nm-thick Au layer was deposited through another shadow mask to define the drain and source electrodes. The channel width was 1 mm, and the channel length (L) was 80 or 100 µm. Since pentacene TFTs with L = 100 µm were mainly investigated, the channel length of TFTs not specified in this manuscript is 100 µm. The current–voltage characteristics of pentacene TFTs were measured in a dry-nitrogen glovebox at room temperature using a semiconductor parameter analyzer.

Figure 3.1: (a) Cross section of fabricated pentacene-based TFT and the fabrication process. (b) Illustration of oxygen plasma equipment used for surface treatment of SiO<sub>2</sub> gate dielectric.

#### 3.3 Results and discussion

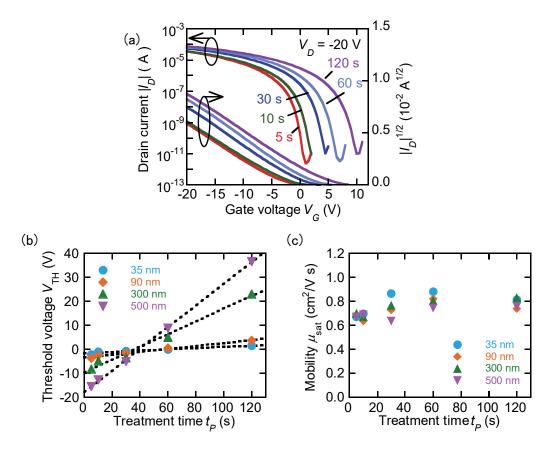

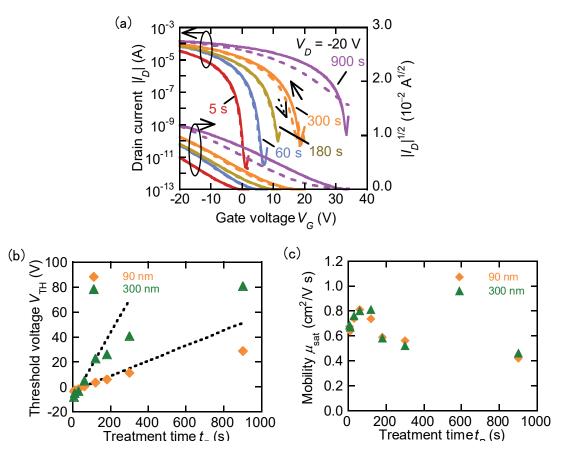

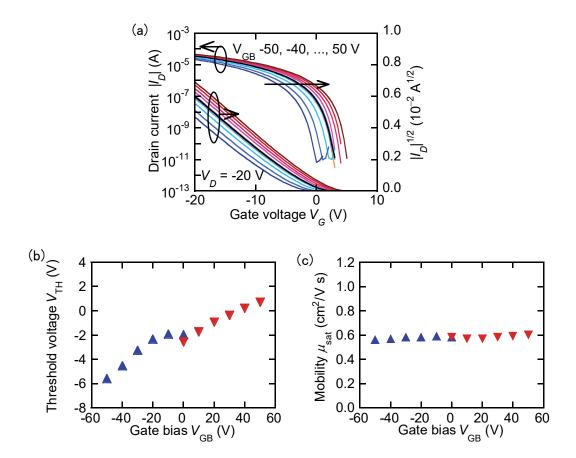

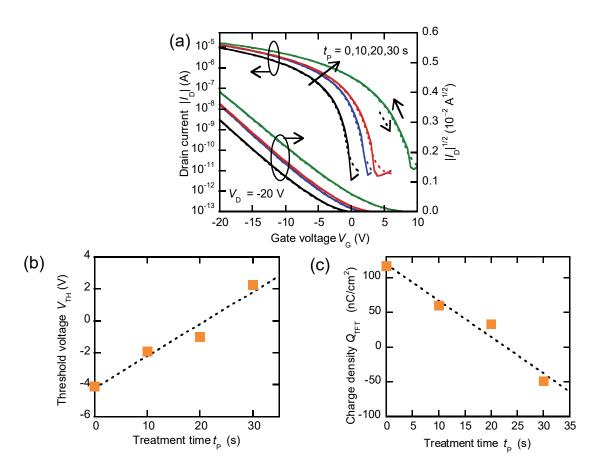

Figure 3.2(a) shows the drain current ( $I_D$ ) versus gate voltage ( $V_G$ ) characteristics at a drain voltage ( $V_D$ ) of -20 V of pentacene TFTs with 90-nm-thick SiO<sub>2</sub> layers treated with oxygen plasma. The plasma treatment times,  $t_P$ , were 5, 10, 30, 60, and 120 s. The transfer curves in Fig. 3.2(a) shift to positive gate voltages with increase in plasma treatment time. The slopes of  $|I_D|^{1/2}-V_G$  curves, the subthreshold swing, and the off current are almost the same for all TFTs. The results indicate that the oxygen plasma treatment with the treatment time affects only the threshold voltages. The threshold voltage,  $V_{TH}$ , and the field-effect mobility in the saturation

regime,  $\mu_{\rm sat}$ , of pentacene TFTs with different SiO<sub>2</sub> thickness are shown as a function of  $t_{\rm p}$  in Figs. 3.2(b) and 3.2(c), respectively. The  $V_{\rm TH}$  and  $\mu_{\rm sat}$  values were estimated by fitting a line to the  $|I_{\rm D}|^{1/2}$ – $V_{\rm G}$  curves in the saturation regime. For the measurement of pentacene TFTs with d=35, 90, 300, and 500 nm in the saturation regime, the drain voltages were set at -10, -20, -60, and -100 V, respectively. The threshold voltage is in the range from -15 to 36 V. The  $V_{\rm TH}$  for each SiO<sub>2</sub> thickness increases linearly with  $t_{\rm P}$ . This is consistent with Eq. (2.8). The slopes of  $V_{\rm TH}$  versus  $t_{\rm P}$  for d=35, 90, 300, and 500 nm are 0.027, 0.061, 0.27, and 0.45 V/s, respectively. The slope increases with SiO<sub>2</sub> thickness. The dependence of the slope on SiO<sub>2</sub> thickness is also consistent with Eq. (2.8). On the other hand, it seems that  $\mu_{\rm sat}$  is independent of treatment time, as seen from Fig. 3.2(c).  $\mu_{\rm sat}$  is in the range of 0.57 to 0.85 cm<sup>2</sup>/(V s) and the average is 0.73 cm<sup>2</sup>/(V s). The results shown in Figs. 3.2(b) and 3.2(c) suggest that the threshold voltage can be controlled without large change in mobility.

Figure 3.2: (a) Transfer characteristics of pentacene TFTs with 90-nm-thick SiO<sub>2</sub> with oxygen plasma treatment times between 5 and 120 s. (b) Threshold voltage and (c) mobilities in the saturation regime of TFTs with 35-, 90-, 300-, and 500-nm thick SiO<sub>2</sub> as a function of treatment time.

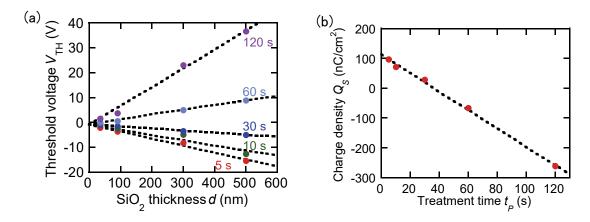

To estimate the surface charge density  $Q_S$ , the threshold voltage is plotted as a function of SiO<sub>2</sub> thickness in Fig. 3.3(a). The slope of the fitting line for treatment time in Fig. 3.3(a) corresponds to the surface charge for treatment time. Figure 3.3(b) shows the surface charge density estimated from Fig. 3.3(a). On the basis of Eqs. (2.6), (2.7), and (2.9), the intrinsic surface charge density  $Q_0$  and the surface charge density induced by plasma treatment,  $q_P$ , are estimated to be 113 nC/cm<sup>2</sup> and -3.1 nC/(cm<sup>2</sup> s), respectively. The  $Q_0$  value of 113 nC/cm<sup>2</sup> corresponds to the charge site density of about  $7 \times 10^{11}$  cm<sup>-2</sup>. Although the reason for the intrinsic surface charge is under investigation, sites not terminated with HMDS and/or dopants

in the highly doped silicon may be related to the positive surface charge. On the other hand, the negative value of  $q_p$  indicates that oxygen plasma treatment generates electron trapping sites on and/or near the SiO<sub>2</sub> surface. In addition, the result of threshold voltage shift suggests that electrons captured at the trapping sites work as negative fixed charges even after the surface is treated with HMDS.

Figure 3.3: (a) Threshold voltages of pentacene TFTs with gate dielectrics plasmatreated for 5, 10, 30, 60, and 120 s as a function of SiO<sub>2</sub> thickness. (b) Surface charge density estimation from the threshold voltage in (a) as a function of treatment time.

The effect of long plasma treatment on the transistor characteristics was examined to investigate the limitation of the threshold voltage changes. Figure 3.4(a) shows the  $|I_D|-V_G$  and  $|I_D|^{1/2}-V_G$  characteristics of TFTs with 90-nm-thick SiO<sub>2</sub> layers treated with oxygen plasma for  $t_p$  between 5 and 900 s. The transfer curves in forward and reverse sweeps are shown with solid and dashed lines, respectively. For the treatment times of 5, 60, and 180 s, the transfer curve in reverse sweep almost traces the curve in forward sweep. On the other hand, the long plasma treatments for  $t_p = 300$  and 900 s lead to hysteresis I the transfer curves. This indicates that long plasma treatments lead to an increase in shallow trap density. Figures 3.4(b) and 3.4(c) respectively show the threshold voltage and mobility in the saturation regime of TFTs with d = 100

90 and 300 nm. The values were estimated from the transfer curves in forward sweep. The dashed line in Fig. 3.4(b) for each d is the same as the fitted line in Fig. 3.2(b). The difference between the dashed line and the plot increases with  $t_p$ . This indicates that the surface charge density induced by plasma treatment does not increase linearly with treatment time. This means that  $q_p$  is not constant with respective to  $t_p$  and decreases with an increase in  $t_p$ . On the other hand, the mobilities for long treatment times between 180 and 900 s are lower than those for  $t_p$  between 5 and 120 s. As a result, plasma treatment for  $t_p$  longer than 120 s leads to decreases in mobility and hysteresis in transfer curves.

Figure 3.4: (a) Transfer characteristics of pentacene TFTs with 90-nm-thick SiO<sub>2</sub> with oxygen plasma treatment times between 5 and 900 s. (b) Threshold voltage and (c) mobilities in the saturation regime of TFTs with 90- and 300-nm-thick SiO<sub>2</sub> as functions of treatment time.

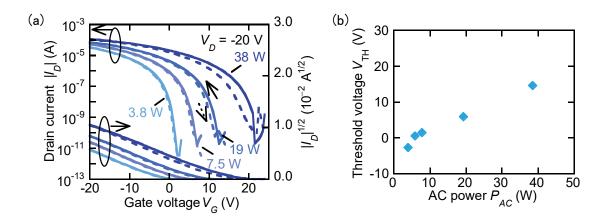

The dependence of AC power on the transfer characteristics was also investigated. Figures 3.5(a) and 3.5(b) show the transfer characteristics and mobility in the saturation regime of pentacene TFTs with 90-nm-thick  $SiO_2$  layers treated with oxygen plasma for 60 s. The AC power  $p_{AC}$  was set in the range between 3.8 and 38 W. The increase in  $p_{AC}$  leads to positive shift in the threshold voltage. However, a high AC power causes hysteresis in the transfer curves as well as long treatment time.

Figure 3.5: (a) Transfer characteristics of pentacene TFTs with 90-nm-thick SiO<sub>2</sub> treated with oxygen plasma at AC power from 3.8 to 38 W. (b) Threshold voltages of TFTs with 90-nm-thick SiO<sub>2</sub> as a function of AC power.

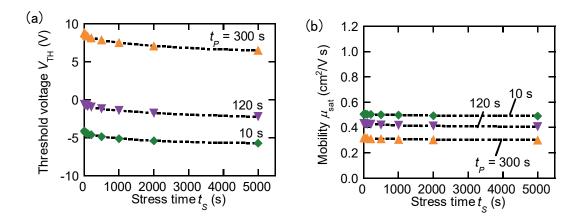

To evaluate the stability of threshold voltage change, the effect of gate bias stress on the transfer characteristics was investigated. The voltage of gate bias,  $V_{\rm GB}$ , was set in the range of -50 to 50 V, and the drain voltage was fixed at 0 V. The stress time  $t_{\rm s}$  was in the range from 0 to 5000 s. Figures 3.6(a) and 3.6(b) show the threshold voltage and mobility in the saturation regime of the TFTs with L=80 µm for different  $t_{\rm p}$  after applying bias at  $V_{\rm GB}=-20$  V as a function of  $t_{\rm s}$ , respectively. The  $V_{\rm TH}$  for each TFT decreases with increase in  $t_{\rm s}$ . The threshold voltage shifts during stress are 1.6 V for  $t_{\rm p}=10$  s, 1.7 V for  $t_{\rm p}=120$  s, and 2.3 V for  $t_{\rm p}=300$  s. The threshold voltage does not depend strongly on  $t_{\rm p}$ . This indicates that a relative threshold

voltage among different  $t_p$  is maintained during gate bias stress. This suggests that the negative bias stress does not affect the negative charge induced by plasma treatment. Although the threshold voltage shift between 1.6 and 2.3 V induced by gate bias stress is slightly larger than that of a pentacene TFT with a polymer gate dielectric [32], the shift is not as large as those other organic TFTs [28,30,35,36], amorphous Si TFTs [37-39] and oxide TFTs [40-42].

Figure 3.6: (a) Threshold voltages and (b) mobilities in the saturation regime of three TFTs with 90-nm-thick SiO<sub>2</sub> plasma treated for 10, 120, and 300 s as a function of bias stress time. The gate bias and drain voltage are -20 and 0 V, respectively.

Figure 3.7(a) shows the transfer characteristics of a TFT with a 90-nm-thick SiO<sub>2</sub> dielectric treated with  $p_{AC} = 3.8$  W and  $t_p = 60$  s measured after applying bias at  $V_{GB} = 0, -10, \ldots, -50$  V, and  $10, \ldots, 50$  V for  $t_s = 60$  s. The measurement for positive bias was conducted about one day after the negative bias examination. The threshold voltage and the mobility in the saturation regime estimated from the transfer characteristics are shown in Fig. 3.7(b) and 3.7(c), respectively. The threshold voltage changes in accordance with the bias stress, although the mobility is almost independent of the bias stress. The negative bias stress induces negative shift in the threshold voltage, which decreases non linearly with decrease in  $V_{GB}$ . Although the bias stress at  $V_{GB}$  less than -20 V induces a threshold voltage shift greater than 1 V, the threshold

voltage shift under a agate bias stress in the range of 0 to -20 V is as small as 0.4 V. The small shift in the threshold voltage contributes to stable operation. In contrast, the positive bias stress induces positive shift in the threshold voltage, which increases linearly with increase in  $V_{\rm GB}$ . In addition, the  $V_{\rm TH}$  value at  $V_{\rm GB}=0$  for positive bias stress is close to that at  $V_{\rm GB}=0$  for the negative bias. Since the transfer characteristics for the positive bias stress were measured about one day after the measurement of the negative bias stress, the recovery of the  $V_{\rm TH}$  implies that storage under no operation extinguishes the effect of the bias stress. This means that the threshold voltage shift induced by the bias stress is a temporary effect. Since the  $V_{\rm TH}$  value at  $V_{\rm GB}=0$  for the positive bias stress is close to that at  $V_{\rm GB}=0$  for negative bias, the  $V_{\rm TH}$  value obtained after oxygen plasma treatment is more stable. In fact, it is confirmed that relative threshold voltage among different  $t_{\rm P}$  is maintained for more than one month at least. This is probably because the oxygen plasma treatment generates electron trapping sites at deep levels in the SiO<sub>2</sub> gate dielectric.

Figure 3.7: (a) Transfer characteristics of a pentacene TFT with  $L = 80 \,\mu\text{m}$  and 90-nm-thick SiO<sub>2</sub> plasma-treated at a AC power of 3.8 W for  $t_p = 60 \,\text{s}$  after bias stresses of  $V_{\text{GB}} = 0$  (black line),  $-10 \,\text{to} -50$ , and 10 to 50 V were applied to the TFT for  $t_{\text{S}} = 60 \,\text{s}$ . (b) Threshold voltages and (c) mobilities in the saturation regime of the TFT estimated from the drain current versus gate voltage characteristics in (a).

Point defects in SiO<sub>2</sub> have been experimentally and theoretically studied in the fields of electronics and optics [43-46]. Many types of point defects have been reported, including  $\equiv$ Si-Si $\equiv$ ,  $\equiv$ Si-H,  $\equiv$ Si-O-O-Si $\equiv$ ,  $\equiv$ Si-O-O•,  $\equiv$ Si-O•, and  $\equiv$ Si-O-H. Here, " $\equiv$ " and " $\equiv$ " denote, respectively, three and two network Si-O bonds, and "•" represents an unpaired electron. Perfect SiO<sub>2</sub> has a bandgap energy of about 9 eV [43] and the point defect generates an energy level within the bandgap. Pacchioni and Ierano have examined defect energy levels in SiO<sub>2</sub> [44]. Since oxygen plasma treatment was used for surface treatment in this study, we focus on O-

related defects. Figure 3.8 shows a schematic illustration of the defect energy levels for  $\equiv$ Si-O-O-Si $\equiv$ ,  $\equiv$ Si-O-O•,  $\equiv$ Si-O•, and  $\equiv$ Si-O-H. The energy level of the highest occupied molecular orbital (HOMO) of pentacene [47] is also shown. The  $\equiv$ Si-O-O• and  $\equiv$ Si-O• defects having an unpaired electron would act as electron traps, whereas the  $\equiv$ Si-O-H and  $\equiv$ Si-O-O-Si $\equiv$  defects would not [45]. It is possible that oxygen atoms incorporated into SiO<sub>2</sub> form  $\equiv$ Si-O-O-Si $\equiv$ ,  $\equiv$ Si-O-O•, and  $\equiv$ Si-O• defects [46]. In oxygen plasma treatment, oxygen ions accelerate to the surface of a substrate. Thus, oxygen plasma treatment would generate  $\equiv$ Si-O-O•, and  $\equiv$ Si-O• defects that act as electron traps. This is a conceivable reason why the oxygen plasma treatment induces threshold voltage change.

Figure 3.8: Schematic illustration of energy levels for various defects in SiO<sub>2</sub> and the HOMO level of pentacene.

#### 3.4 Summary

We investigated the effect of oxygen plasma treatment of the SiO<sub>2</sub> gate dielectric on the characteristics of pentacene TFTs. The plasma treatment for less than 120 s enables the control of the threshold voltage without a large change in the mobility. The threshold voltage shift, which is proportional to the treatment time, can be explained by supposing that the plasma treatment induces negative charges on and/or near to the gate dielectric surface. Also, we investigated the effect of gate bias stress on the TFT characteristics. The gate bias stress did not extinguish the threshold voltage change induced by plasma treatment. The threshold voltage shift in the TFT induced by gate bias stress was as small as about 2 V. The information on the threshold voltage shift and stability obtained in this study is useful for the application of organic TFTs to integrated circuits.

#### 3.5 References

- [1] P. F. Baude, D. A. Ender, M. A. Haase, T. W. Kelley, D. V. Muyres, and S. D. Theiss, Appl. Phys. Lett. 82, 3964 (2003).

- [2] D. Bode, K. Myny, B. Verreet, B. van der Putten, P. Bakalov, S. Steudel, S. Smout, P. Vicca, J. Genoe, and P. Heremans, Appl. Phys. Lett. 96, 133307 (2010).

- [3] M. Kitamura, Y. Kuzumoto, S. Aomori, and Y. Arakawa, Appl. Phys. Express 4, 051601 (2011).

- [4] K.-J. Baeg, S.-W. Jung, D. Khim, J. Kim, D.-Y. Kim, J. B. Koo, J. R. Quinn, A. Facchetti, I.-K. You, and Y.-Y. Noh, Org. Electron. 14, 1407 (2013).

- [5] P. Mach, S. J. Rodriguez, R. Nortrup, P. Wiltzius, and J. A. Rogers, Appl. Phys. Lett. 78, 3592 (2001).

- [6] C. D. Sheraw, L. Zhou, J. R. Huang, D. J. Gundlach, and T. N. Jackson, Appl. Phys. Lett. 80, 1088 (2002).

- [7] M. Kitamura, T. Imada, and Y. Arakawa, Jpn. J. Appl. Phys. 42, 2483 (2003).

- [8] L. Zhou, S. Park, B. Bai, J. Sun, S.-C. Wu, T. N. Jackson, S. Nelson, D. Freeman, and Y. Hong, IEEE Electron Device Lett. **26**, 640 (2005).

- [9] S. C. Lim, S. H. Kim, H. Y. Chu, J. H. Lee, J.-I. Lee, J. Y. Oh, D. Kim, and T. Zyung, Synth. Met. 151, 197 (2005).

- [10] G. H. Gelinck, H. E. A. Huitema, E. van Veenendaal, E. Cantatore, L. Schrijnemakers, J. B. P. H. van der Putten, T. C. T. Geuns, M. Beenhakkers, J. B. Giesbers, B.-H. Huisman, E. J. Meijer, E. M. Benito, F. J. Touwslager, A. W. Marsman, B. J. E. van Rens, and D. M. de Leeuw, Nat. Mater. 3, 106 (2004).

- [11] M. Kitamura and Y. Arakawa, Jpn. J. Appl. Phys. **50**, 01BC01 (2011).

- [12] L. Shang, Z. Ji, H. Wang, Y. Chen, C. Lu, X. Liu, M. Han, and M. Liu, IEEE Tran. Electron Devices 58, 2127 (2011).

- [13] R. Schroeder, L. A. Majewski, and M. Grell, Appl. Phys. Lett. 83, 3201 (2003).

- [14] M. Kitamura, Y. Kuzumoto, S. Aomori, M. Kamura, J. H. Na, and Y. Arakawa, Appl. Phys. Lett. 94, 083310 (2009).

- [15] S. Kobayashi, T. Nishikawa, T. Takenobu, S. Mori, T. Shimoda, T. Mitani, H. Shimotani, N. Yoshimoto, S. Ogawa, and Y. Iwasa, Nat. Mater. 3, 317 (2004).

- [16] K. P. Pernstich, S. Haas, D. Oberhoff, C. Goldmann, D. J. Gundlach, B. Batlogg, A. N. Rashid, and G. Schitter, J. Appl. Phys. 96, 6431 (2004).

- [17] S. C. Lim, S. H. Kim, J. H. Lee, M. K. Kim, D. J. Kim, and T. Zyung, Synth. Met. **148**, 75 (2005).

- [18] S. Iba, T. Sekitani, Y. Kato, T. Someya, H. Kawaguchi, M. Takamiya, T. Sakurai, and S. Takagi, Appl. Phys. Lett. **87**, 023509 (2005).

- [19] K. Hizu, T. Sekitani, T. Someya, and J. Otsuki, Appl. Phys. Lett. 90, 093504 (2007).

- [20] M. Kitamura, Y. Kuzumoto, M. Kamura, S. Aomori, J. H. Na, and Y. Arakawa, Phys. Status Solidi C 5, 3181 (2008).

- [21] Y. Ito, A. A. Virkar, S. Mannsfeld, J. H. Oh, M. Toney, J. Locklin, and Z. Bao, J. Am. Chem. Soc. 131, 9396 (2009).

- [22] M. W. Lee and C. K. Song, Jpn. J. Appl. Phys. 42, 4218 (2003).

- [23] A. Wang, I. Kymissis, V. Bulović, and A. I. Akinwande, IEEE Trans. Electron Devices **53**, 9 (2006).

- [24] K. Fukuda, T. Sekitani, U. Zschieschang, H. Klauk, K. Kuribara, T. Yokota, T. Sugino, K. Asaka, M. Ikeda, H. Kuwabara, T. Yamamoto, K. Takimiya, T. Fukushima, T. Aida, M. Takamiya, T. Sakurai, and T. Someya, Adv. Funct. Mater. 21, 4019 (2011).

- [25] A. Wang, I. Kymissis, V. Bulović, and A. I. Akinwande, Appl. Phys. Lett. 89, 112109 (2006).

- [26] D. Guo, S. Entani, S. Ikeda, and K. Saiki, Chem. Phys. Lett. 429, 124 (2006).

- [27] Y. Kimura, M. Kitamura, and Y. Arakawa, Ext. Abstr. Solid State Devices and Materials, 2014, p. 926.

- [28] S. J. Zilker, C. Detcheverry, E. Cantatore, and D. M. de Leeuw, Appl. Phys. Lett. **79**, 1124 (2001).

- [29] T. Sekitani, S. Iba, Y. Kato, Y. Noguchi, T. Someya, and T. Sakurai, Appl. Phys. Lett. 87, 073505 (2005).

- [30] J. B. Chang and V. Subramanian, Appl. Phys. Lett. 88, 233513 (2006).

- [31]D. K. Hwang, K. Lee, J. H. Kim, S. Im, J. H. Park, and E. Kim, Appl. Phys. Lett. **89**, 093507 (2006).

- [32] T. Umeda, D. Kumaki, and S. Tokito, Org. Electron. 9, 545 (2008).

- [33] K. Fukuda, T. Hamamoto, T. Yokota, T. Sekitani, U. Zschieschang, H. Klauk, and T. Someya, Appl. Phys. Lett. **95**, 203301 (2009).

- [34] U. Zschieschang, R. T. Weitz, K. Kern, and H. Klauk, Appl. Phys. A 95, 139 (2009).

- [35] D. Knipp, R. A. Street, A. Völkel, and J. Ho, J. Appl. Phys. 93, 347 (2003).

- [36] A. Salleo, F. Endicott, and R. A. Street, Appl. Phys. Lett. **86**, 263505 (2005).

- [37] M. J. Powell, Appl. Phys. Lett. 43, 597 (1983).

- [38] F. R. Libsch and J. Kanicki, Appl. Phys. Lett. **62**, 1286 (1993).

- [39] C.-H. Lee, D. Striakhilev, and A. Nathan, IEEE Tran. Electron Devices 54, 45 (2007).

- [40] J.-S. Park, K. Kim, Y.-G. Park, Y.-G. Mo, H. D. Kim, and J. K. Jeong, Adv. Mater. **21**, 329 (2009).

- [41] M. E. Lopes, H. L. Gomes, M. C. R. Medeiros, P. Barquinha, L. Pereira, E. Fortunato, R. Martins, and I. Ferreira, Appl. Phys. Lett. **95**, 063502 (2009).

- [42] J. S. Park, W.-J. Maeng, H.-S. Kim, and J.-S. Park, Thin Solid Films **520**, 1679 (2012).

- [43] T. H. DiStefano and D. E. Eastman, Solid State Commun. 9, 2259 (1971).

- [44] G. Pacchioni and G. Ierano, Phys. Rev. B 57, 818 (1998).

- [45] V. A. Gritsenko, A. V. Shaposhnikov, Yu. N. Novikov, A. P. Baraban, Hei Wong, G. M. Zhidomirov, and M. Roger, Microelectron. Reliab. 43, 665 (2003).

- [46] K. Kajihara, T. Miura, H. Kamioka, A. Aiba, M. Uramoto, Y. Morimoto, M. Hirano, L. Skuja, and H. Hosono, J. Non-Cryst. Solids **354**, 224 (2008).

- [47] S. J. Kang, Y. Yi, C. Y. Kim, S. W. Cho, M. Noh, K. Jeong, and C. N. Whang, Synth. Met. 156, 32 (2006).

# Chapter 4

# **Energy Distribution of Interface States Generated by Oxygen Plasma Treatment**

#### 4.1 Introduction

Organic thin-film transistors (TFTs) have attracted considerable attention because of their potential applications to large-area, mechanically flexible, light-weight, and cost-effective devices [1-3]. In addition to the advantage, field-effect mobilities in organic TFTs have reached to about 10 cm<sup>2</sup>/(V s) [5-8], Which is close to those of oxide TFTs practically used in flat panel displays. For practical application, threshold voltage control in organic TFTs is an important issue as well as improvement of the performance. Some groups have been attempting threshold voltage control in organic TFTs using various methods such as using self-assembled monolayers (SAM) on a gate dielectric [9-12], utilizing new polymer gate dielectrics [13,14], doping into organic layers [15-17], choosing gate metals [18,19], adjusting parasitic resistance [20,21], and using multi gate structures [22].

Another approach of threshold voltage control utilized oxygen plasma treatment to the surface of gate dielectrics [23-25]. Oxygen plasma treatment has been used to obtain a hydrophilic surface for formation of a SAM on a gate dielectric [26,27]. Thus, the threshold voltage control by oxygen plasma treatment does not require an additional process if the organic TFT requires a SAM layer. In addition, the threshold voltage gradually changes with plasma treatment time. The continuous change is suitable for application to integrated circuits of organic TFTs. In actual, we applied pentacene TFTs with the controlled threshold voltage to

logic circuits [28,29]. Since the threshold voltage shifts to positive gate voltage with plasma treatment time, the threshold voltage change in probably attributed to electrons captured at interface states generated by oxygen plasma treatment. Although a concern is that the change is temporary, we described that gate bias stress does not negate the threshold voltage change provided by oxygen plasma treatment in chapter 3. This implies that the interface states work as deep traps for electrons. On the other hand, the presence of shallow traps has been unclear.

For Si metal-oxide-semiconductor (MOS) field-effect transistors (FET), electron states at the interface between semiconductors and gate dielectric have been examined using some methods including electron spin resonance spectroscopy [30], current–voltage measurements [31], and capacitance–voltage (C–V) measurements [32,33]. Among the method, C–V measurement has an advantage that the measurement is performed without light irradiation and elevated temperature. Since organic TFTs are generally sensitive to light and temperature change, C–V measurement is suitable for evaluation of organic TFTs and MOS capacitors. In actual, interface traps in organic MOS capacitors have been investigated by C–V measurement [34-36].

In this chapter, we report C-V characteristics of pentacene MOS capacitors with a SiO<sub>2</sub> gate dielectric treated with oxygen plasma to examine the energy distribution of interface states generated by the treatment. First, we show current-voltage characteristics of pentacene TFTs to compare the characteristics of those of the MOS capacitors. Then, C-V characteristics of the MOS capacitors are shown. The energy distribution of the interface states is calculated from the C-V characteristics.

### 4.2 Analytical methods

#### 4.2.1 Characteristics of MOS capacitors

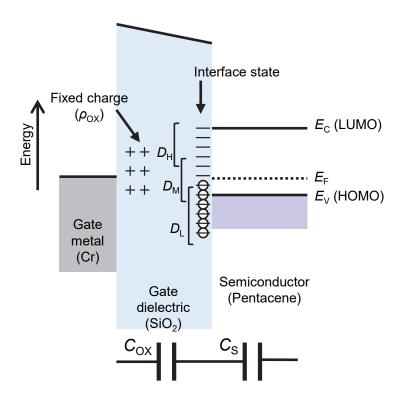

Figure 4.1 shows schematic band diagram of a SiO<sub>2</sub>/pentacene MOS capacitor examined in this study, we attempt to estimate the interface state density by C-V measurement. The total

capacitance per unit area of MOS capacitor ( $C_G$ ) is expressed as

$$\frac{1}{C_{\rm G}} = \frac{1}{C_{\rm OX}} + \frac{1}{C_{\rm S}},\tag{4.1}$$

where  $C_S$  is the capacitance per unit area of the pentacene layer. The capacitances  $C_G$  and  $C_S$  are functions of the gate voltage  $(V_G)$  and are represented as  $C_G(V_G)$  and  $C_S(V_G)$ . The interface state density in experimentally classified into three groups denoted as  $D_L$ ,  $D_M$ , and  $D_H$  are expected to be roughly distributed in ascending order shown in Fig. 4.1. Because the fixed charge in the gate dielectric is expect to be positive, it is represented by a plus sign.

Flat band voltage ( $V_{\text{FB}}$ ) of a MOS capacitor without inversion mode is equal to threshold voltage ( $V_{\text{TH}}$ ) of a transistor as described in chapter 2, and is written as

$$V_{\rm FB} = \frac{\Phi_{\rm M} - \Phi_{\rm S}}{e} - \frac{Q}{C_{\rm OV}},\tag{4.2}$$

where e is the electron elementary charge,  $\Phi_{\rm M}$  and  $\Phi_{\rm S}$  are the work functions of the gate electrode and the organic semiconductor, respectively. When a  $V_{\rm FB}$  value is experimentally obtained, Q is calculated from Eq. (4.2) as well as the charge density Q in Eq. (2.5). Also, the  $V_{\rm FB}$  value is used in an equation for surface potential shown below. An issue is how to determine  $V_{\rm FB}$  experimentally. In this study, the  $V_{\rm FB}$  value is experimentally determined as

$$C_{\rm S}(V_{\rm FB}) = 20\,\mathrm{min}\left[C_{\rm S}(V_{\rm G})\right].\tag{4.3}$$

Although this definition is not standard, Eq. (4.3) for a MOS capacitor provides a  $V_{\rm FB}$  value close to a  $V_{\rm TH}$  value obtained from the current characteristics of a TFT prepared under the same condition as that of the MOS capacitor. Physically, Eq. (4.3) means that one twentieth thickness of a pentacene layer acts as insulator. In this study, the average thickness of a pentacene is about 22.5 nm as explained later. Thus, the one twentieth thickness is about 1.1 nm.

#### 4.2.2 Interface states of MOS capacitors

The interface state density  $D_{it}$  in an evaluated MOS capacitor is generally obtained as a function of the surface potential at the interface between the semiconductor and the gate dielectric. The surface potential  $\Psi_{S}$  is expressed as [37,38]

$$\Psi_{\rm S}(V_{\rm G}) = V_{\rm G} - V_{\rm FB} - \int_{V_{\rm FB}}^{V_{\rm G}} \left(\frac{C_{\rm G}(V)}{C_{\rm OX}}\right) dV \tag{4.4}$$

as a function of  $V_G$  and is constructed by using  $V_{FB}$  and  $C_G(V_G)$ . The calculation of  $D_{it}$  requires the C-V characteristic of a MOS capacitor, which ideally has no interface state, as a reference. Here, the surface potential and the total capacitance of the reference MOS capacitor are denoted as  $\Psi_{ref}(V_G)$  and  $C_{ref}(V_G)$ , respectively. Using these notations, the interface state density  $(D_{it})$  can be calculated from

$$D_{it}\left(\Psi_{S}(V_{G})\right) = \lim_{\Delta V_{G} \to 0} \frac{1}{e^{2}} \frac{\Delta Q_{G} - \Delta Q_{ref}}{\Psi_{S}(V_{G} + \Delta V_{G}) - \Psi_{S}(V_{G})}$$

(4.5)

where

$$\Delta Q_{\rm G} = \int_{V_{\rm G}}^{V_{\rm G} + \Delta V_{\rm G}} C_{\rm G}(V) dV \tag{4.6a}$$

$$\Delta Q_{\text{ref}} = \int_{V_{G'}}^{V_{G'} + \Delta V_{G'}} C_{\text{ref}} (V) dV \tag{4.6b}$$

The  $V_{G}$  and  $\Delta V_{G}$  are defined as the following equations:

$$\Psi_{\text{ref}}\left(V_{\text{G}}'\right) = \Psi_{\text{S}}\left(V_{\text{G}}\right),\tag{4.7a}$$

$$\Psi_{\text{ref}}\left(V_{\text{G}}' + \Delta V_{\text{G}}'\right) = \Psi_{\text{S}}\left(V_{\text{G}} + \Delta V_{\text{G}}'\right). \tag{4.7b}$$

The  $\Delta Q_G$  and  $\Delta Q_{ref}$  are charges stored in the evaluated and reference MOS capacitors, respectively, when the surface potential changes from  $\Psi_S(V_G)$  to  $\Psi_S(V_G+\Delta V_G)$ .

Equation (4.5) is mathematically equivalent to

$$D_{\rm it}(\Psi_{\rm S}) = \frac{C_{\rm ox}}{e^2} \frac{d(V_{\rm G} - V_{\rm G}')}{d\Psi}$$

(4.8)

known as Terman method [38-40]. A calculated  $D_{it}$  value generally contains numerical errors. Thus, a value calculated from Eq. (4.5) may be slightly different from that calculated fro Eq. (4.8). In this study, we use Eq. (4.5) for calculation of  $D_{it}$ . This is because the increases in accumulated charges  $\Delta Q_{G}$ ,  $\Delta Q_{ref}$  can be seen in the calculation process.

Figure 4.1: Schematic band diagram of Cr/SiO<sub>2</sub>/pentacene structure.

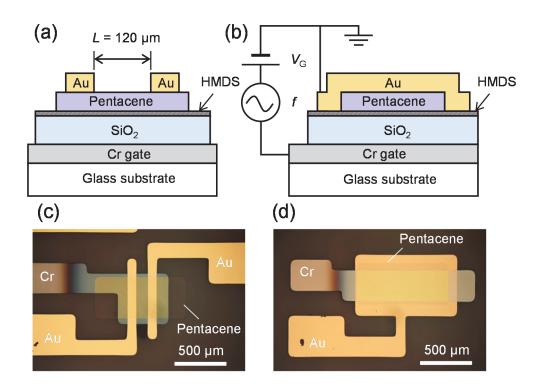

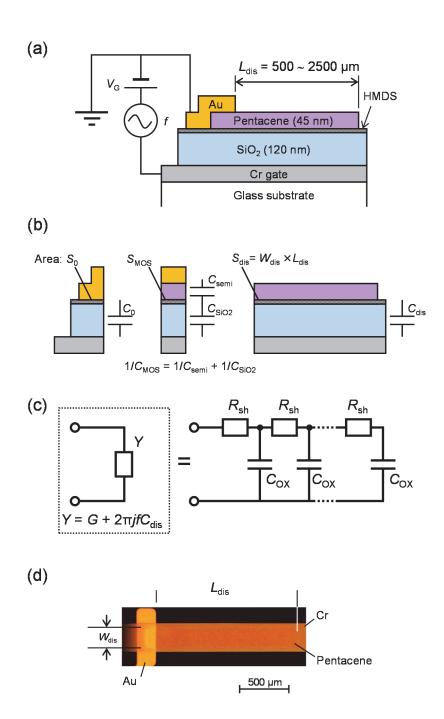

#### 4.3 Experimental methods

Figures 4.2(a) and 4.2(b) show cross sections of a pentacene TFT and a MOS capacitor, respectively. TFTs and MOS capacitors were fabricated on glass substrates, Corning (R) EAGLE XG. Each layer for the TFT and capacitor was deposited through a metal mask. First, a 20-nm-thick Cr layer was deposited as a gate electrode. Then, a  $SiO_2$  layer was deposited as a gate dielectric by rf sputtering. The  $SiO_2$  layer has a thickness of about 120 nm and a capacitance per unit area ( $C_{OX}$ ) of about 27 nF/cm<sup>2</sup>. The  $C_{OX}$  values determined from C-V

measurement are shown in Table 4.1. The substrates were cleaned with acetone, isopropanol, and UV ozone. Then, the SiO<sub>2</sub> surfaces were exposed to oxygen plasma for a time ( $t_p$ ) of 10 to 30 s under a condition of an O<sub>2</sub> flow rate of 100 mL/min and an AC power for plasma generation of 9.2 W. After oxygen plasma treatment, or UV ozone treatment as a reference without oxygen plasma treatment, the substrates were immediately exposed to hexamethyldisilazane (HMDS) vapor for 30 min at 120 °C. The TFT without oxygen plasma treatment is represented as  $t_p = 0$  s afterhere. A 45-nm-thick pentacene layer was deposited at a rate of 0.2 Å/s on the substrate of room temperature. Finally, a 45-nm-thick Au layer was thermally deposited as the top electrode of MOS capacitors and as the drain/source electrodes of TFTs. For TFTs, the channel width (W) is 400 µm and the channel length (L) is 120 µm. For MOS capacitors, the MOS capacitor area of Au/pentacene/SiO<sub>2</sub>/Cr structure is 2.7 × 10<sup>-3</sup> cm<sup>2</sup>. The MOS capacitor has an area of Au/SiO<sub>2</sub>/Cr structure, which is 0.3 × 10<sup>-3</sup> cm<sup>2</sup>. Capacitance values excluding the capacitance of the Au/SiO<sub>2</sub>/Cr area are shown as then capacitance of a MOS capacitor.

All characteristics were examined in a dry-nitrogen filled glovebox at room temperature. The current–voltage characteristics of TFTs were measured by using a semiconductor parameter analyzer, Agilent Technologies, B1500A. The capacitance characteristics of MOS capacitors were measured by using a source/measurement unit, Keysight Technologies, B2912A. A 100-mVrms AC voltage of a frequency of 200 Hz superimposed on a DC voltage ( $V_G$ ) was applied to the Cr electrode with respect to the Au electrode as seen in Fig. 4.2(b).

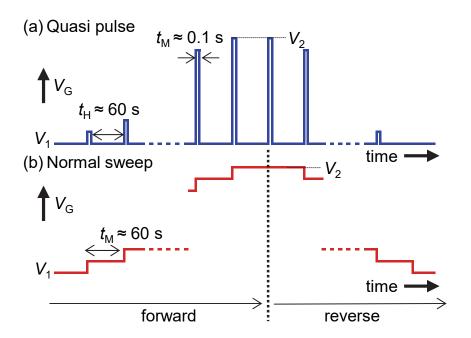

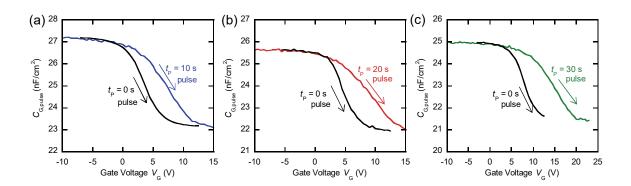

For MOS capacitors, the C-V measurement was performed in the range of  $V_G = V_1$  to  $V_2$  where  $V_1 = -10$  V,  $V_2 = 10$ , 15, 18, and 23 V for  $t_p = 0$ , 10, 20, and 30 s, respectively. To change the number of charges trapped in the interface states at a certain  $V_G$ , we adopted two time-profiles of applied  $V_G$  shown in Figs. 4.3(a) and 4.3(b). One is a quasi-pulse wave and the other is a normal sweep. The holding voltage in the quasi-pulse wave, which was set at -10 V, contributes to suppression of unintended charge transfer under a certain  $V_G$ .

Figure 4.2: Cross sections of a pentacene (a) TFT and (b) MOS capacitor. Microphotographs of a fabricated (c) TFT and (d) MOS capacitor.

Figure 4.3: Measuring methods of capacitance-voltage characteristics of MOS capacitors in this study. Two time-profiles of applied gate voltage: (a) a quasi-pulse wave and (b) a normal sweep.

#### 4.4 Results and discussion

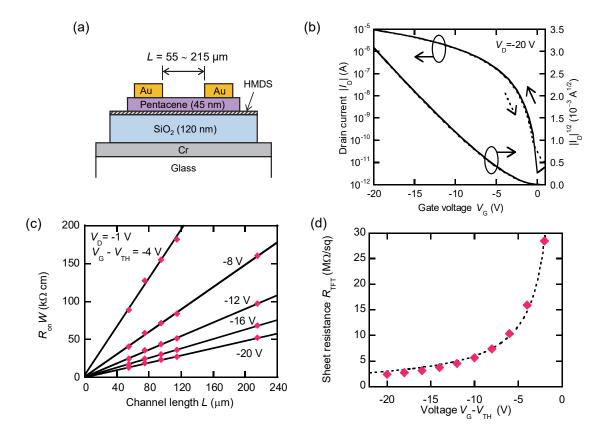

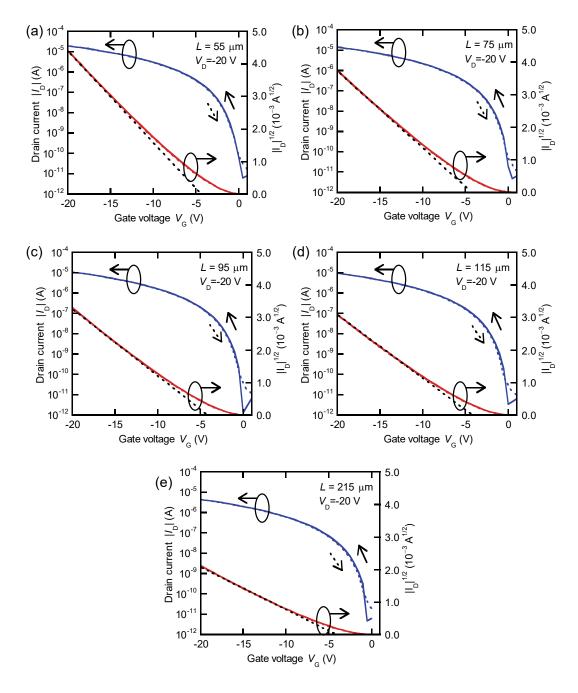

#### 4.4.1 Transistor characteristics

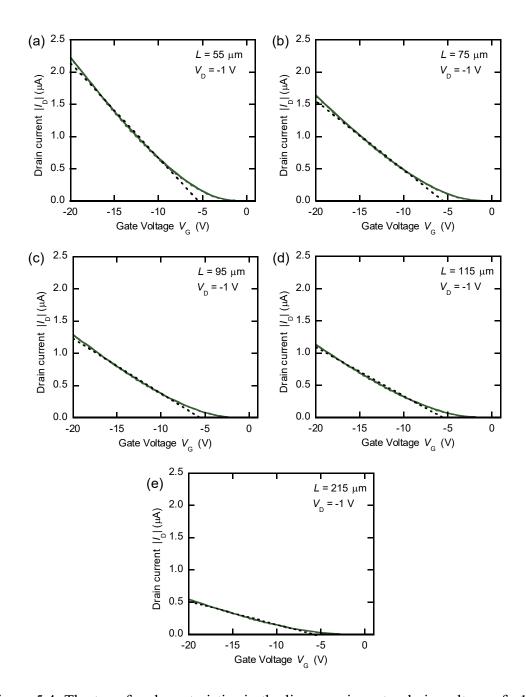

Figure 4.4(a) shows the drain current ( $I_D$ ) versus gate voltage ( $V_G$ ) characteristics of pentacene TFTs in the saturation regime at a drain voltage ( $V_D$ ) of -20 V. The  $I_D-V_G$  characteristics were obtained by the forward sweep from a positive  $V_G$  to -20 V, and the reverse sweep from -20 V to the positive  $V_G$ . The plasma treatment time  $t_P$  is 0, 10, 20, and 30 s. The  $I_D-V_G$  curves shift to positive gate voltages with increase in  $t_P$ . For  $|I_D| > 10^{-10}$  A, the  $I_D-V_G$  curves do not exhibit large hysteresis in the forward of positive to negative  $V_G$  and reverse of negative and positive  $V_G$  sweeps. For  $|I_D| < 10^{-10}$  A, a small hysteresis appears in the sweep. This hysteresis may relate to shallow traps shown as  $D_M$  and/or  $D_H$  in Fig. 4.1.

The field-effect mobilities in the saturation regime ( $\mu_{sat}$ ),  $V_{TH}$ , and sub-threshold swing (S) are summarized in Table 4.1. The  $\mu_{sat}$  and  $V_{TH}$  are calculated by fitting a line to  $|I_D|^{1/2} - V_G$  plots. The  $C_{OX}$  value shown in Table 4.2 is used for the calculation of  $\mu_{sat}$ , being obtained from C-V measurement.  $\mu_{sat}$  is in the range of 0.78 to 0.86 cm<sup>2</sup>/(V s), and does not largely depend on  $t_P$ . In Fig. 4.4(b),  $V_{TH}$  is plotted with respect to  $t_P$ . By assuming values of  $\Phi_M$  and  $\Phi_S$ , Q in Eq. (2.5) can be calculated as a function of  $t_P$ . We used  $\Phi_M = 4.8$  eV and  $\Phi_S = 4.5$  eV for the calculation. Although Cr was used for the gate metal, the surface of Cr is easily oxidized in general. Thus, we adopted the work function reported for  $Cr_2O_3$  as  $\Phi_M$  [41]. The  $\Phi_S$  value corresponds to the Fermi energy of pentacene [42].

Figure 4.4(c) shows the charge density  $Q_{\rm TFT}$  calculated from Eq. (2.5). From the fitting curve,  $Q_0$  and  $q_{\rm P}$  are estimated to be 118.8 nC/cm<sup>2</sup> and -5.24 nC/(cm<sup>2</sup> s). By assuming that positive charges are uniformly distributed in SiO<sub>2</sub>,  $\rho_0$  is calculated as  $2.0 \times 10^{-2}$  C/cm<sup>3</sup> which corresponds to positive charges of  $1.2 \times 10^{17}$  /cm<sup>3</sup>. The negative  $q_{\rm P}$  value suggests that oxygen plasma treatment generates interface states serving as electron traps. The surface charge density  $Q_{\rm S,TFT}$  (=  $q_{\rm P}$   $t_{\rm P}$ ) is shown in Table 4.1.

Figure 4.4: (a) Drain current versus gate voltage characteristics measured drain voltage  $V_D = -20 \text{ V}$  for pentacene TFTs with SiO<sub>2</sub> gate dielectric treated by oxygen plasma for  $t_p = 0$ , 10, 20, and 30 s. (b) Threshold voltage estimated from the transfer characteristics of pentacene TFTs. (c) Charge density  $Q_{\text{TFT}}$  calculated from the threshold voltage in (b).

Table 4.1: Electrical properties of pentacene TFTs with SiO<sub>2</sub> treated by oxygen plasma for  $t_p = 0$ , 10, 20, and 30 s: mobility in the saturation regime  $\mu_{\text{sat}}$ , threshold voltage  $V_{\text{TH}}$ , sub-threshold swing S, and surface charge density  $Q_{\text{S,TFT}} (= q_p t_p)$ .

| <i>t</i> <sub>p</sub> (s) | $\mu_{\rm sat}$ (cm <sup>2</sup> /(V s)) | $V_{\mathrm{TH}}\left(\mathrm{V}\right)$ | S (V/decade) | $Q_{S,TFT}$ (nF/cm <sup>2</sup> ) |

|---------------------------|------------------------------------------|------------------------------------------|--------------|-----------------------------------|

| 0                         | 0.85                                     | -4.11                                    | 0.61         | _                                 |

| 10                        | 0.86                                     | -1.90                                    | 0.70         | -59.0                             |

| 20                        | 0.83                                     | -0.99                                    | 0.72         | -85.8                             |

| 30                        | 0.78                                     | 2.25                                     | 1.00         | -168                              |

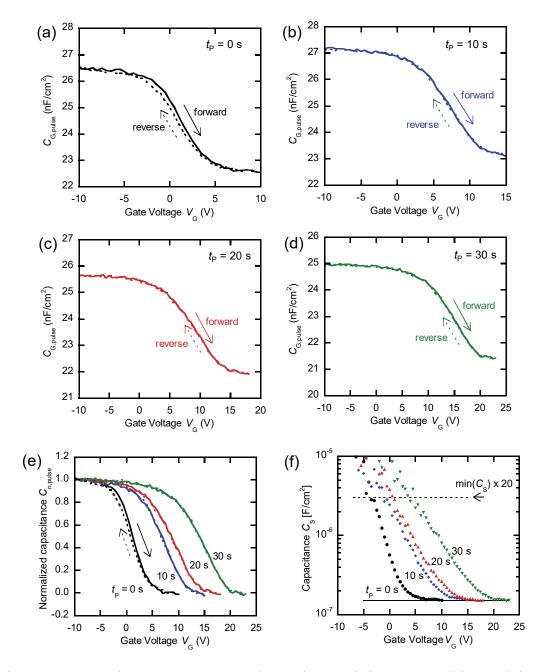

#### 4.3.2 MOS capacitor characteristics

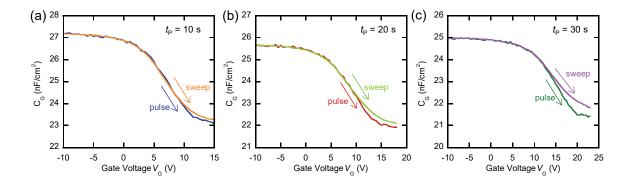

Figures 4.5(a)–4.5(d) show the capacitance measured by quasi-pulse wave shown in Fig. 4.3(a),  $C_{G,pulse}$ , versus  $V_G$  characteristics of pentacene MOS capacitors for  $t_p = 0$ , 10, 20, and 30 s. Properties extracted from the  $C_{G,pulse}$  characteristics are summarized in Table 4.2. For  $t_p = 10$ , 20, and 30 s, the C-V characteristics do not exhibit hysteresis in the forward and reverse measurement. This suggests that electrons trapped at the interface states by applying  $V_G > -10$  V leave from the states when applying  $V_G = -10$  V for a holding time of about 60 s. On the other hand, the C-V characteristic for  $t_p = 0$  s exhibits a small hysteresis. The  $C_{G,pulse}$  in the reverse measurement is slightly lower than that in the forward measurement. This may be due to presence of hole traps at the interface without oxygen plasma treatment.

The maximum and minimum values of  $C_G$  depend on the SiO<sub>2</sub> thickness. Although the SiO<sub>2</sub> layers were deposited under the same condition, unintentional difference in conditions leads to the difference in the SiO<sub>2</sub> thickness. For comparison of the C-V characteristics, we calculated a normalized capacitance  $C_n$  defined as

$$C_{\rm n} = \frac{C_{\rm G}(V_{\rm G}) - \min[C_{\rm G}(V_{\rm G})]}{\max[C_{\rm G}(V_{\rm G})] - \min[C_{\rm G}(V_{\rm G})]}.$$

(4.9)

Figure 4.5(e) shows  $C_{n,pulse}$  versus  $V_G$  of pentacene MOS capacitors for  $t_p = 0$ , 10, 20, and 30 s. The C-V curves shift to positive gate voltage with an increase in  $t_p$ .

The  $V_{\rm FB}$  values were calculated based on Eq. (4.3). Figure 4.5(f) shows the  $C_{\rm S}$  values calculated by substituting  $C_{\rm G,pulse}$  values into Eq. (4.1). The  $C_{\rm S}$  decreases with an increase in  $V_{\rm G}$ , and approaches 1.55, 1.58, 1.53, and 1.53 × 10<sup>-7</sup> F/cm<sup>2</sup> for  $t_{\rm P}$  = 0, 10, 20, and 30 s, respectively. The  $V_{\rm FB}$  value, which equals  $V_{\rm G}$  that satisfies  $C_{\rm S} \approx 3.1 \times 10^{-6}$  F/cm<sup>2</sup>, are estimated to be -3.57, -0.77, 0.64, and 3.61 V for  $t_{\rm P}$  = 0, 10, 20, and 30 s, respectively. For each  $t_{\rm P}$ , this value is close to the  $V_{\rm TH}$  value shown in Table 4.1. The  $V_{\rm FB}$  as well as  $V_{\rm TH}$  can be used for estimation of Q,  $Q_0$ , and  $Q_{\rm P}$ .  $Q_0$  and  $Q_{\rm P}$  are estimated to be 98.7 nC/cm<sup>2</sup> and -5.92 cm<sup>2</sup>/(cm<sup>2</sup> s), which are not far

from those estimated from  $V_{\rm TH}$ . Electrons that cause  $Q_{\rm S}$  (=  $q_{\rm P}$   $t_{\rm P}$ ) probably capture at interface states. We classify the interface state density into  $D_{\rm L}$ . This is because  $Q_{\rm S}$  does not cause hysteresis in the transfer characteristics of pentacene TFTs. This indicates that  $D_{\rm L}$  work as deep traps. Thus,  $D_{\rm L}$  corresponds to low energy levels as shown in Fig. 4.1. In other words,  $Q_{\rm S}$  is expressed as

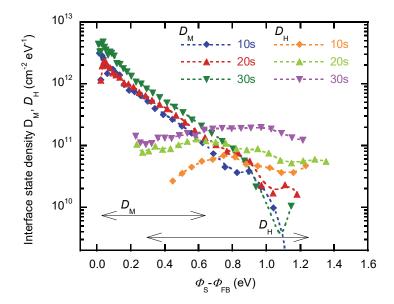

$$Q_{\rm S} = e \int D_{\rm L} dE \,. \tag{4.10}$$